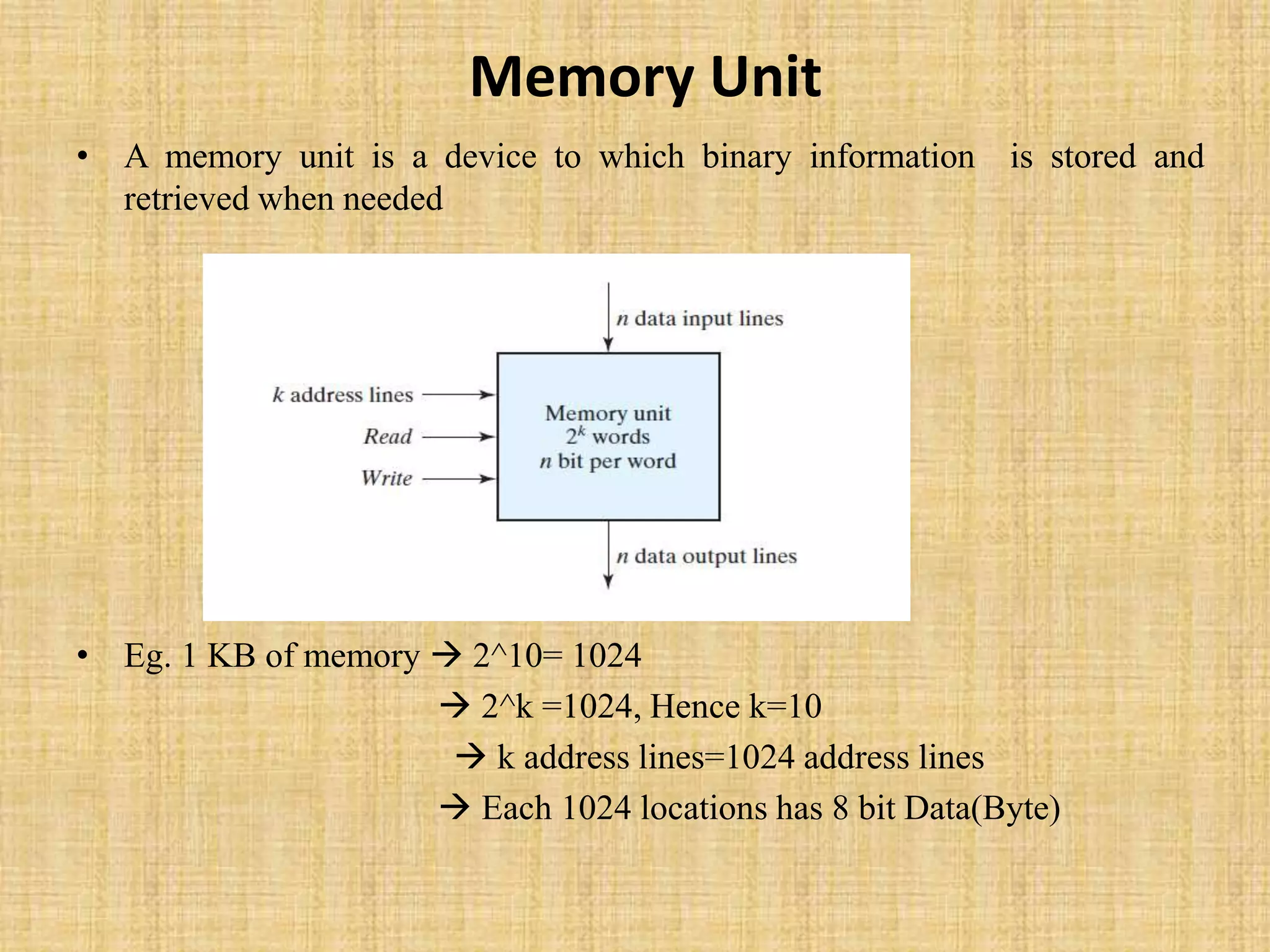

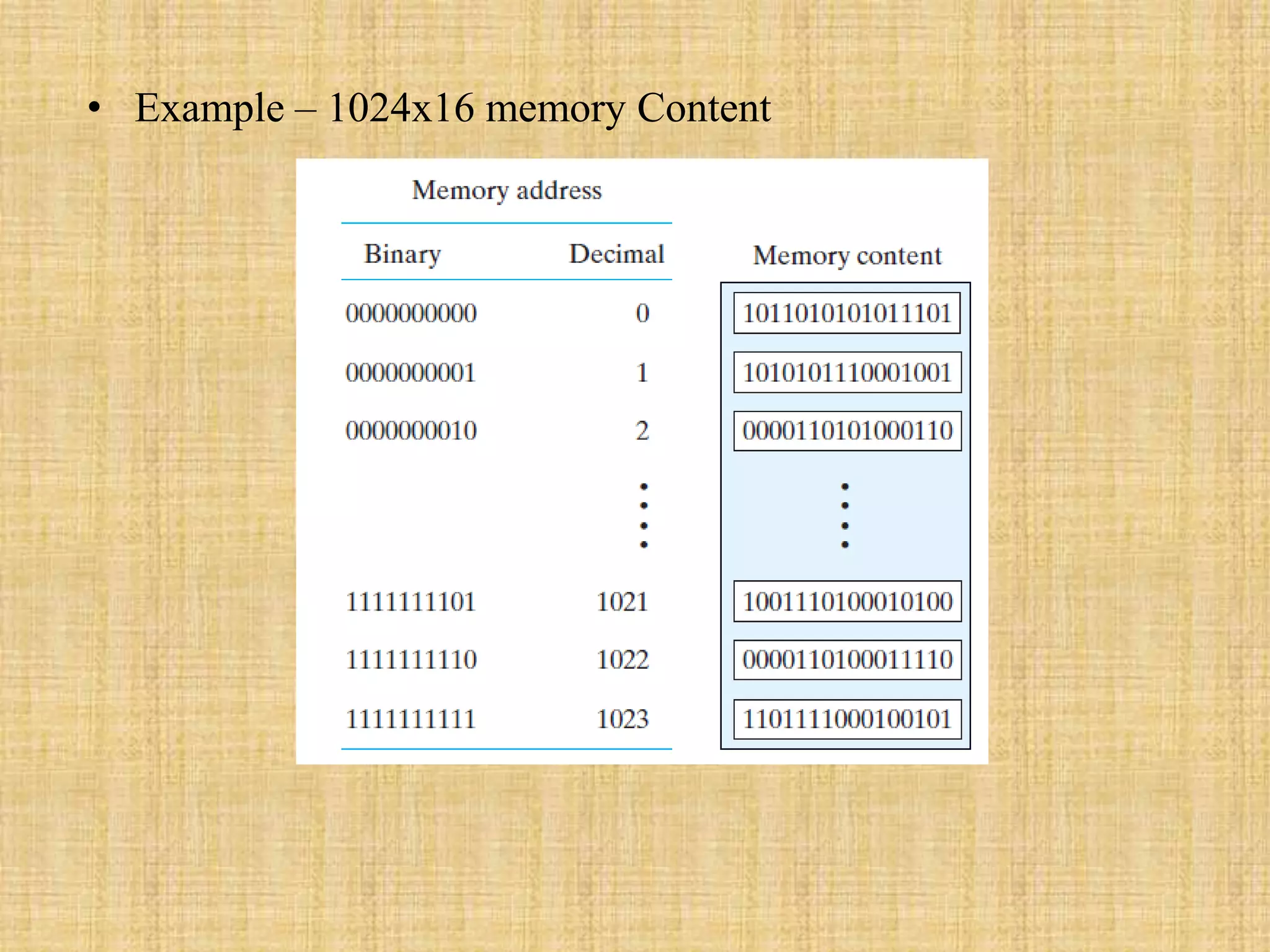

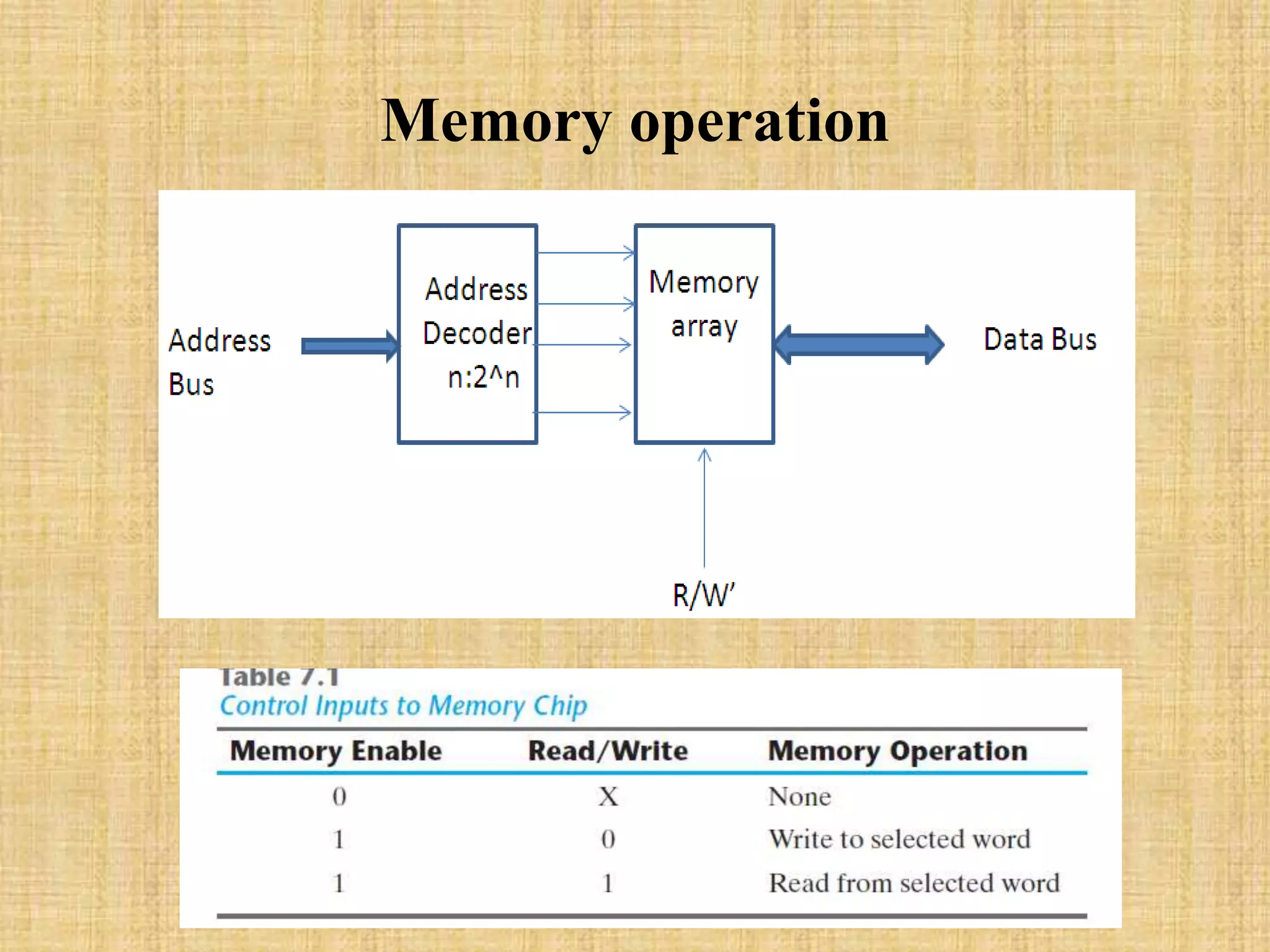

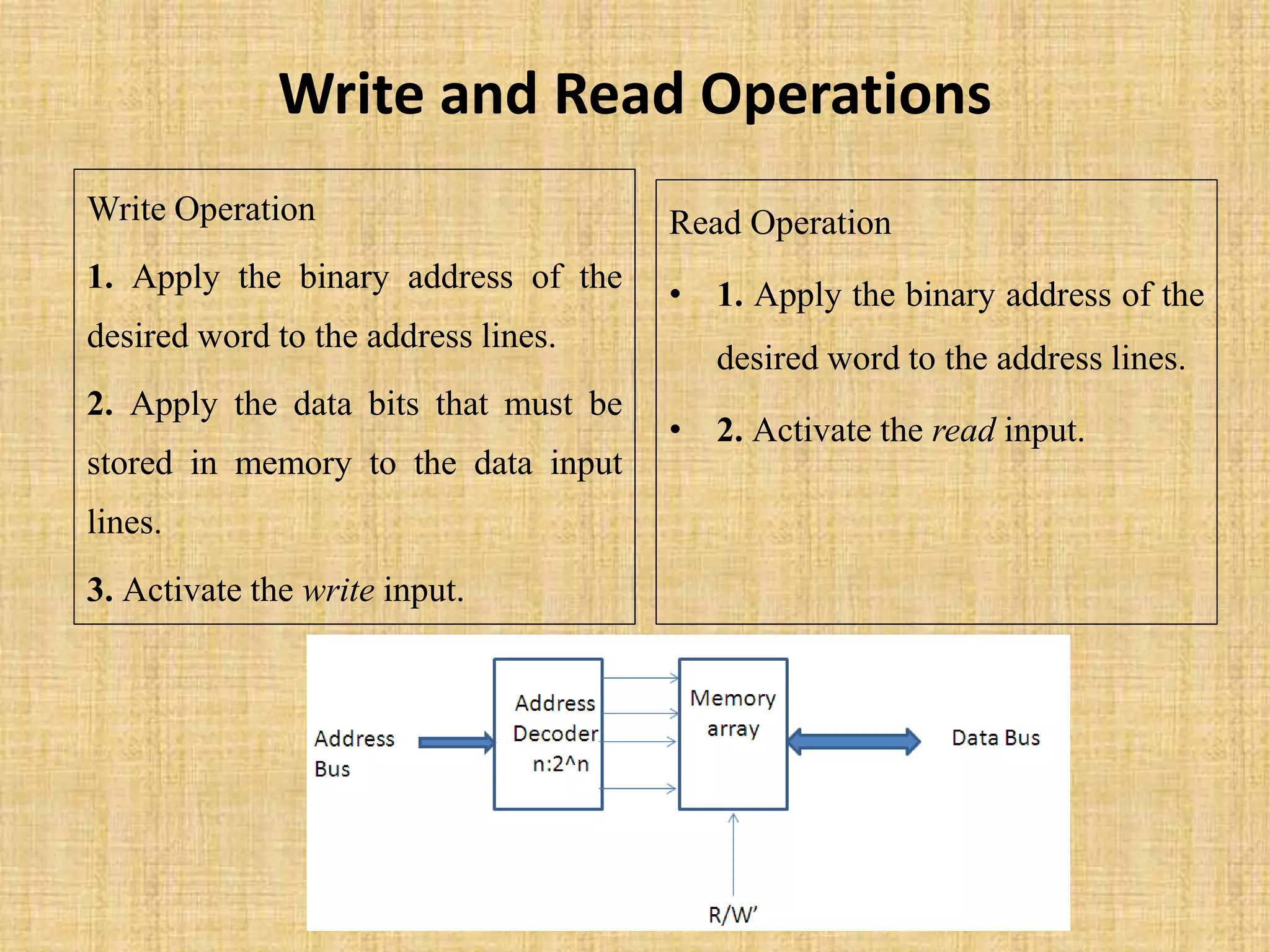

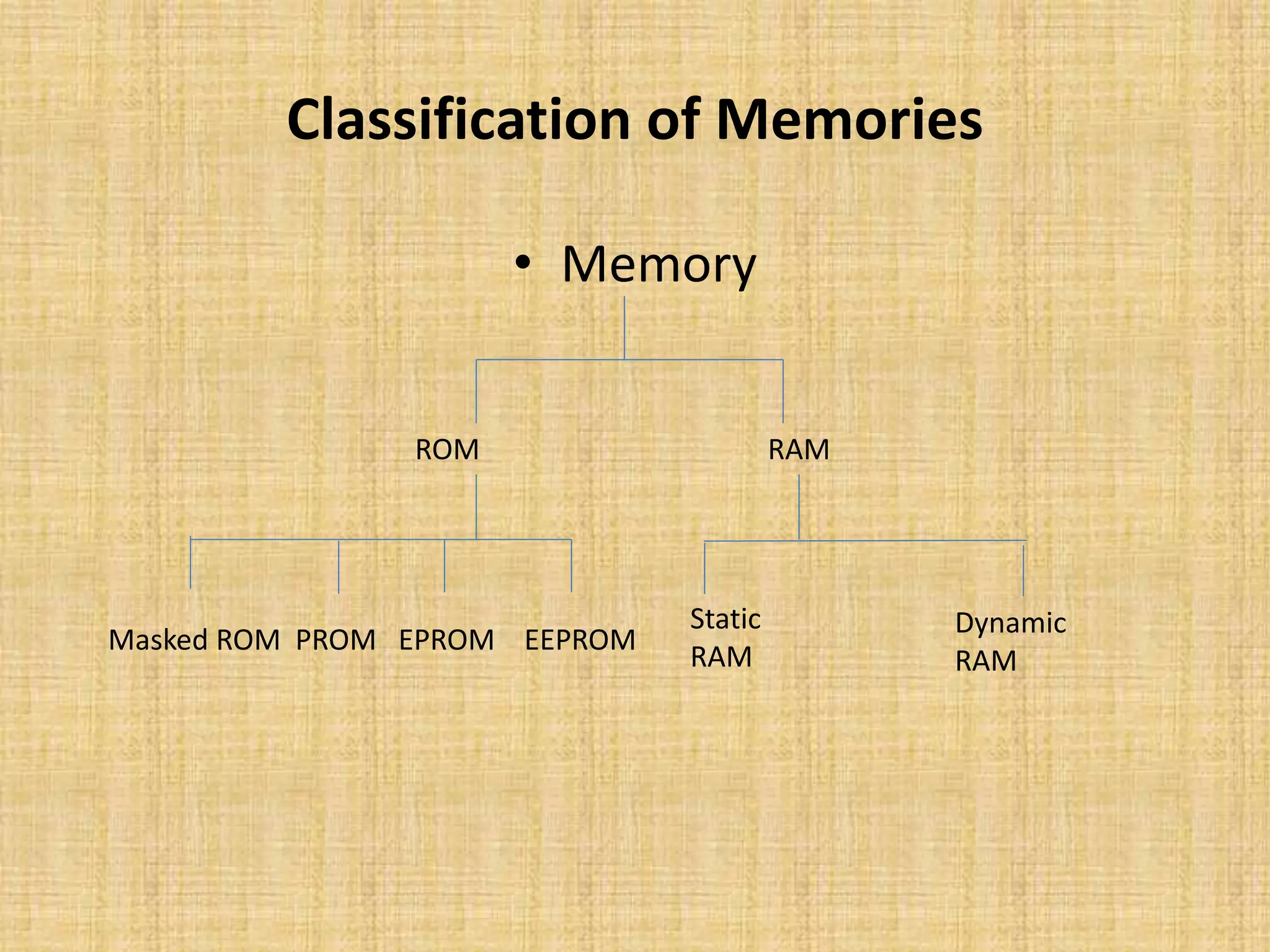

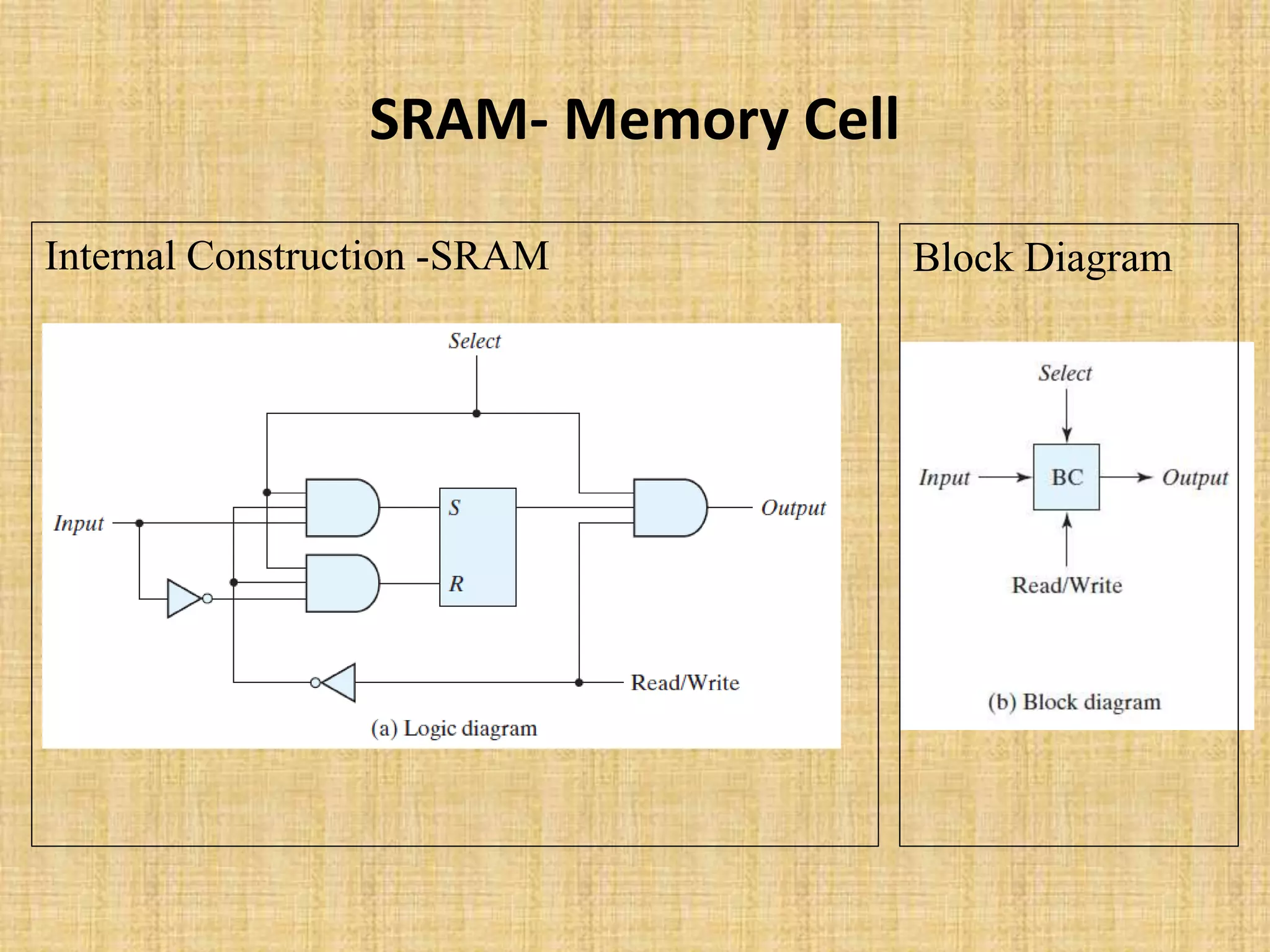

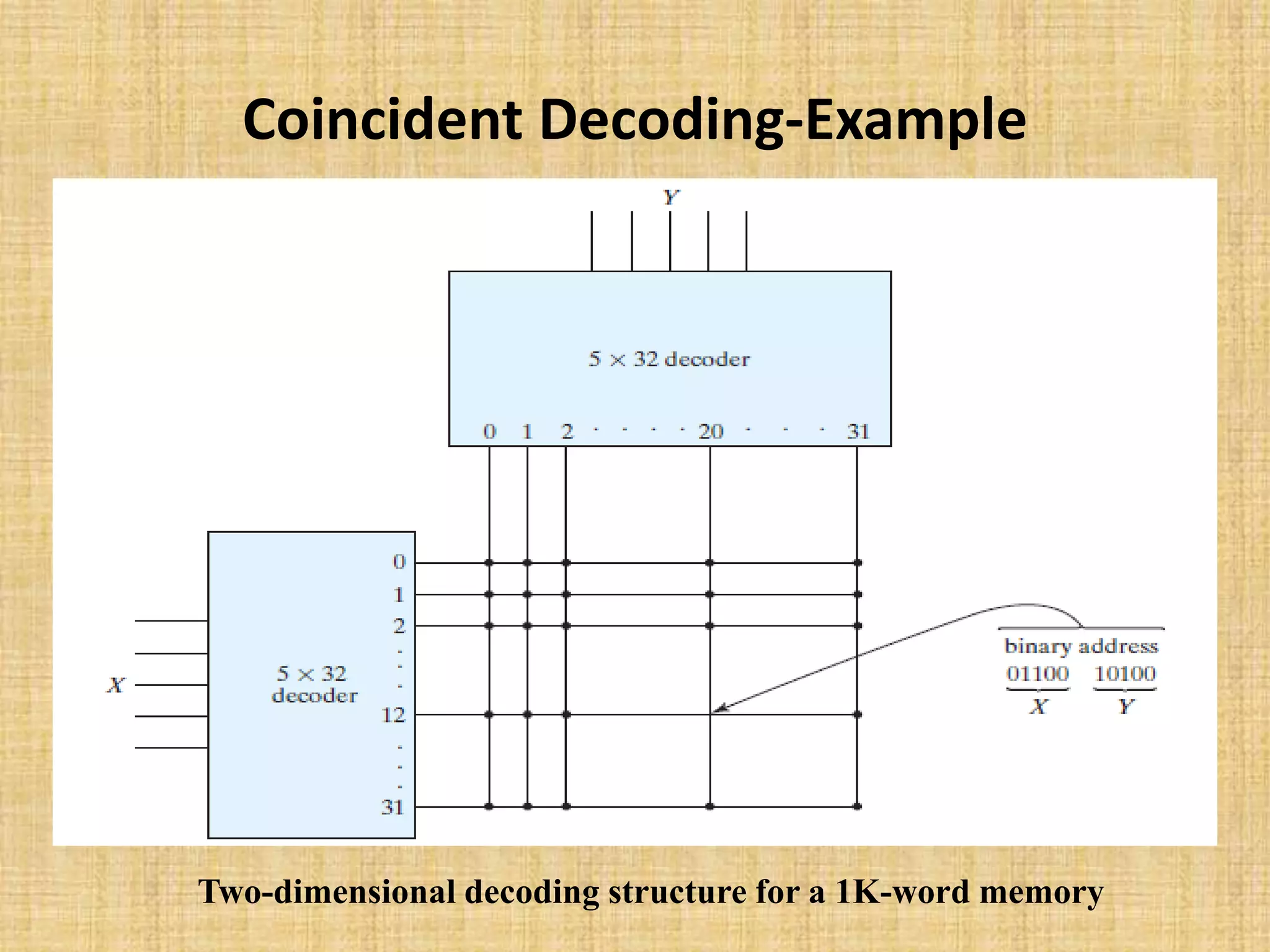

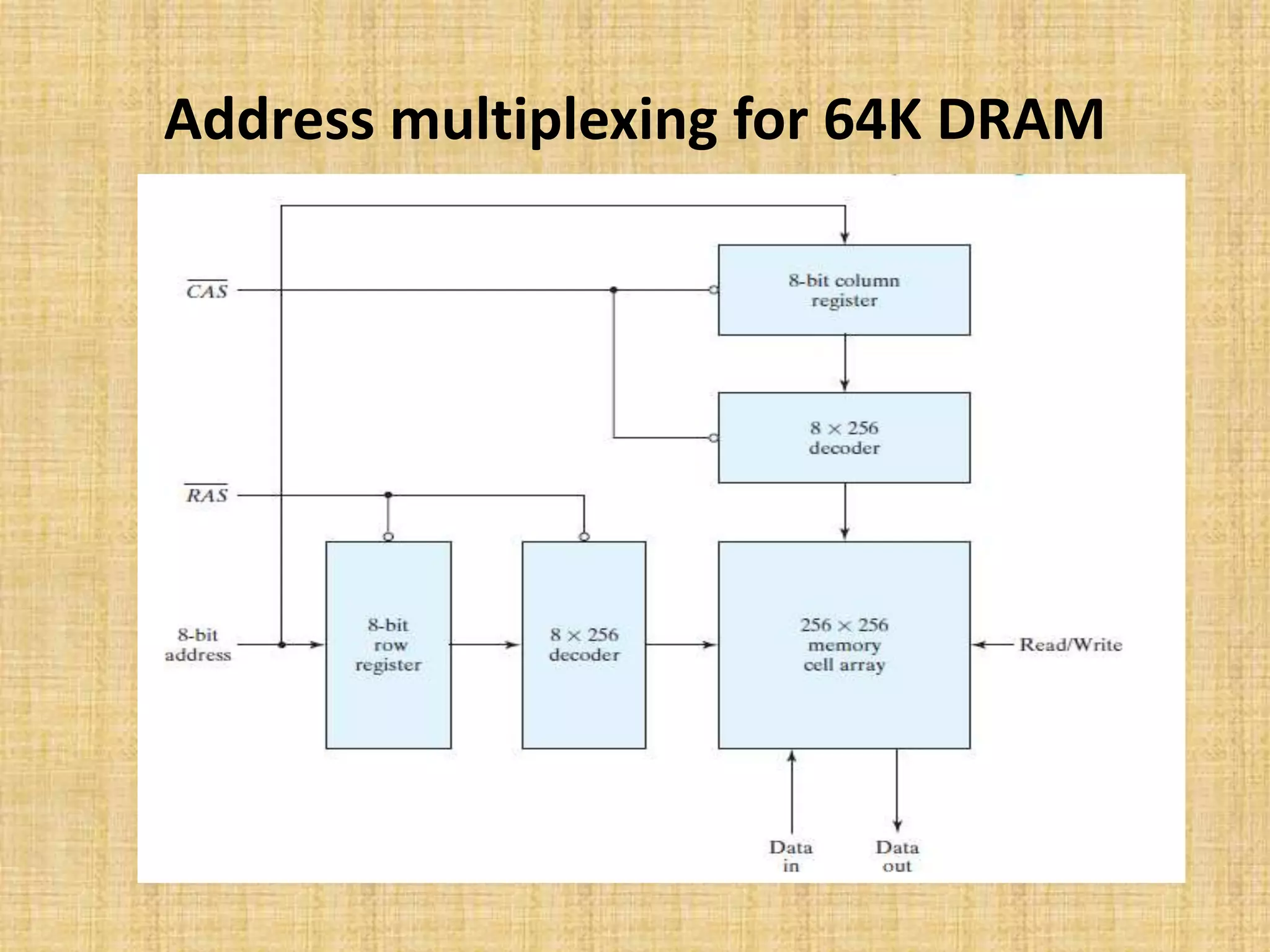

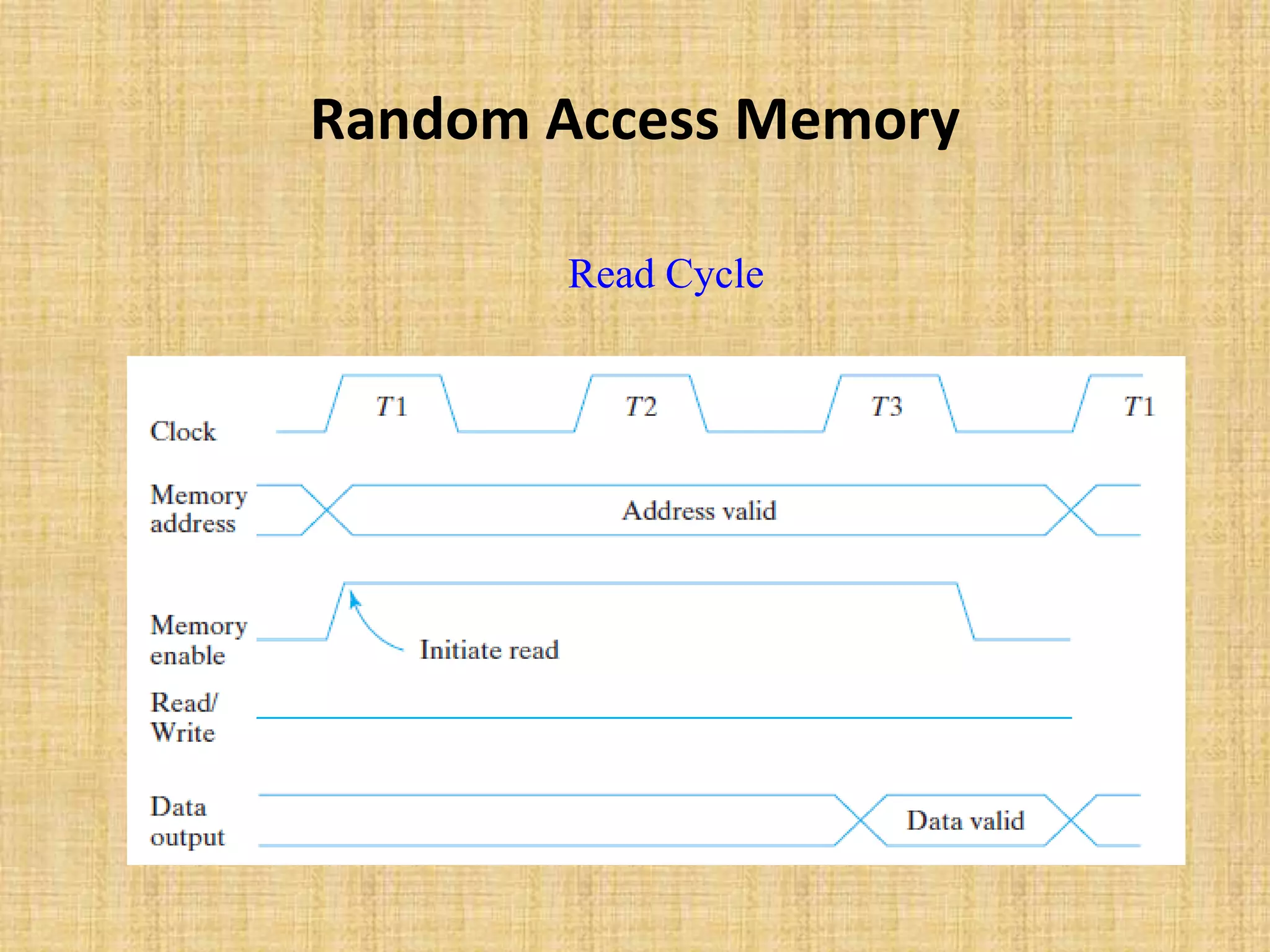

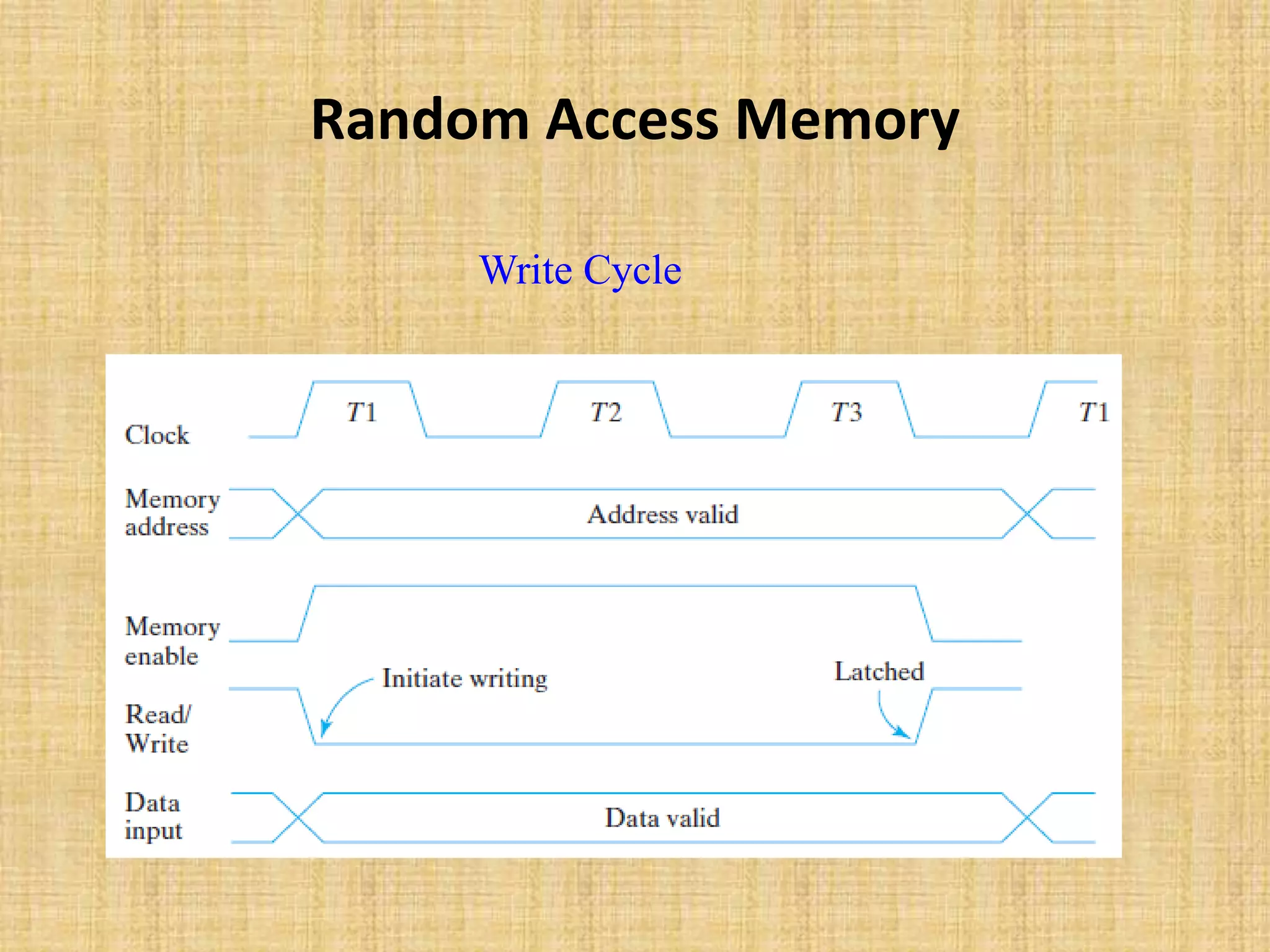

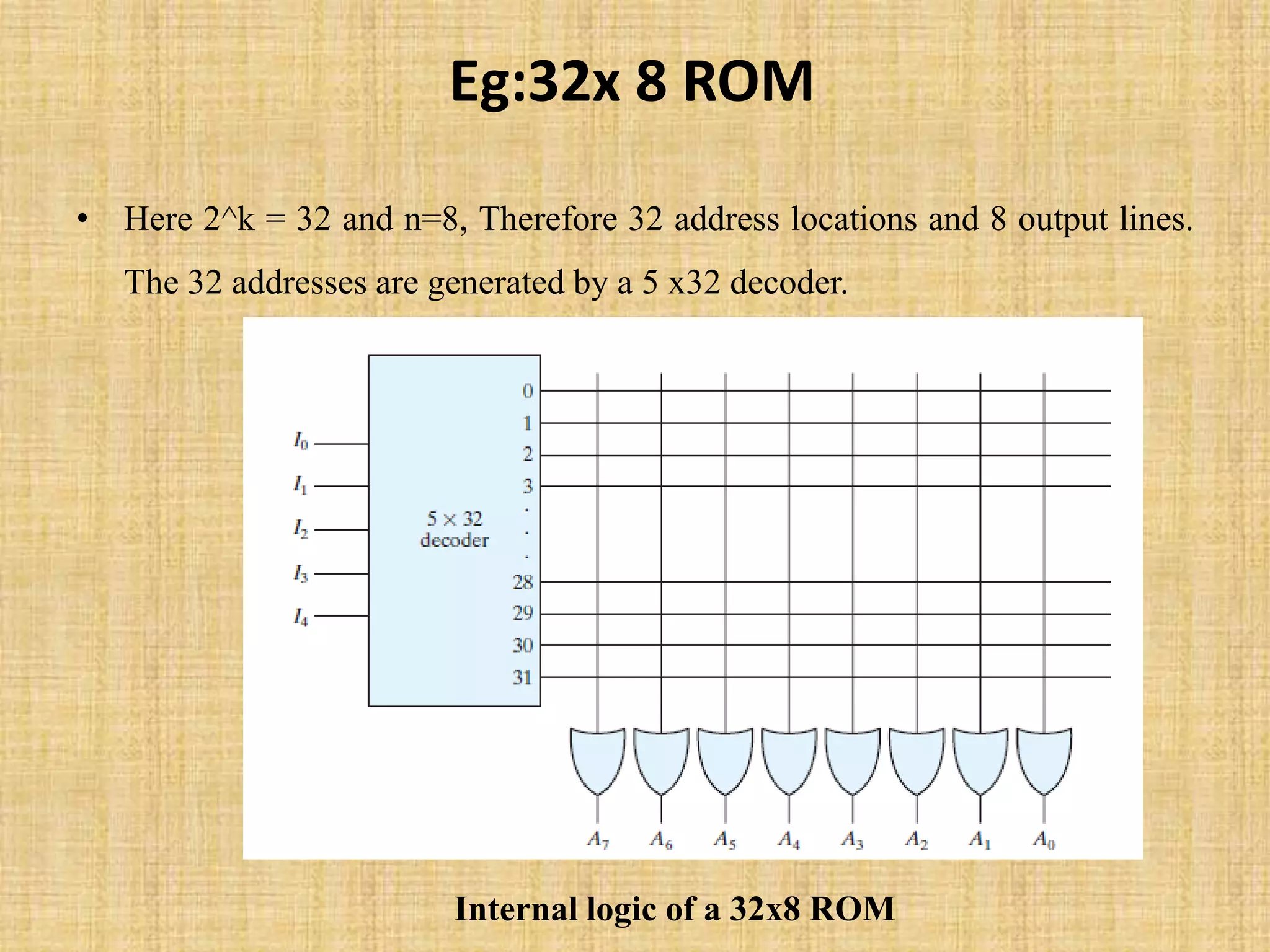

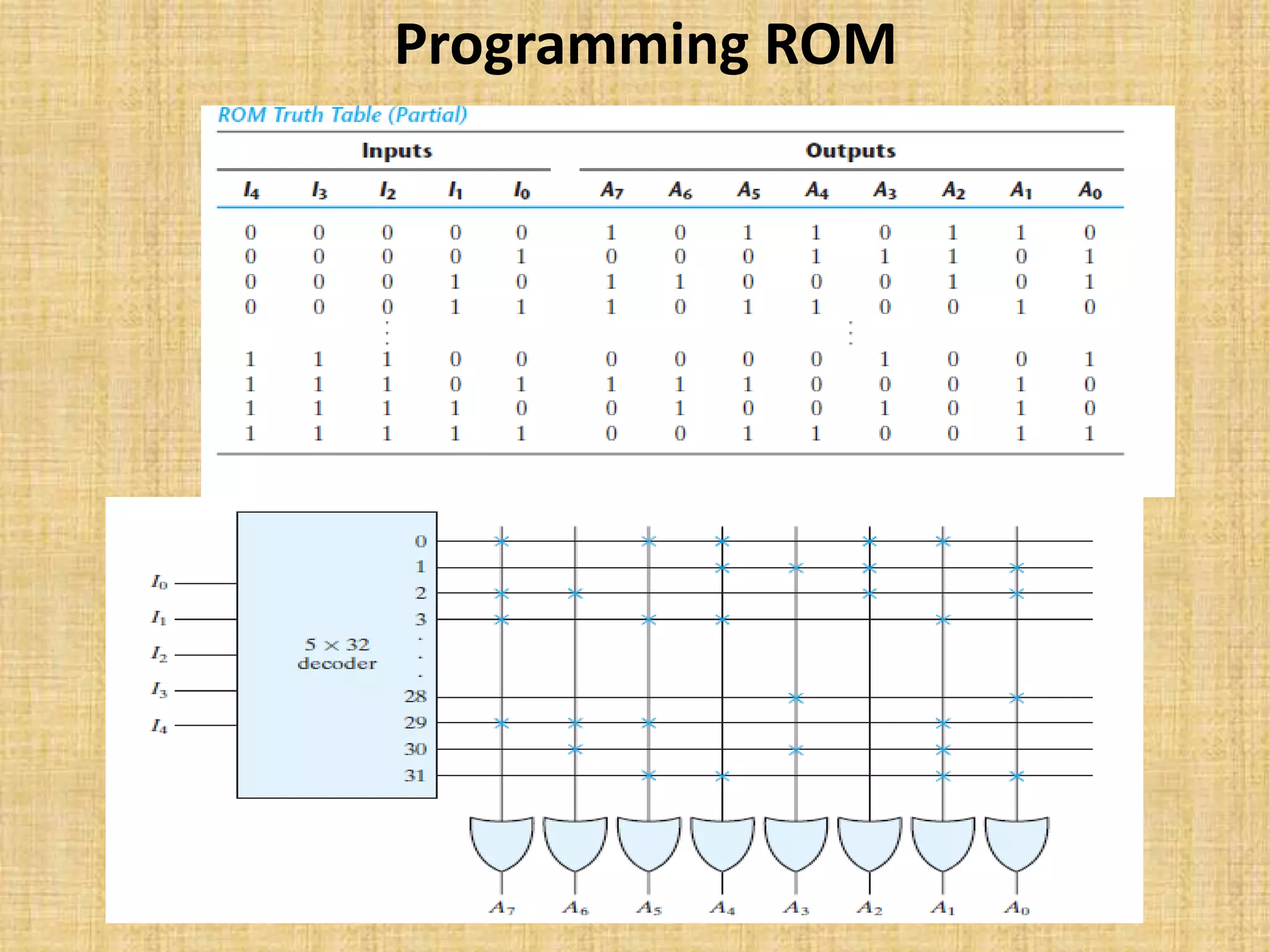

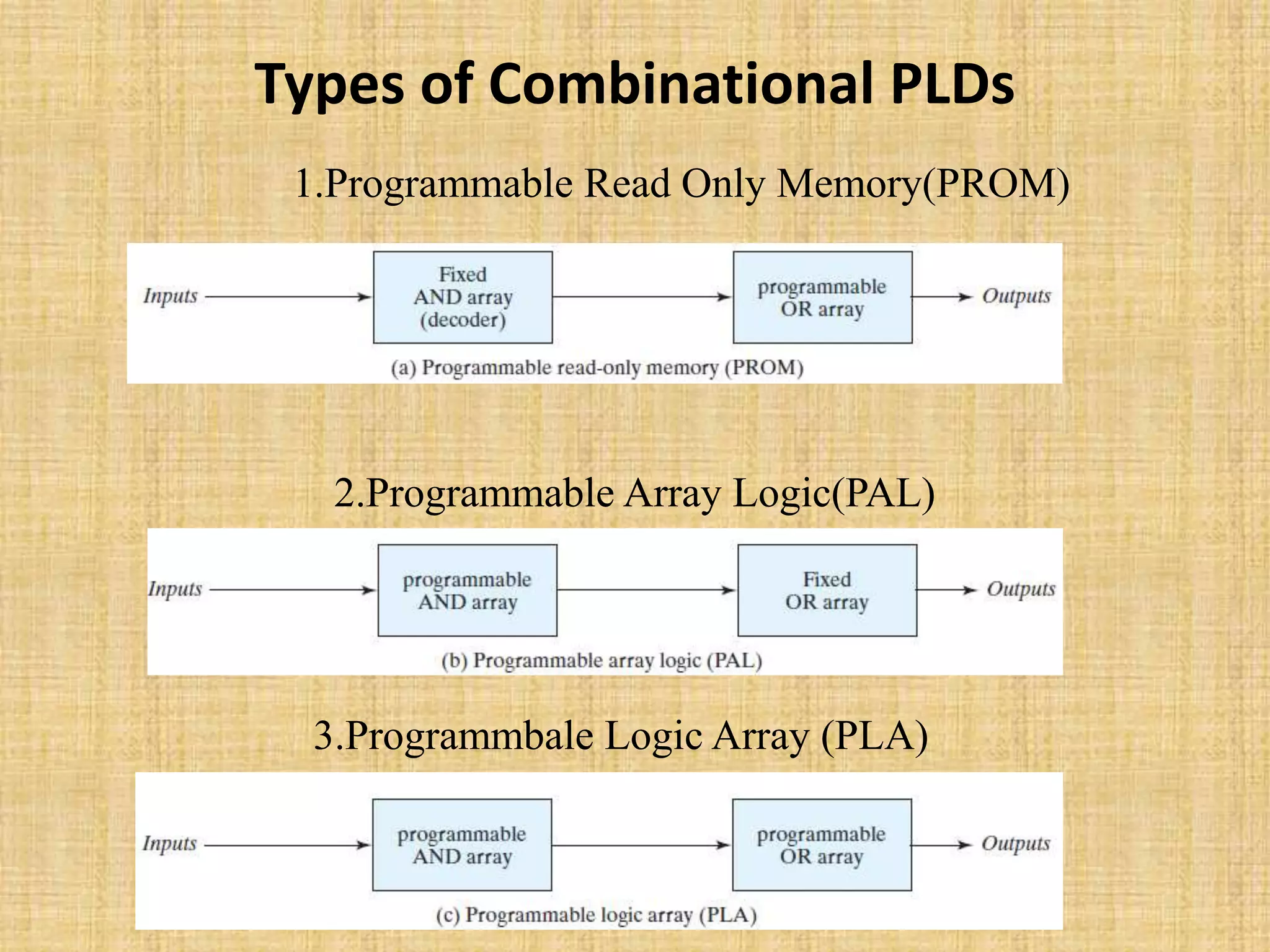

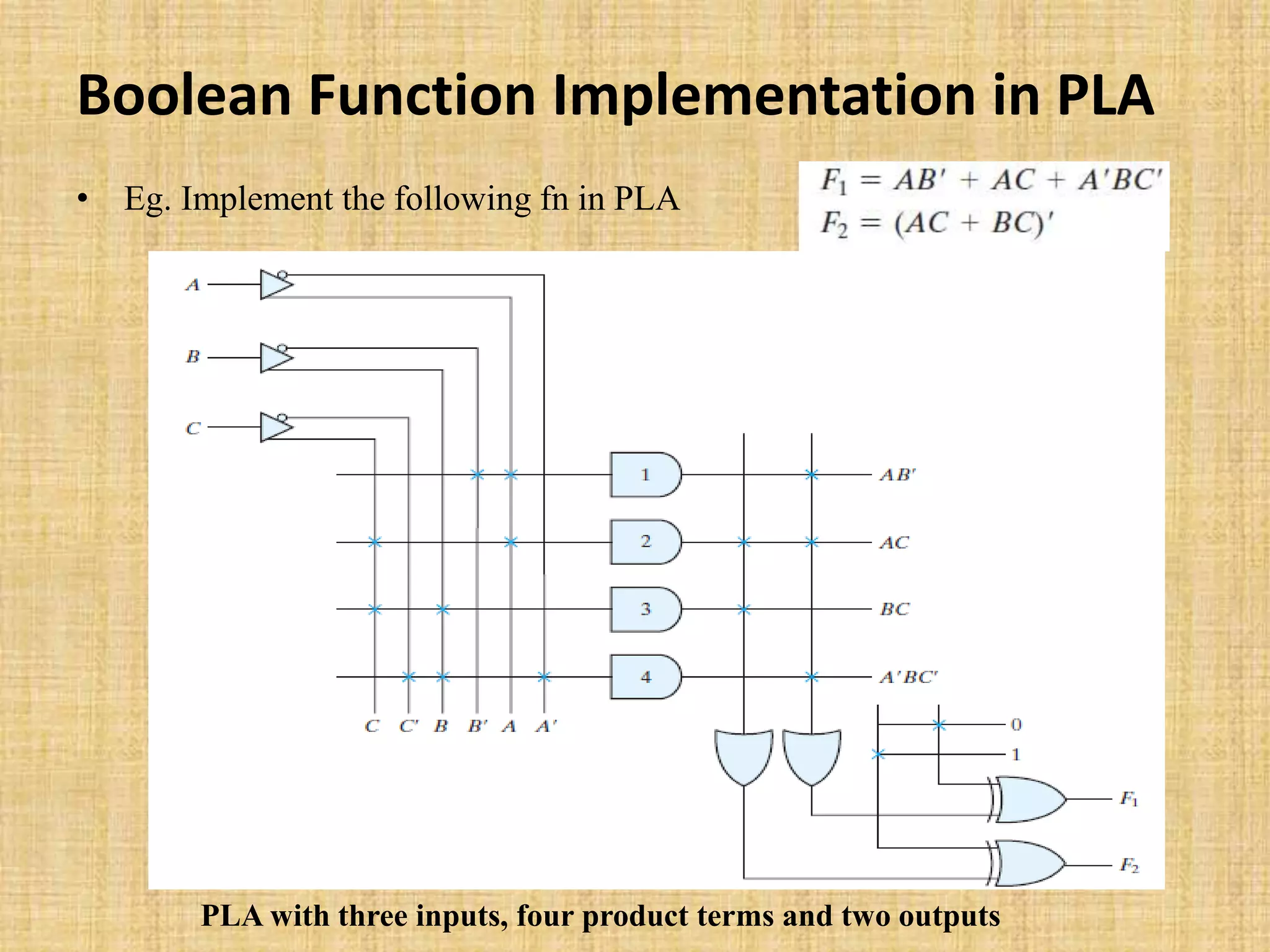

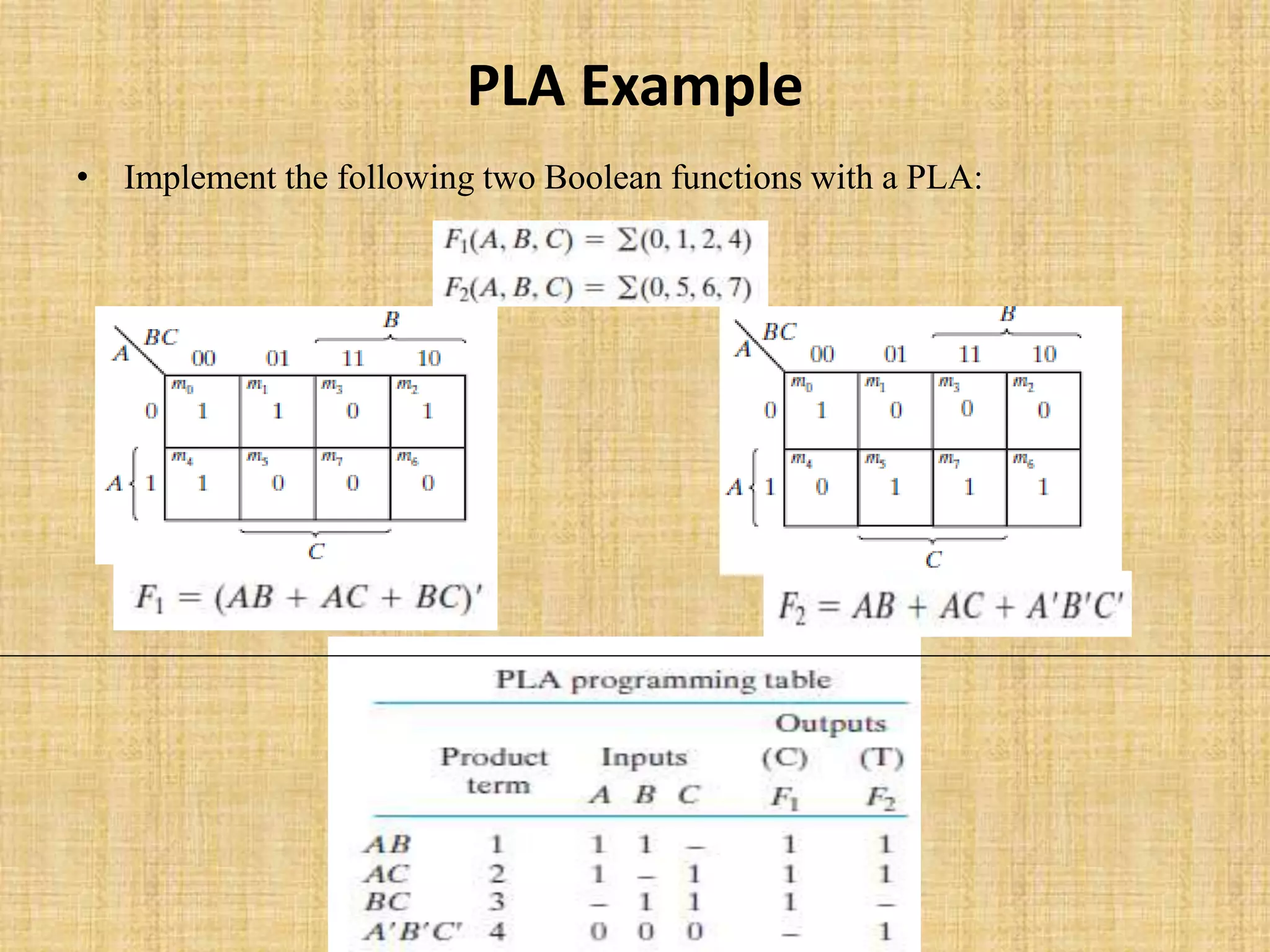

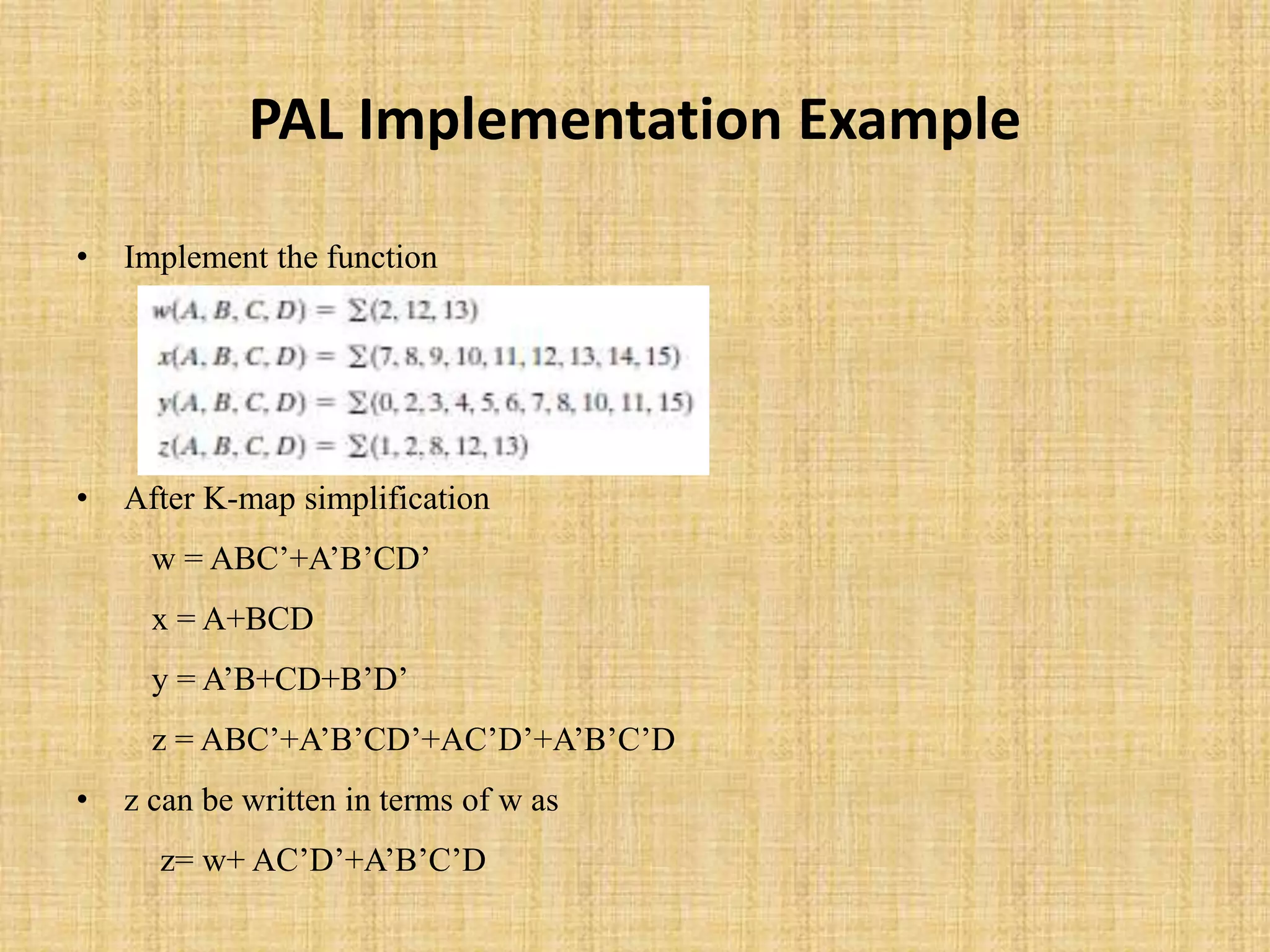

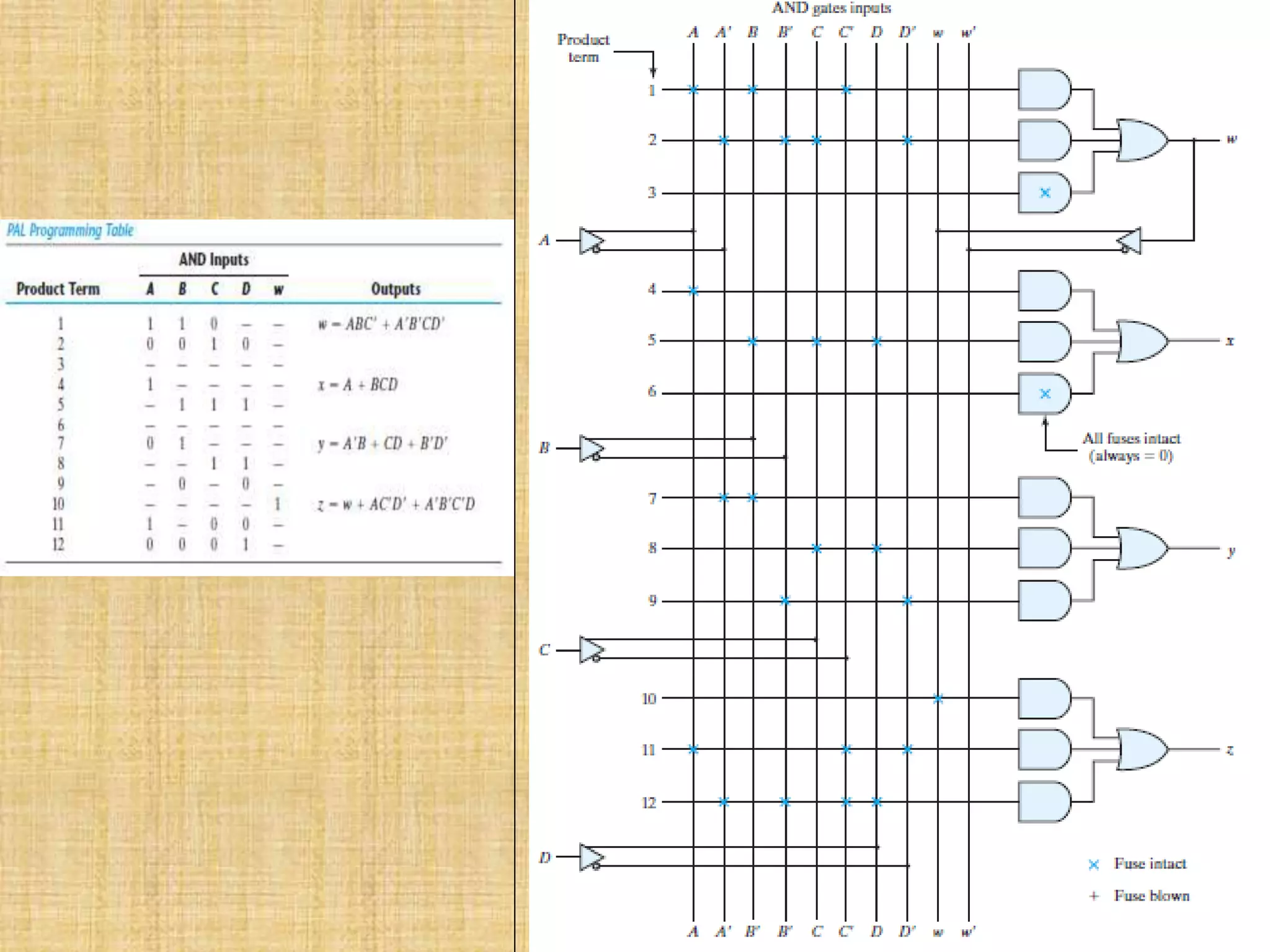

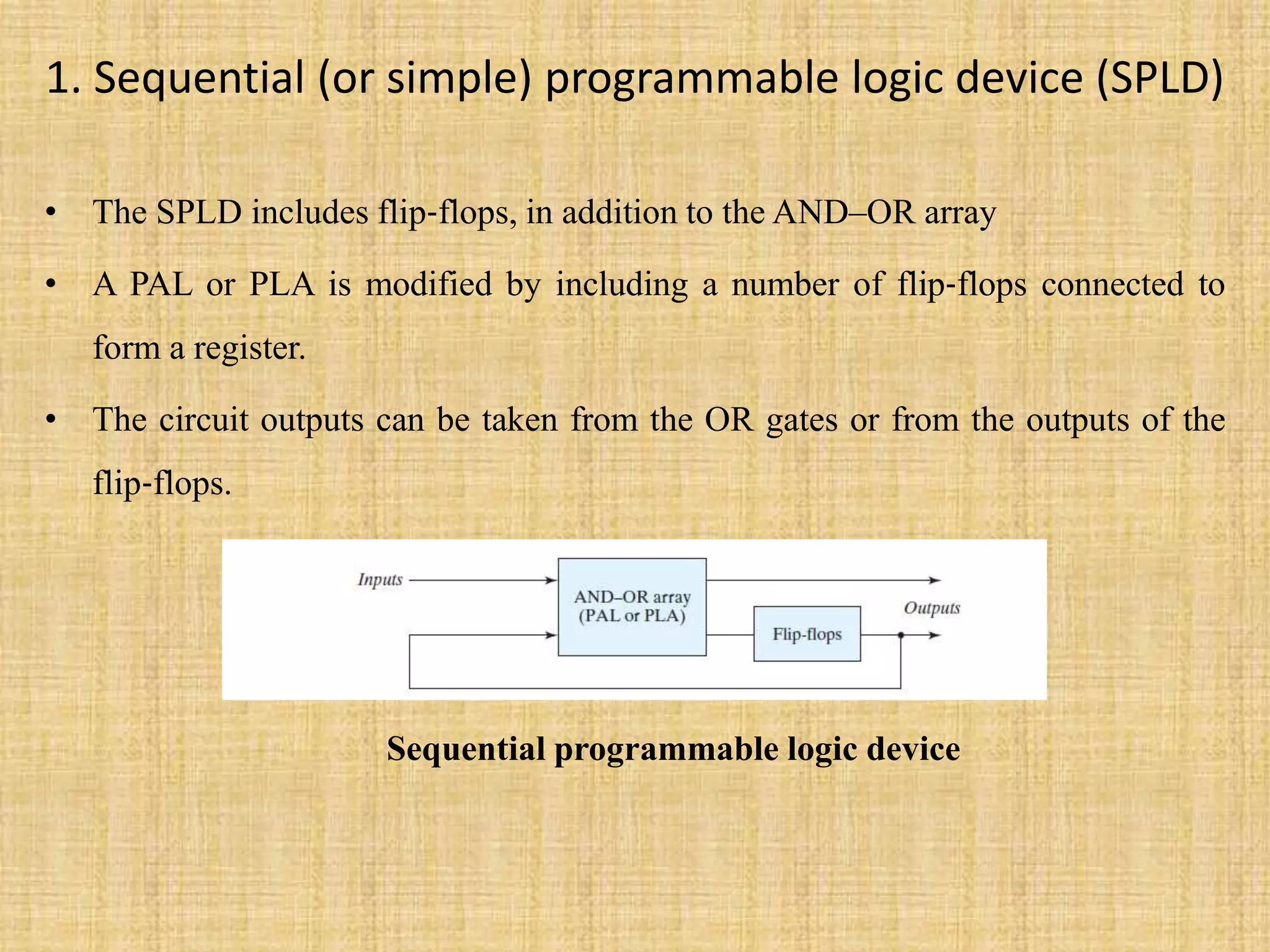

The document discusses different types of programmable logic devices including memory units, random access memory (RAM), read only memory (ROM), programmable logic arrays (PLA), programmable array logic (PAL), and complex programmable logic devices (CPLD). It describes the basic components, operations, and applications of each type of programmable logic device. Memory units can store and retrieve binary data and include RAM and ROM. RAM can be written to and read from while ROM can only be read from. PLDs like PLA and PAL provide configurable logic functions using AND and OR gates that can be programmed. CPLDs contain multiple configurable logic blocks and a programmable interconnect