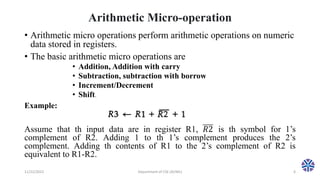

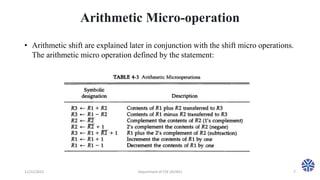

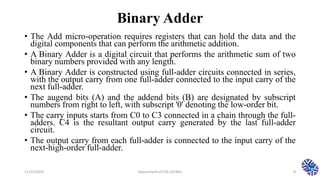

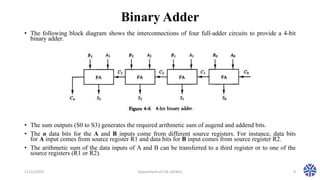

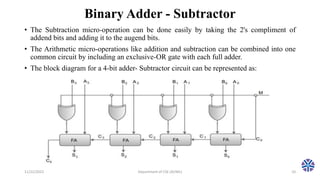

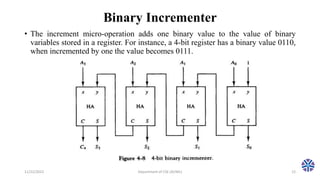

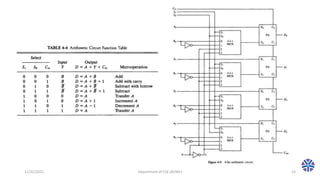

This document provides an overview of the topics covered in Session 3 of the CS307PC course on Computer Organization and Architecture. The session covered Register Transfer Language and microoperations, including register transfer, bus and memory transfers, and different types of microoperations such as arithmetic, logic, and shift microoperations. It provides examples of arithmetic microoperations like addition and subtraction. Binary adders and incrementers are discussed as implementations of arithmetic microoperations. The next session will cover logic and shift microoperations as well as arithmetic shift logic units.