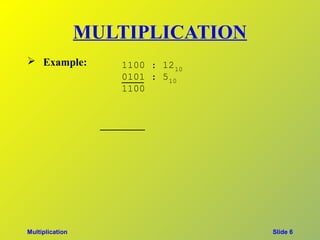

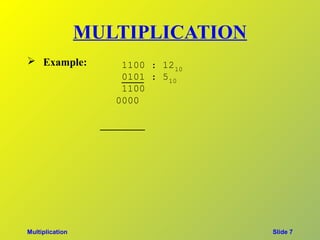

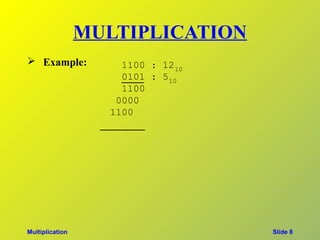

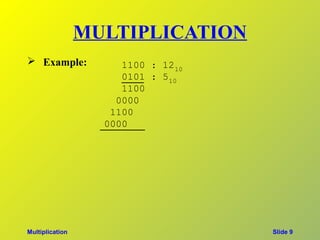

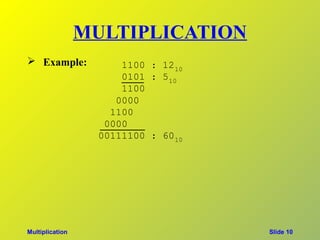

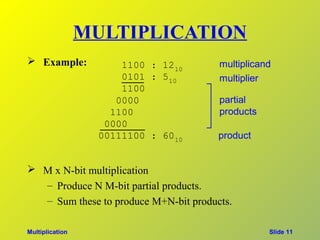

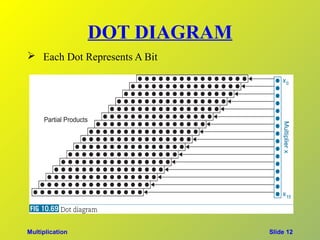

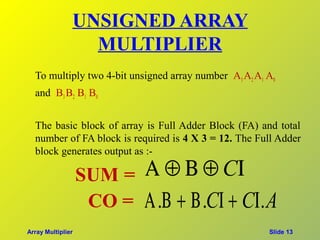

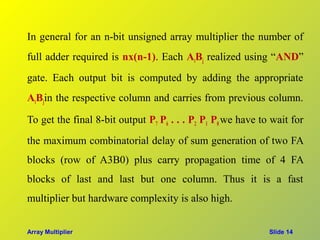

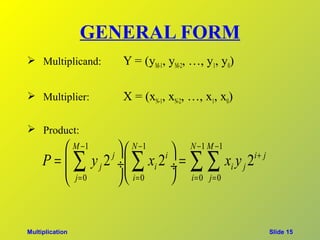

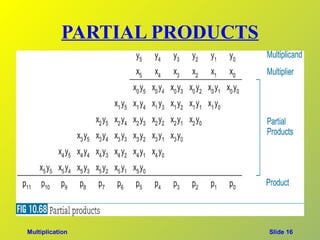

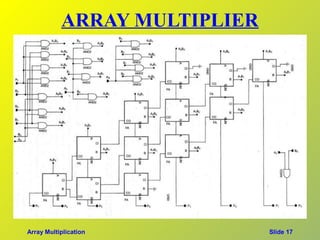

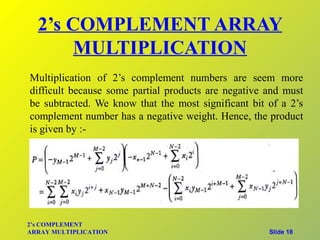

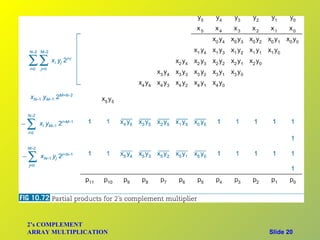

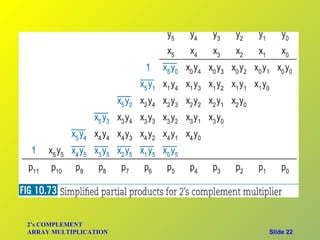

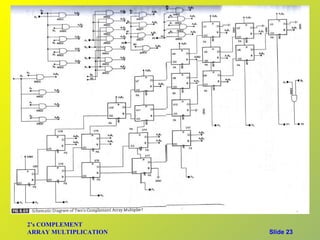

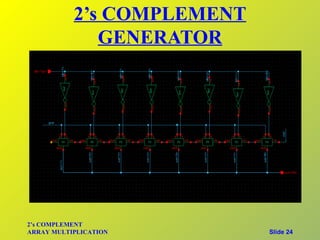

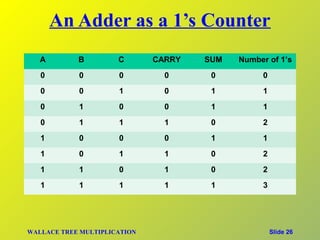

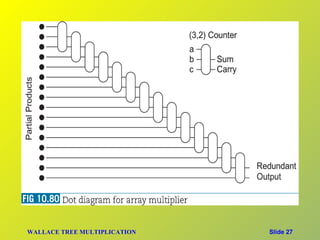

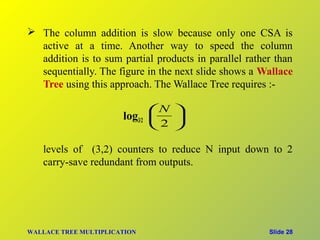

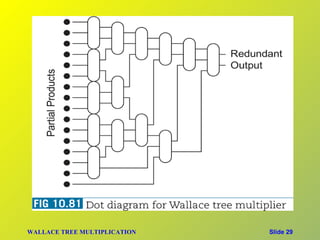

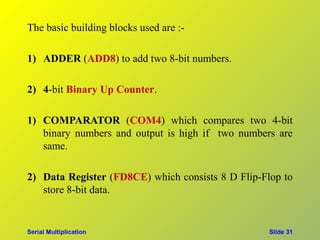

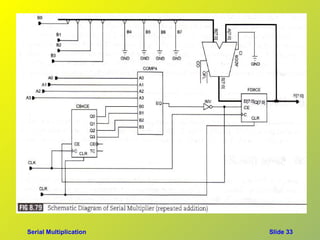

The document discusses various methods of multiplication in data path sub-systems, emphasizing the importance of optimizing multipliers in microprocessors and digital systems. It covers techniques like unsigned array multiplication, 2's complement array multiplication, Wallace tree multiplication, and serial multiplication, detailing their structures, advantages, and operating principles. Additionally, it highlights the complexities and trade-offs in hardware design related to speed, power, and area during multiplication operations.