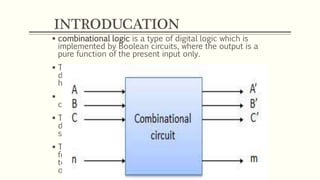

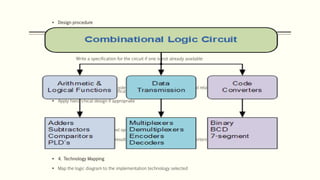

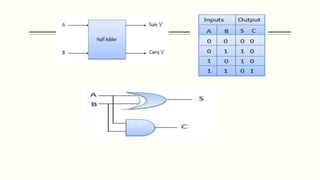

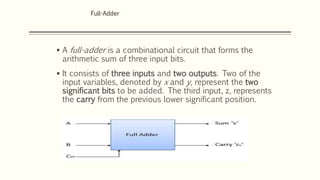

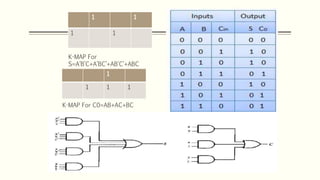

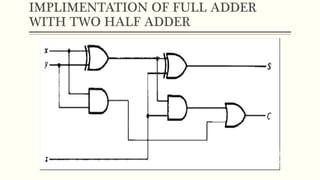

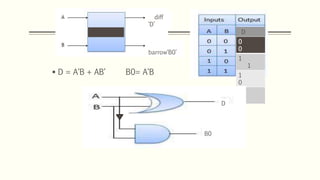

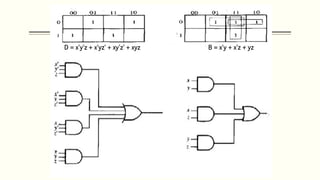

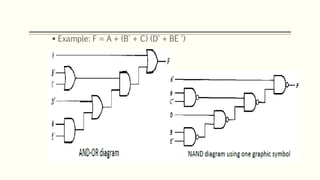

This document summarizes key concepts about combinational logic circuits. It defines combinational logic as circuits whose outputs depend only on the current inputs, in contrast to sequential logic which also depends on prior inputs. Common combinational circuits are described like half and full adders used for arithmetic, as well as decoders. The design process for combinational circuits is outlined involving specification, formulation, optimization and technology mapping. Implementation of functions using NAND and NOR gates is also discussed.