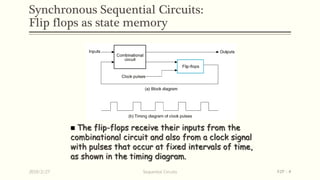

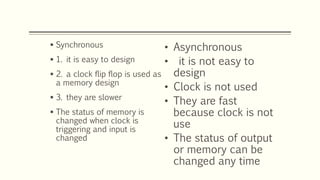

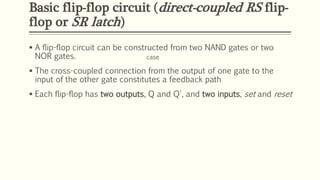

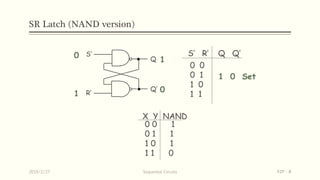

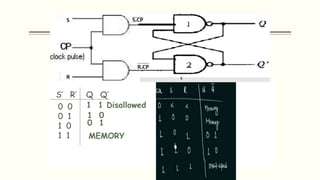

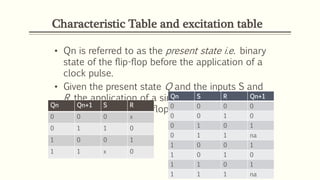

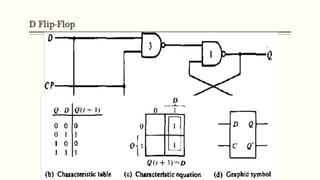

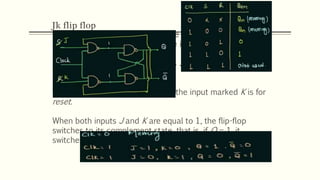

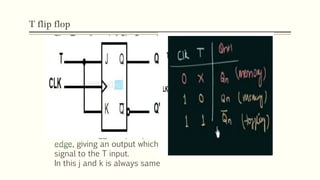

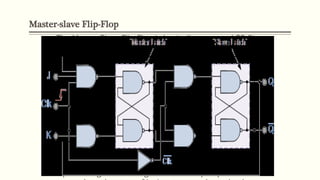

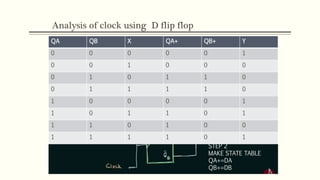

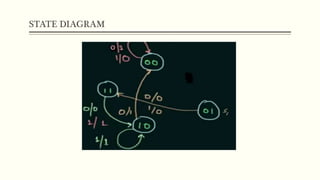

Sequential circuits are circuits whose outputs depend not only on present inputs but also on past inputs or states. There are two types: synchronous use a clock signal to synchronize state changes, asynchronous can change state at any time. Common memory elements are flip-flops including RS, D, JK, and T flip-flops. The master-slave flip-flop construction using two flip-flops avoids unpredictable states by separating the sampling and output functions.