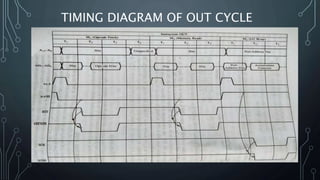

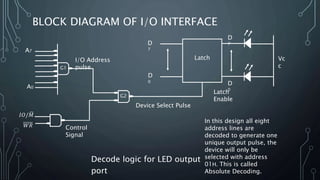

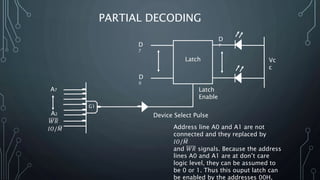

The document discusses I/O interfacing and provides an example of using an OUT instruction to display data from the accumulator on LEDs connected to an output port. It explains that during the M3 cycle of the OUT instruction, the processor places the accumulator data on the data bus. This bus is connected to a latch that is enabled by the IO/M and WR signals to catch the data and display it on the LEDs. It describes how the address of the latch is determined by decoding the address bus lines to generate a device select pulse only when a specific port address is present.