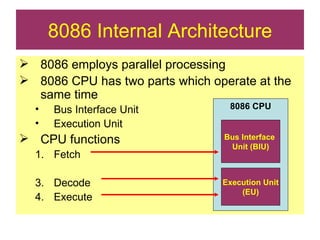

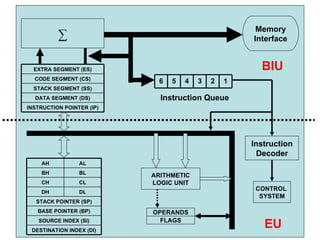

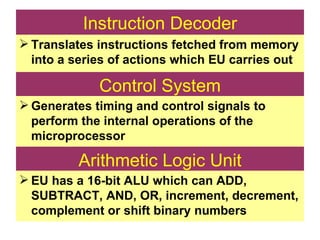

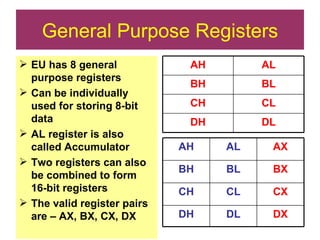

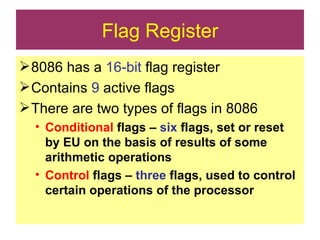

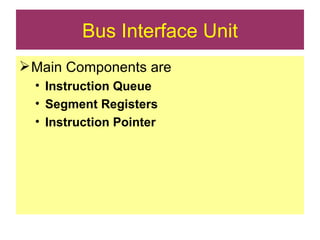

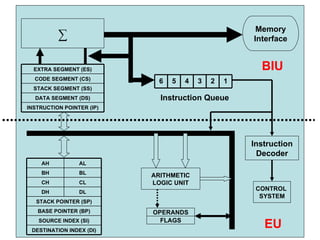

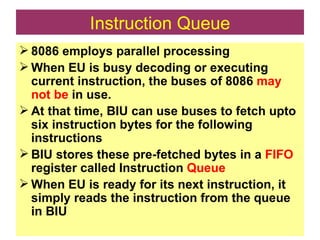

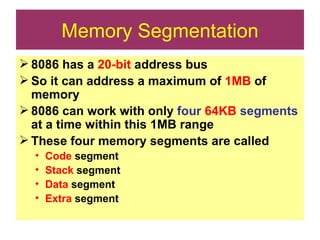

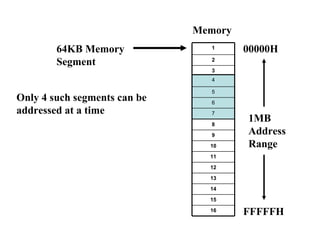

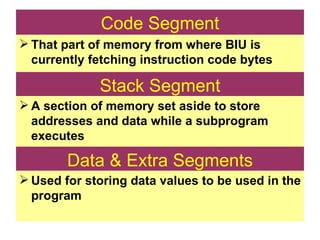

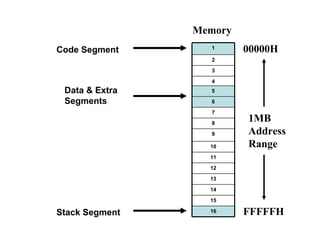

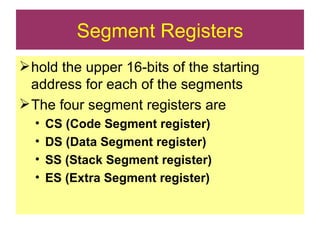

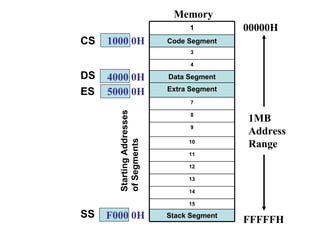

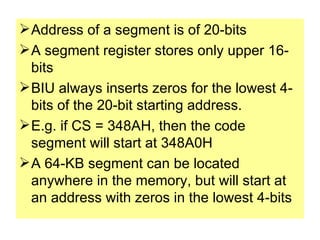

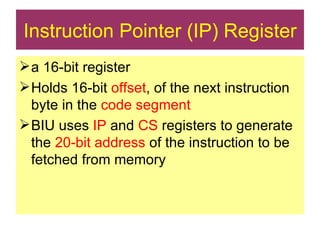

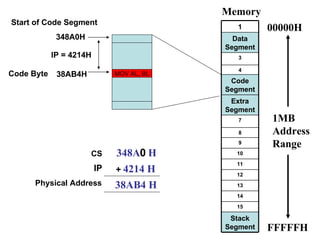

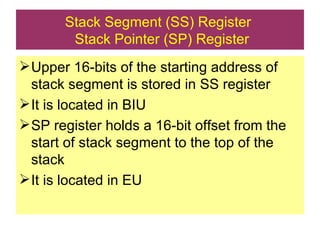

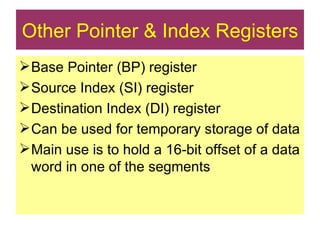

The document provides an introduction to the 8086 microprocessor. It describes how the 8086 is a 16-bit microprocessor that was launched by Intel in 1978. It discusses the internal architecture of the 8086, including how it employs parallel processing through separate bus interface and execution units to improve performance. It also describes the various registers and memory segmentation used in the 8086 architecture.