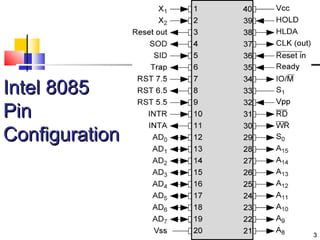

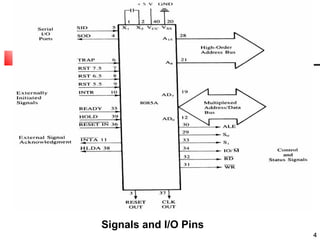

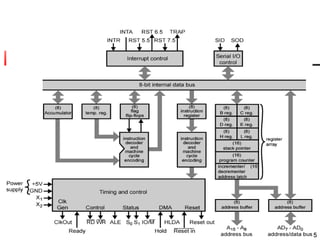

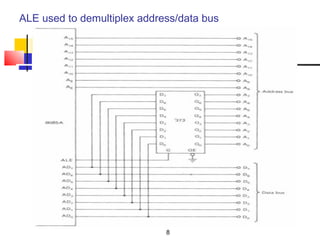

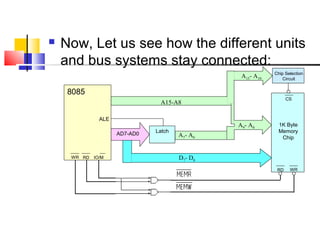

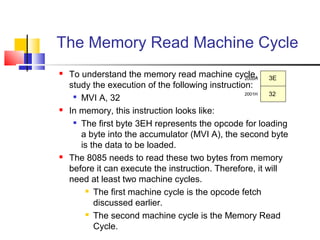

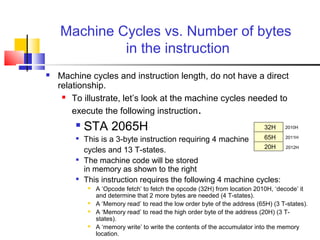

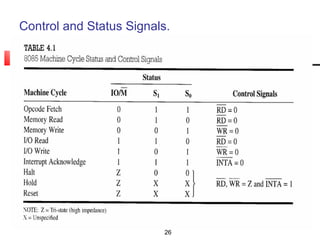

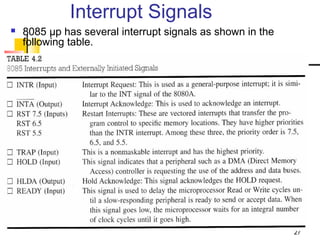

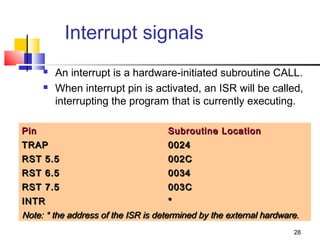

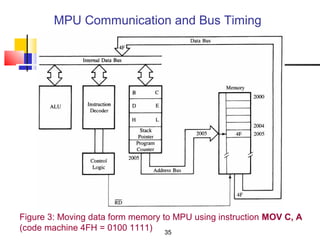

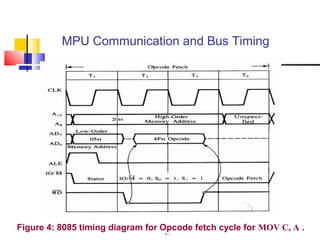

The document provides an introduction to the Intel 8085 microprocessor architecture. It discusses that the 8085 is an 8-bit processor that can address 64KB of memory using 40 pins running at a maximum of 3MHz. It describes the address bus, data bus, control signals, and CPU block diagram. It also explains the different types of machine cycles used by the 8085 like opcode fetch, memory read, and memory write and how instructions of different lengths require varying numbers of cycles.