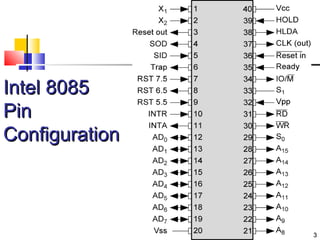

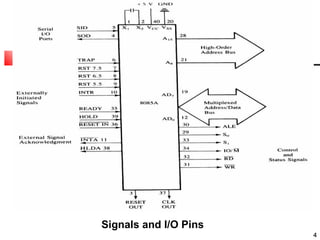

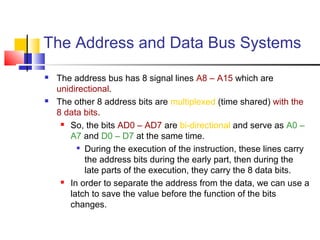

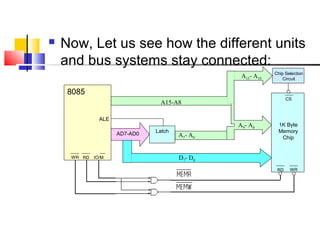

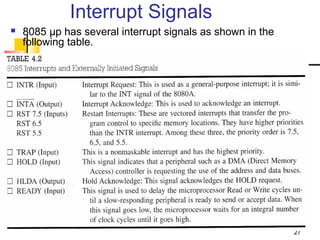

The document provides an overview of the Intel 8085 microprocessor architecture. It discusses the 8085's pins, buses, control signals, arithmetic logic unit, flags register, and memory interfacing. The 8085 uses an 8-bit address bus and 8-bit bi-directional data bus. It has pins for power, clock signals, interrupts and I/O. The document explains the 8085's opcode fetch, memory read/write and I/O read/write machine cycles and timing. It also covers addressing memory chips, interrupt handling and putting the concepts together in a system diagram.