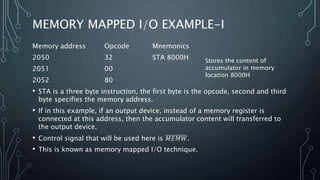

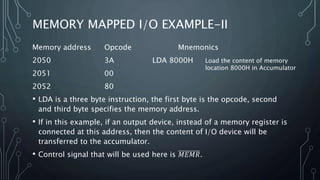

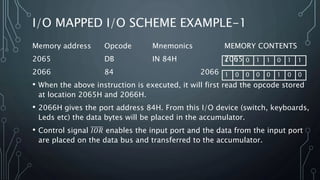

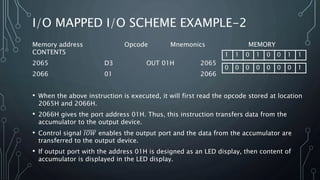

This document discusses two schemes for interfacing I/O devices with a microprocessor: memory mapped I/O and I/O mapped I/O. Memory mapped I/O treats I/O devices like memory locations, using memory instructions and addresses to transfer data. I/O mapped I/O uses special IN and OUT instructions to specify an 8-bit port address for input or output. Examples are given of transferring data between an accumulator and memory/I/O locations using LDA, STA, IN, and OUT instructions.