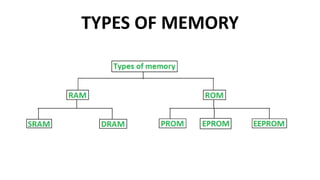

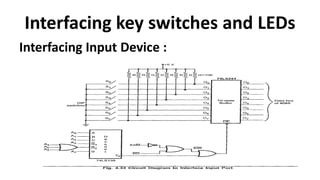

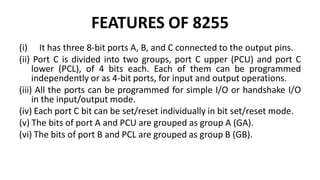

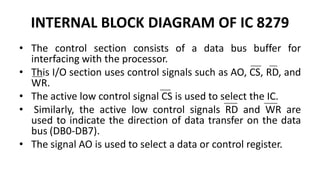

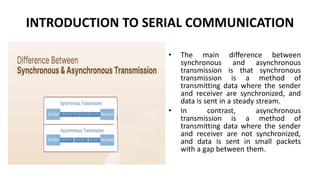

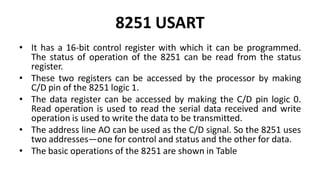

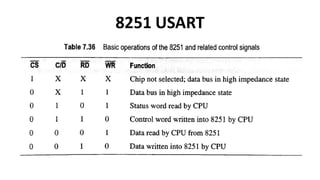

This document provides an overview of memory and I/O interfacing concepts for microprocessors and microcontrollers. It discusses types of memory including RAM, ROM, and EEPROM and methods of memory mapping and addressing such as partial decoding and complete decoding. It also covers I/O interfacing topics like I/O mapping, interfacing switches and LEDs, the 8255 Programmable Peripheral Interface chip, and serial communication using the 8251 USART.