Embed presentation

Downloaded 46 times

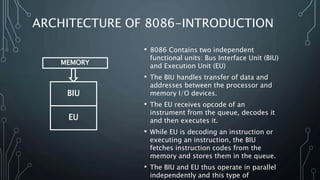

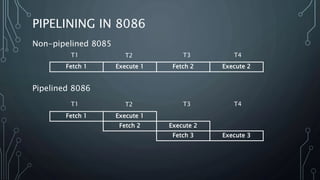

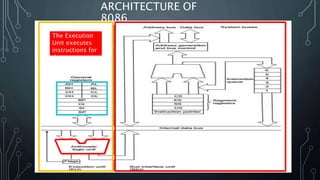

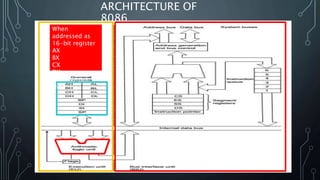

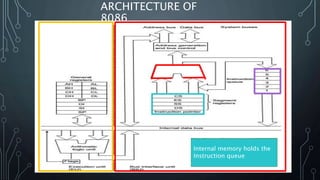

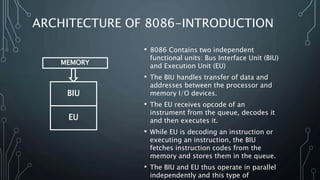

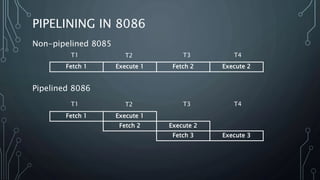

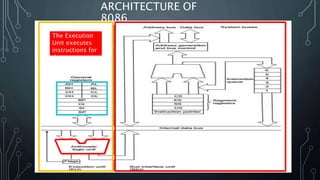

The 8086 microprocessor uses a pipelined architecture with two independent functional units: the Bus Interface Unit (BIU) and the Execution Unit (EU). The BIU handles data/address transfers between memory/I/O devices and the processor. The EU receives instructions from the queue, decodes them, and executes them. While the EU is decoding/executing an instruction, the BIU fetches the next instruction, allowing the two units to operate in parallel for improved performance over non-pipelined designs like the 8085. The 8086 can address registers as either 8-bit or 16-bit and uses segment registers to address 1MB of segmented memory space.