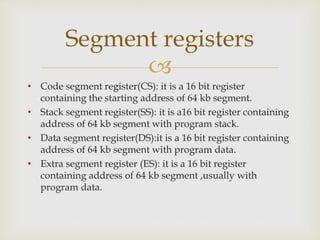

The document summarizes the registers in the Intel 8086 microprocessor architecture. It describes the 4 general purpose registers (AX, BX, CX, DX), 4 segment registers (CS, SS, DS, ES), 2 pointer registers (SP, BP), 2 index registers (SI, DI), the instruction pointer register (IP), and the flag register. The general purpose registers include the accumulator (AX), base (BX), counter (CX), and data (DX) registers. The segment registers contain the starting addresses of the 4 separate 64kb memory segments for code, stack, data, and extra data.