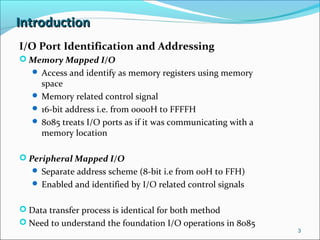

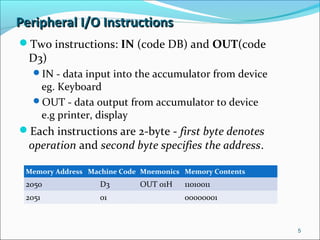

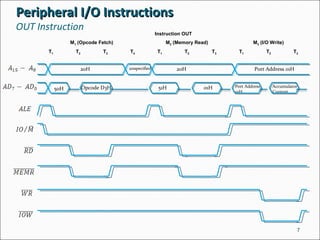

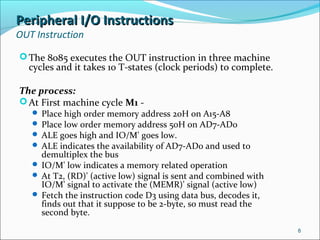

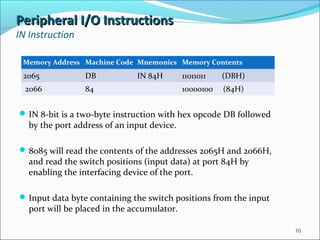

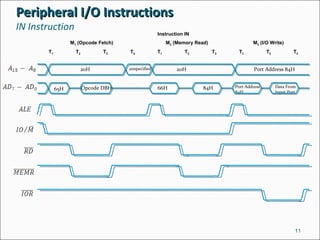

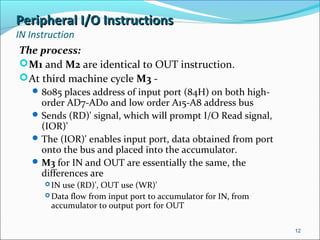

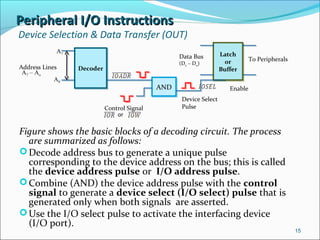

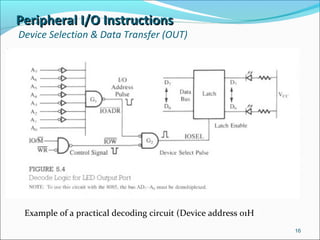

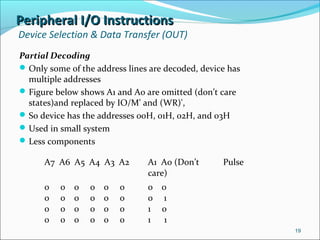

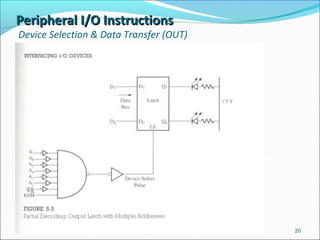

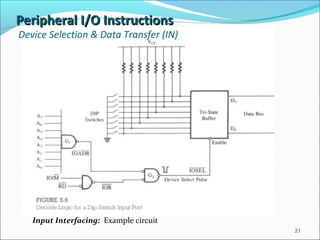

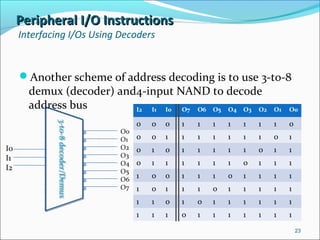

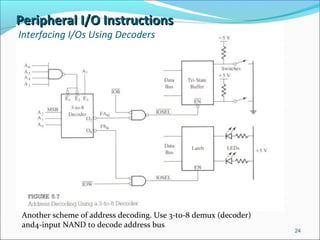

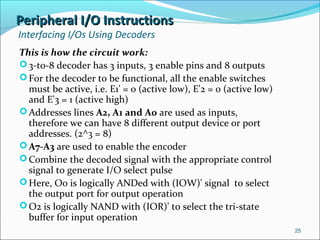

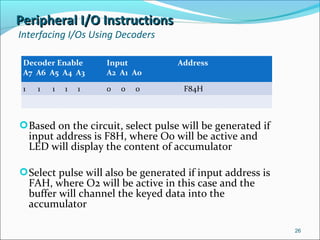

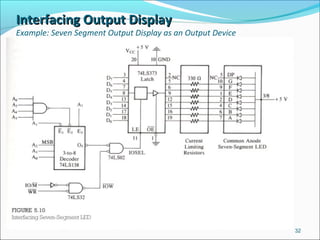

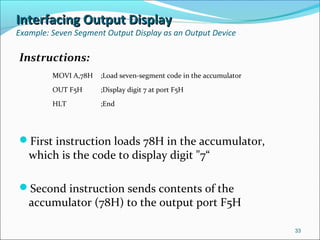

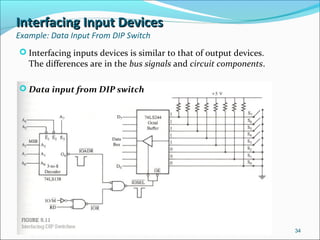

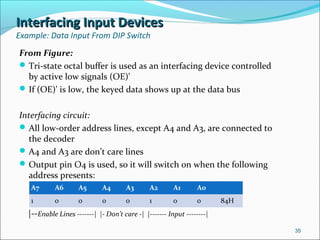

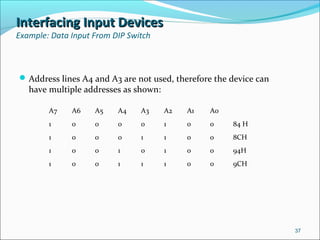

The document discusses peripheral input/output (I/O) instructions in 8085 microprocessor. It describes the OUT and IN instructions used for peripheral-mapped I/O. The OUT instruction outputs data from the accumulator to an I/O port, while the IN instruction inputs data from an I/O port into the accumulator. It explains the decoding circuits used to select I/O devices based on their addresses. The decoding circuits generate pulses to latch output data and enable input buffers at the appropriate times.