Embed presentation

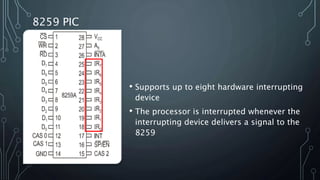

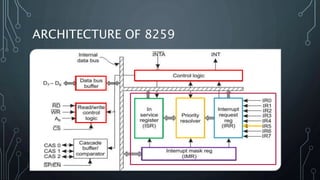

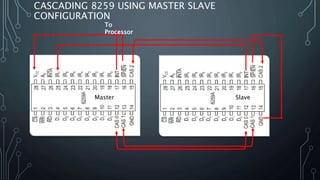

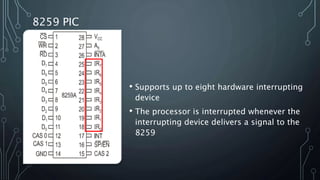

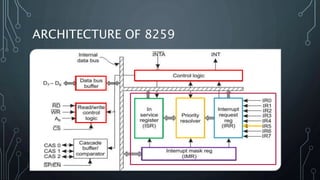

Download to read offline

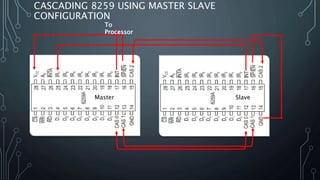

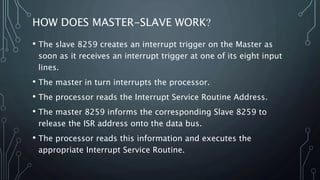

The document discusses the 8259 Programmable Interrupt Controller (PIC), which supports up to eight hardware interrupting devices and interrupts the processor when a device delivers a signal. The PIC is required for systems with more than four I/O devices since the 8085 processor can only handle four interrupt requests. The PIC architecture allows multiple PICs to be cascaded in a master-slave configuration so that the slave PIC interrupts the master which then interrupts the processor, and the master and slave work together to provide the interrupt service routine address to the processor.