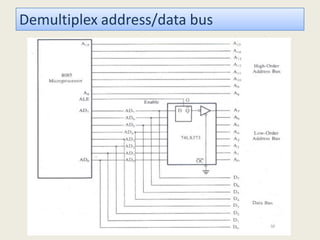

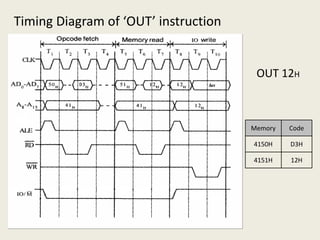

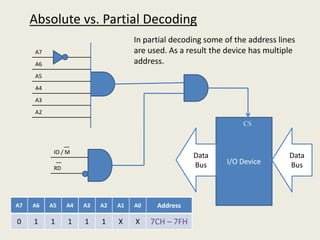

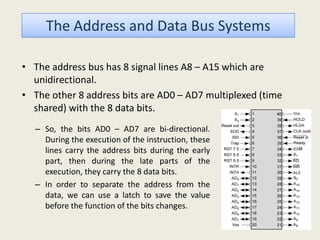

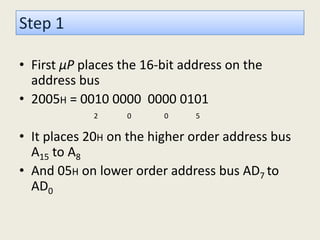

The document discusses the pin configuration and addressing modes of the Intel 8085 microprocessor. It has 16 address lines, with 8 lines (A8-A15) dedicated to addressing memory locations and 8 lines (AD0-AD7) that are multiplexed to carry both address and data information. These lower address lines are connected to a latch enabled by the ALE signal to separate the address and data. The document provides examples of writing data to and reading data from memory using the 8085's control signals. It also describes how I/O devices can be interfaced using either 8-bit peripheral I/O addressing of 256 devices or 16-bit memory mapping that treats I/O registers as part of the memory address space

![Step 2

• Lower order address bus [AD7 to AD0] are connected with a latch

• Latch is such a device whose input = output

when it is activated

• ALE (Address Latch Enable) signal is

used to activate or deactivate the latch

when it is activated

• But when it is deactivated output does not

change with input](https://image.slidesharecdn.com/overview2-180116081037/85/Microprocessor-Part-2-7-320.jpg)

![Step 3

• Once the lower order address is latched µP

places the data on the data bus [AD7 to AD0]

• And generate an appropriate control signal to• And generate an appropriate control signal to

enable selected memory register

• Thus the data [4FH] is stored in memory

location 2005H](https://image.slidesharecdn.com/overview2-180116081037/85/Microprocessor-Part-2-9-320.jpg)