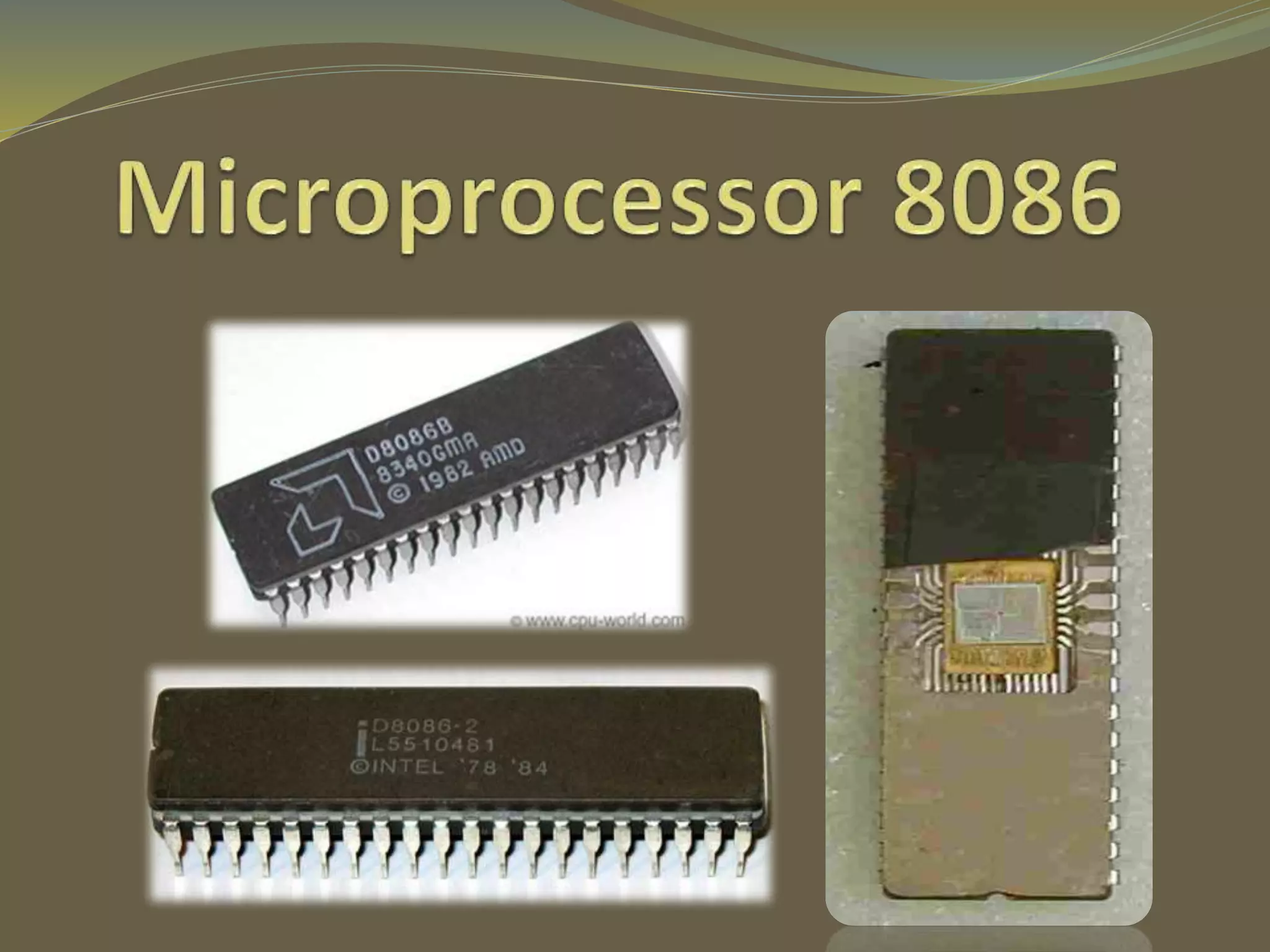

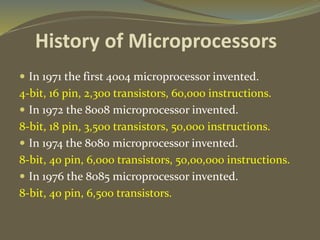

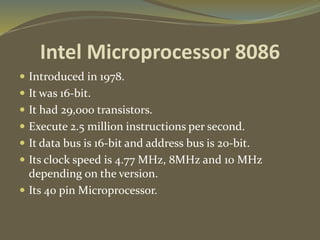

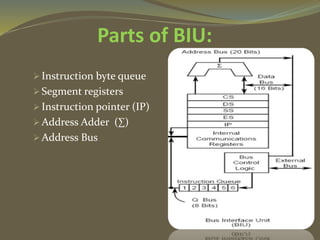

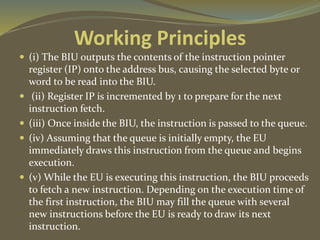

The document discusses the history and architecture of Intel microprocessors from the 4004 in 1971 to the 8086 introduced in 1978. It describes the 8086 as the first 16-bit microprocessor with 29,000 transistors that could execute over 2.5 million instructions per second. The 8086 had an internal architecture with separate bus interface and execution units that concurrently fetch, decode, and execute instructions to improve performance.