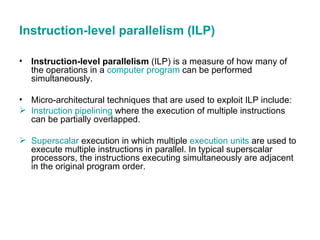

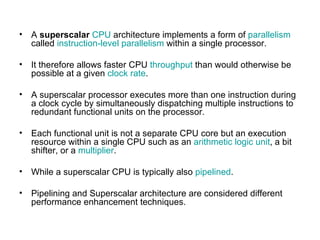

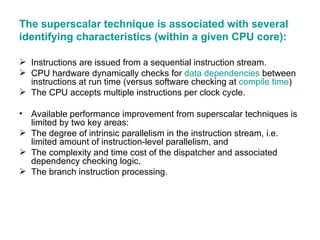

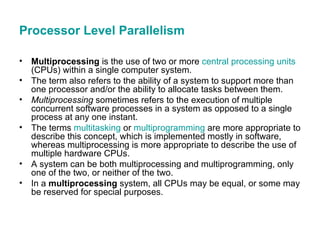

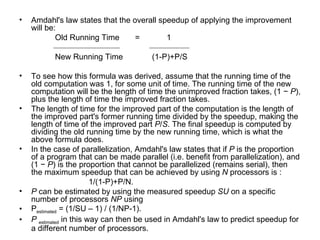

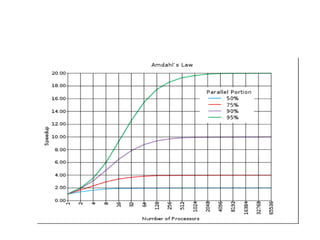

Unit-4 discusses parallelism and techniques to exploit concurrency in computers. The goals of parallelism are to increase computational speed and throughput. There are different types of parallelism like instruction level parallelism, processor level parallelism using multiple processors, and pipelining to overlap instruction execution. Amdahl's law predicts the maximum speedup from parallel processing based on the sequential fraction of a program.