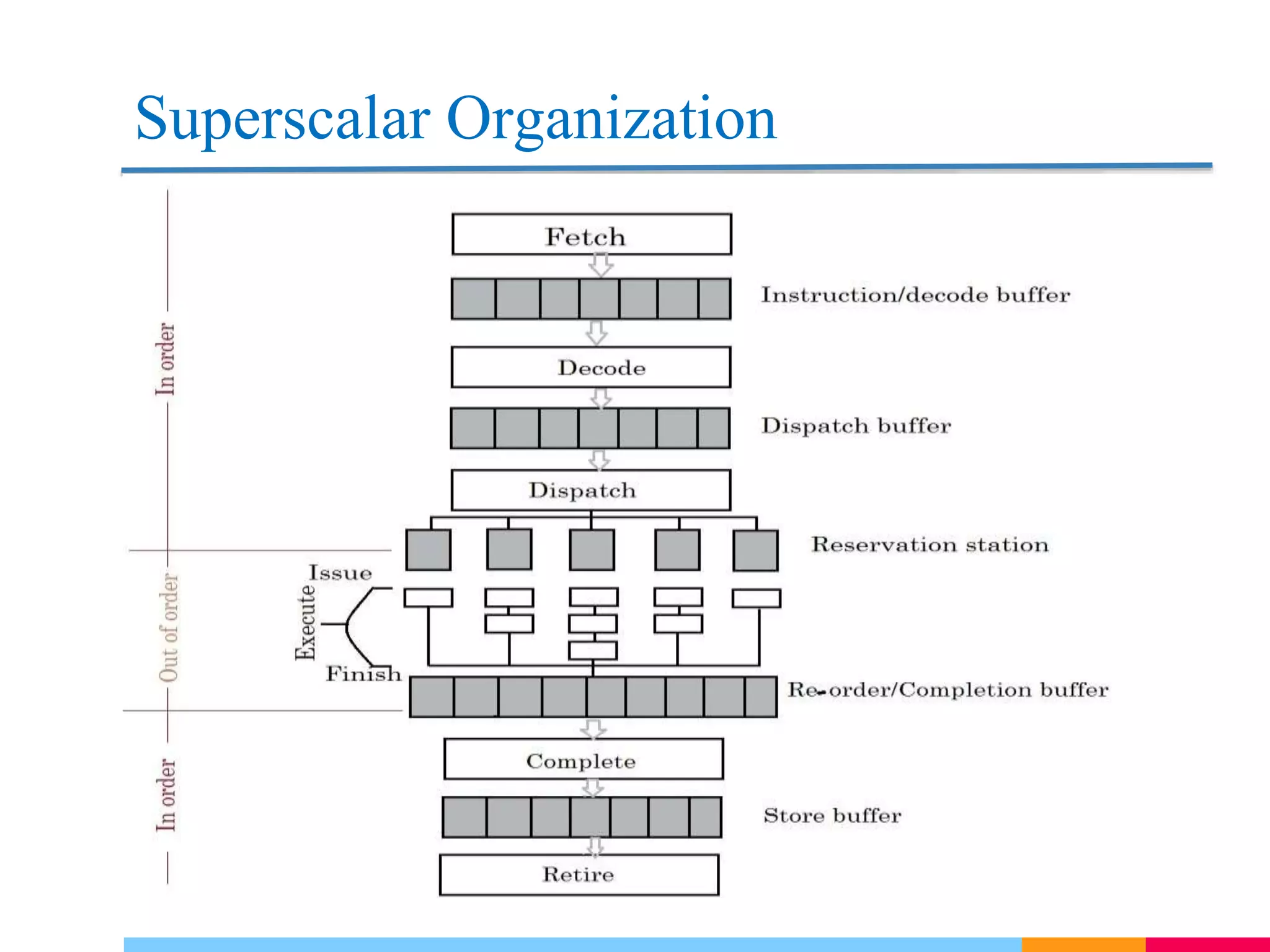

This document discusses superscalar processors, which can execute multiple instructions in parallel within a single processor. A superscalar processor improves performance by executing scalar instructions simultaneously. It consists of an instruction dispatch unit that routes decoded instructions to functional units, reservation stations that decouple instruction decoding from execution, and a reorder buffer that stores in-flight instructions and ensures they complete in program order. While superscalar processors can increase performance, they have limitations such as branch delays and complexity that limit scalability.

![Simple superscalar pipeline

By fetching and dispatching two instructions at a time, a maximum of two instructions per cycle can be

completed. (IF = Instruction Fetch, ID = Instruction Decode, EX = Execute, MEM = Memory access,

WB = Register write back, i = Instruction number, t = Clock cycle [i.e., time])](https://image.slidesharecdn.com/superscalarseminer-171029073807/75/Superscalar-Processor-4-2048.jpg)

![References

1. Nptel lecture IIT Madras (online certification course) Superscalar processor

organization

2. https://en.wikipedia.org/wiki/Supercalar

3. https://www.slideshare.net/

4. [John_L._Hennessy,_David_A._Patterson]_Computer_Architecture , A

Quantitative

Approach, 4th Edition , (Digital copy) from bookfi.net.](https://image.slidesharecdn.com/superscalarseminer-171029073807/75/Superscalar-Processor-13-2048.jpg)