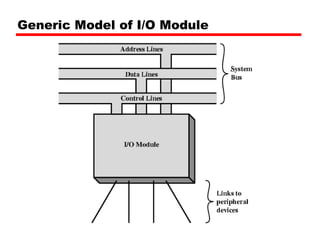

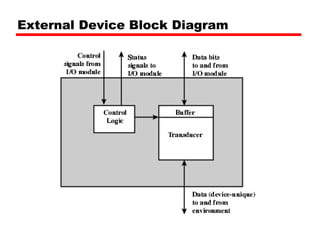

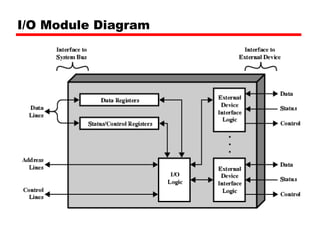

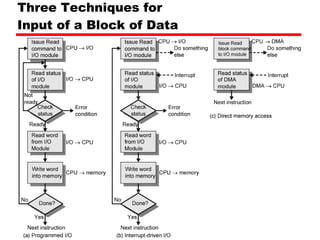

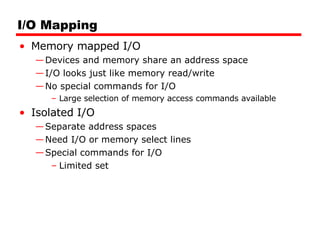

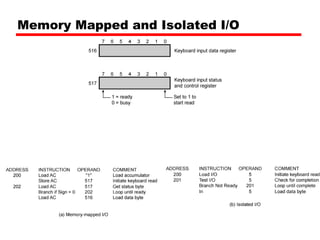

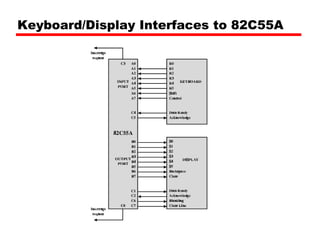

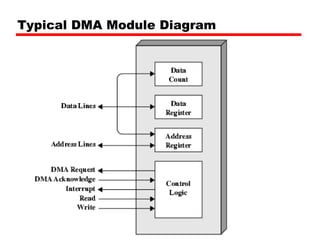

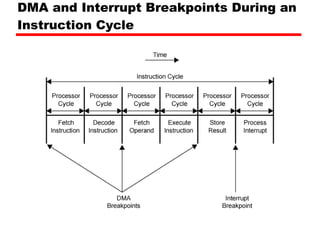

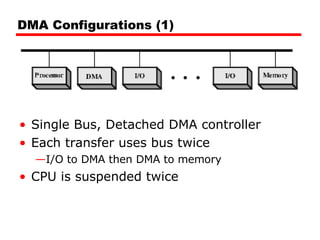

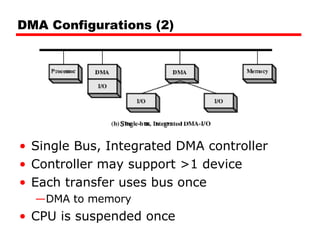

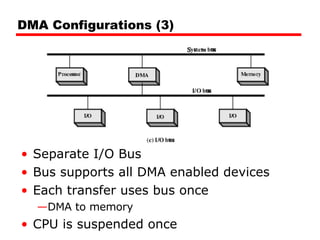

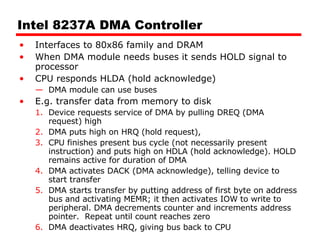

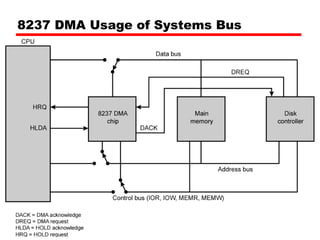

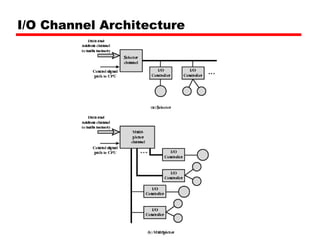

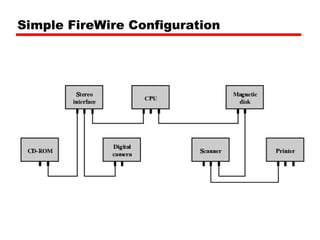

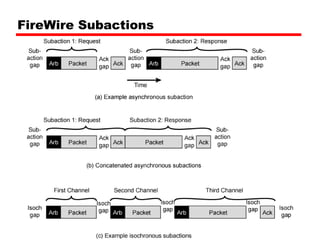

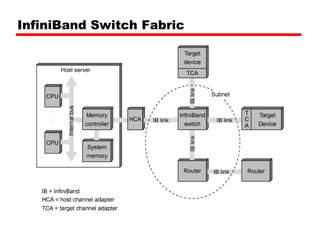

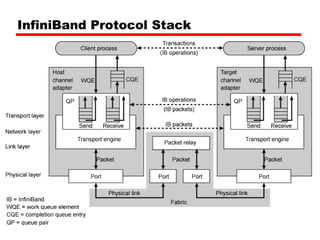

The document discusses various techniques for input/output (I/O) in computer systems, including programmed I/O, interrupt-driven I/O, and direct memory access (DMA). It describes how I/O modules interface with CPUs and peripherals to handle data transfer between devices that operate at different speeds. Common I/O bus standards like ISA, PCI, FireWire, and InfiniBand are also overviewed in terms of their architecture, protocols, and applications.