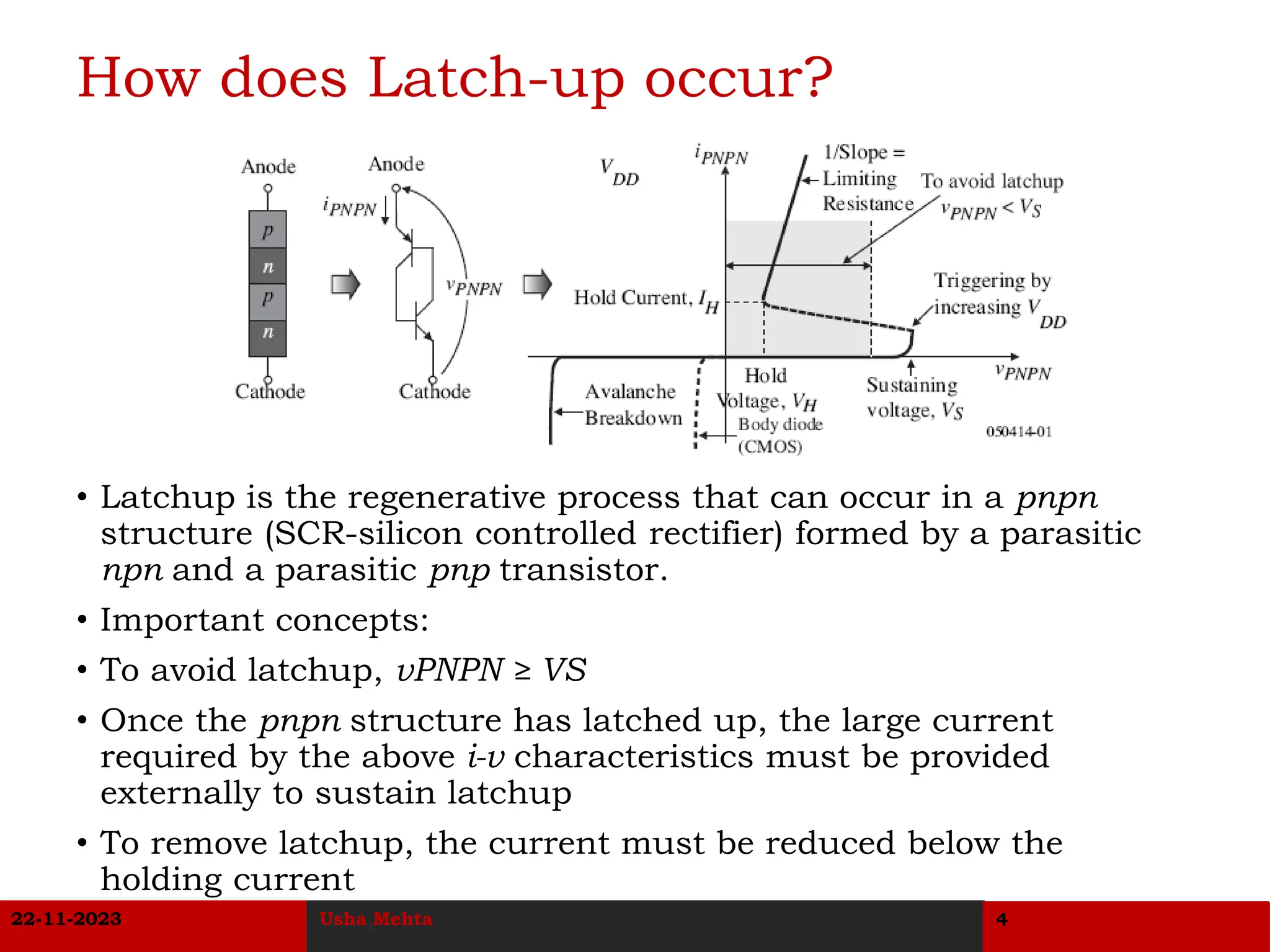

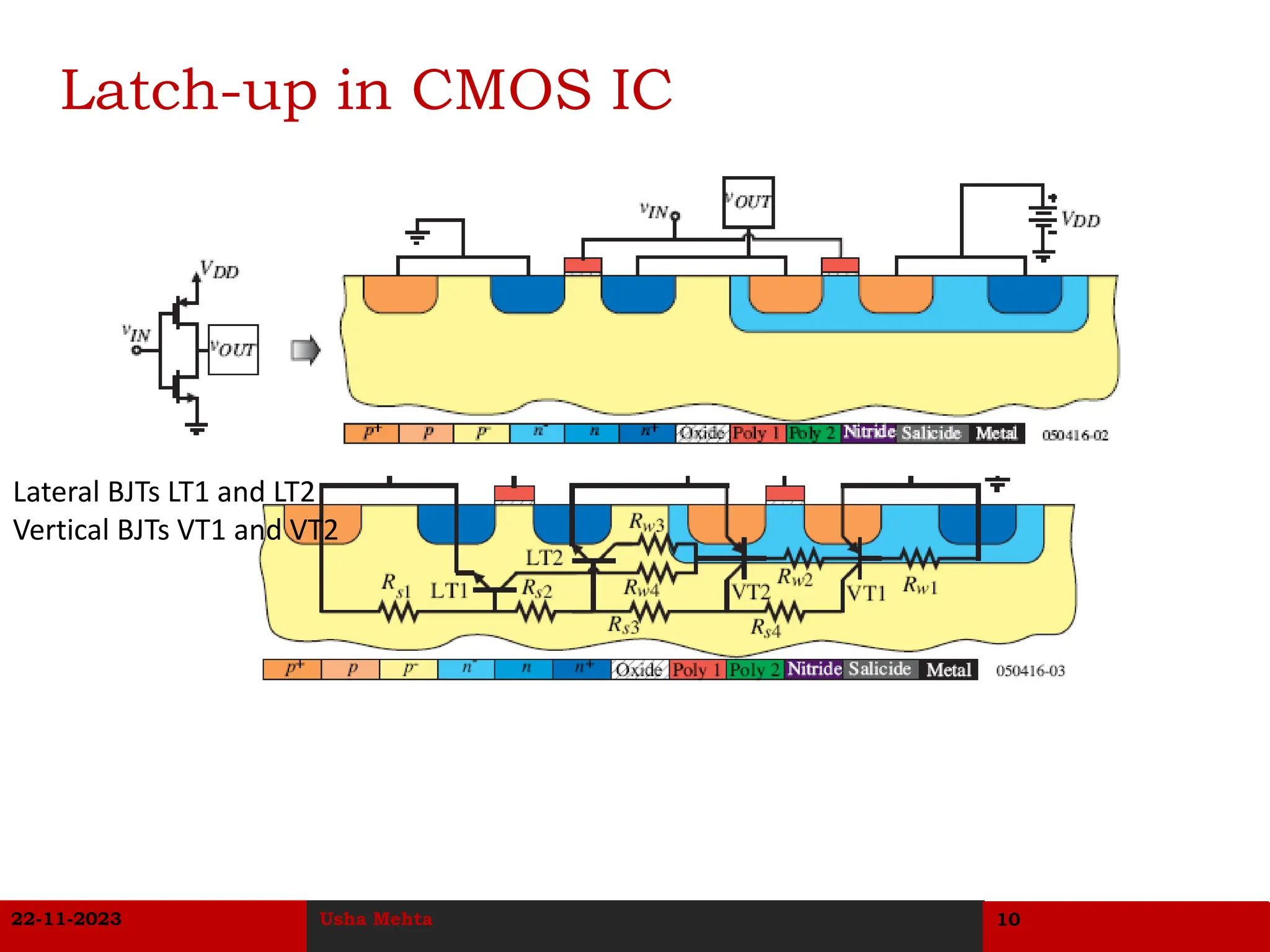

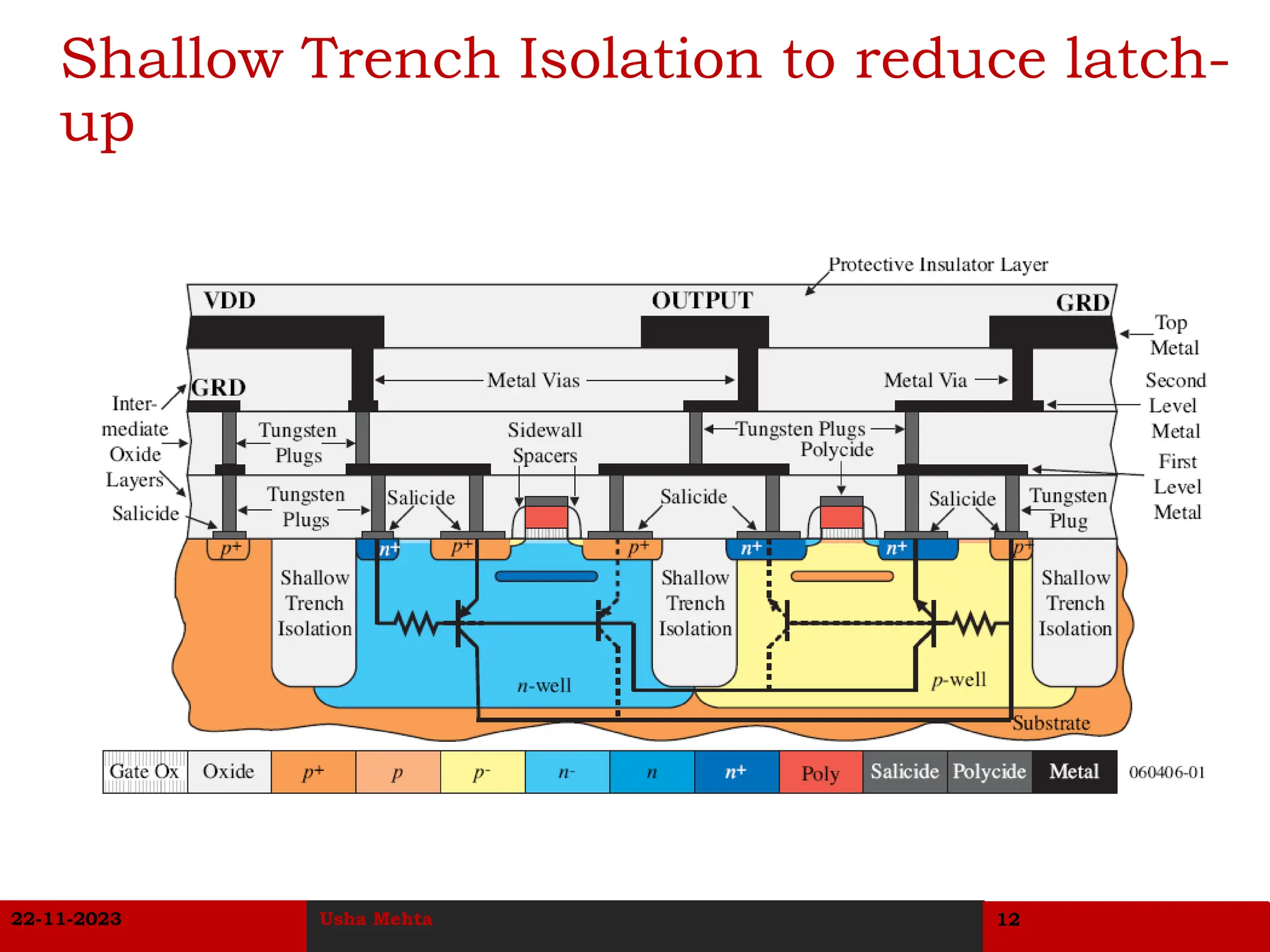

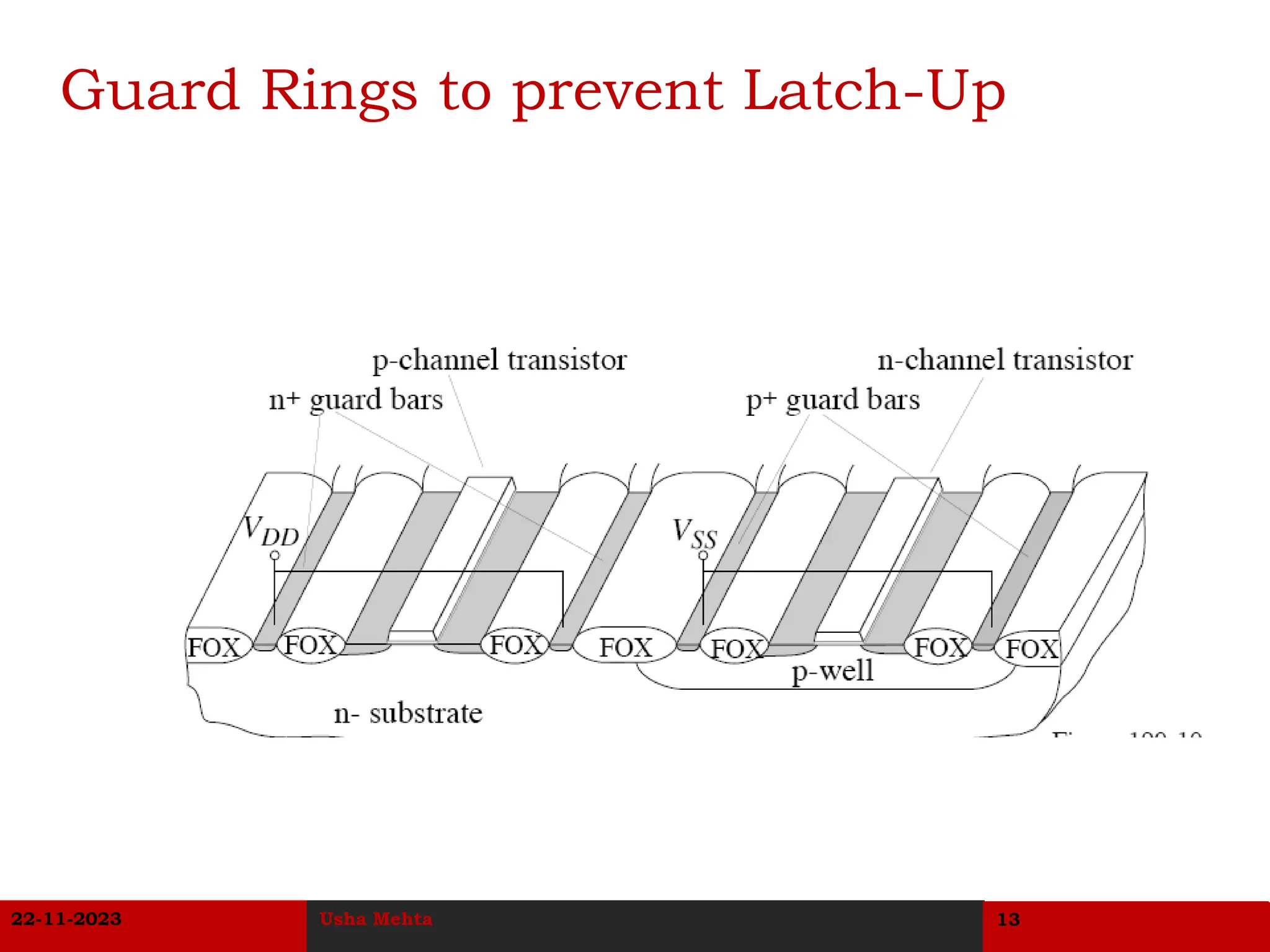

Latch-up occurs in CMOS chips due to the interaction of parasitic bipolar transistors forming a silicon-controlled rectifier with positive feedback. This causes a low impedance path between power and ground rails, risking damage from excessive currents. Latch-up can be prevented by techniques that reduce the gains of the parasitic bipolar junction transistors like guard rings connected to power and ground rails to capture injected minority carriers. Proper layout practices like minimizing well and substrate resistances and avoiding forward biasing of junctions can also help prevent latch-up.