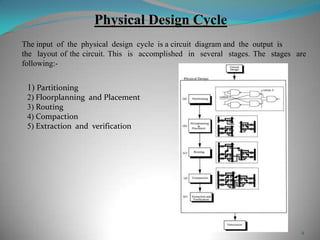

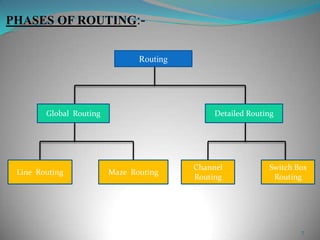

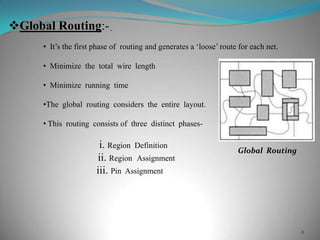

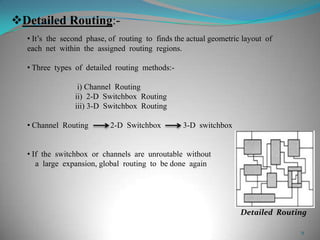

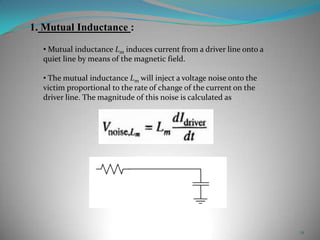

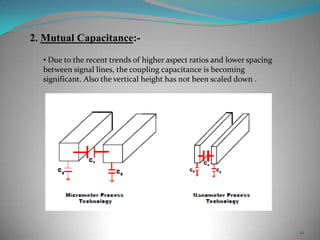

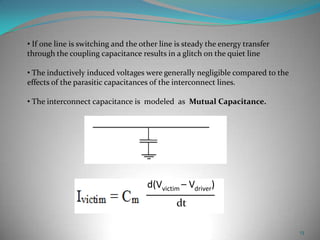

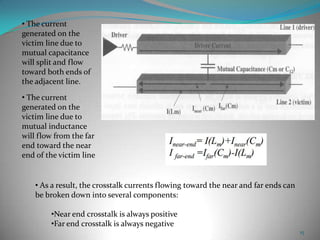

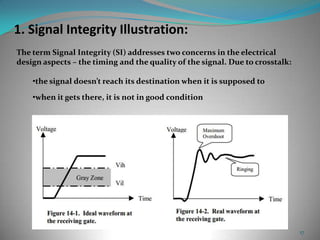

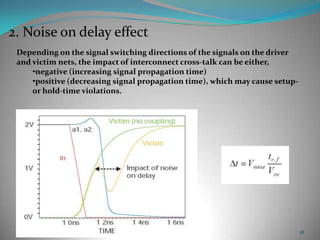

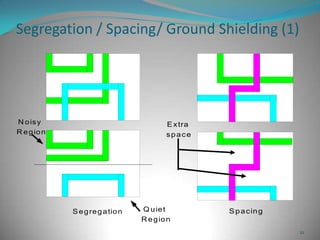

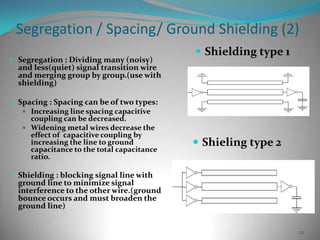

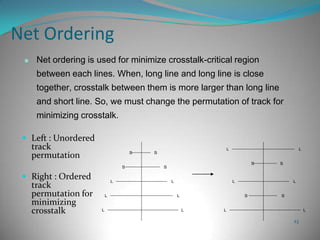

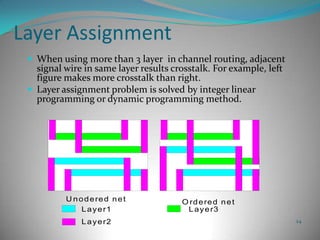

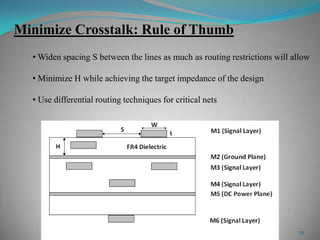

This document summarizes techniques for minimizing crosstalk in VLSI designs. It discusses the VLSI design cycle and physical design cycle. Routing is a key stage that involves global and detailed routing. Crosstalk occurs due to mutual inductance and capacitance between wires and can affect signal integrity, delay, and timing. Basic approaches to reduce crosstalk include segregating wires, increasing spacing between wires, using ground shields, optimizing the net ordering and layer assignments. Specific techniques mentioned are widening spacing, minimizing wire heights and lengths of parallel runs, using differential routing, and routing orthogonal layers.