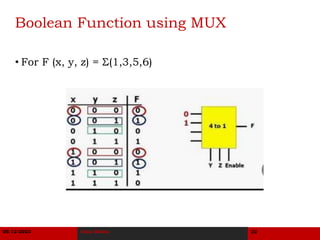

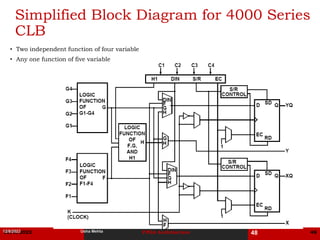

This document discusses FPGA architecture and programming. It begins with an acknowledgement of sources used to create the presentation. It then discusses how FPGA programming differs from microprocessor programming. The document covers the evolution of FPGAs from CPLDs and their advantages over ASICs. It discusses the programmability of FPGAs in logic, interconnects, and input/output. Examples of Xilinx and Altera FPGA architectures are provided. Applications and advantages of FPGAs are also summarized.