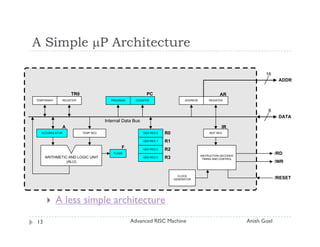

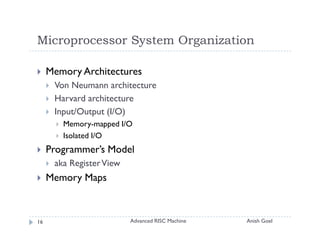

This document discusses the ARM7TDMI microprocessor. It provides an overview of embedded systems and applications, describing how embedded microprocessors account for most microprocessor sales. It also discusses the basic structure of a microprocessor system, including the CPU, memory, I/O, and system bus. The document examines why the ARM architecture was chosen and provides information on the ARM7TDMI implementation, pipeline execution, and performance measures like latency and throughput.