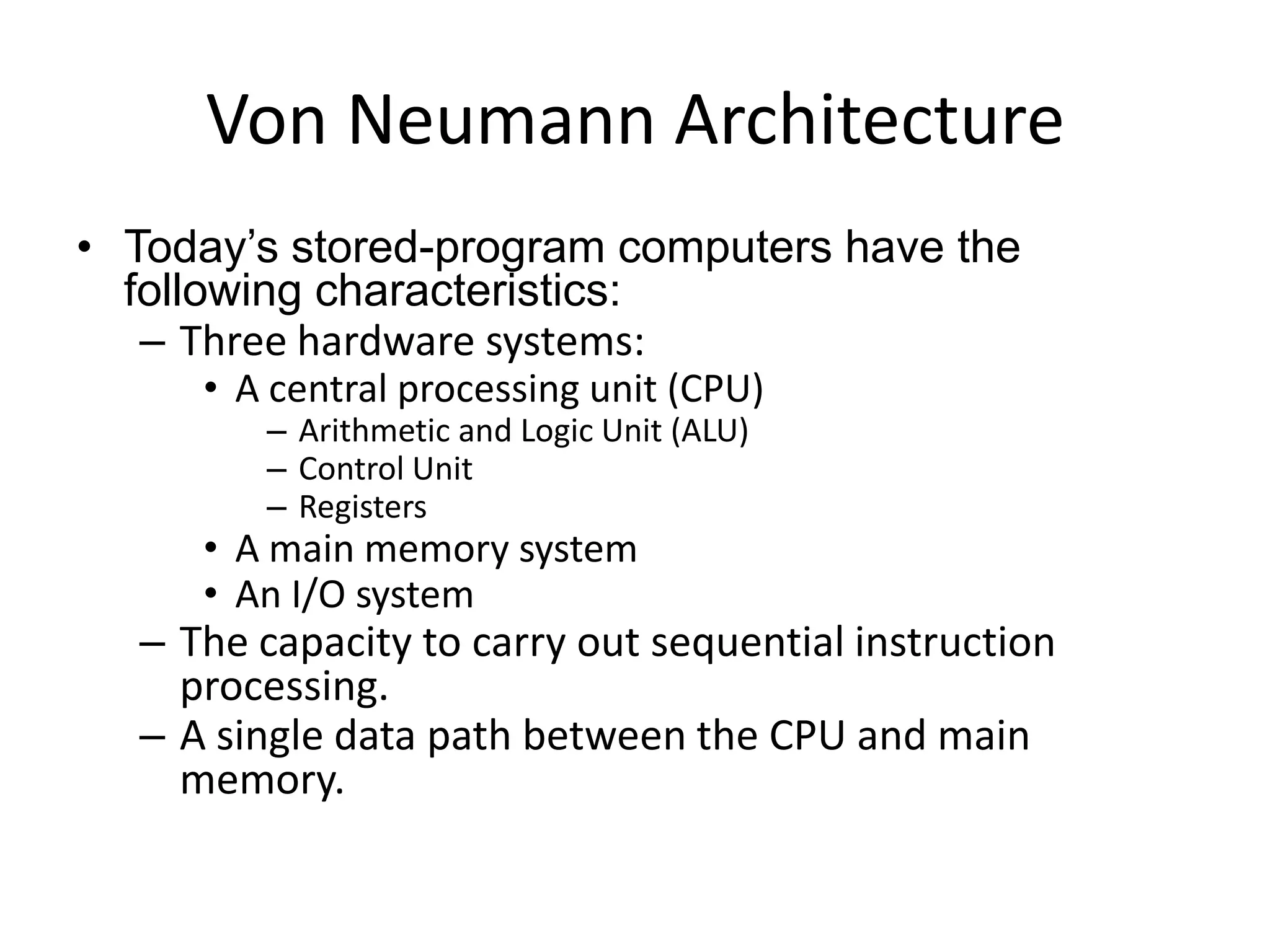

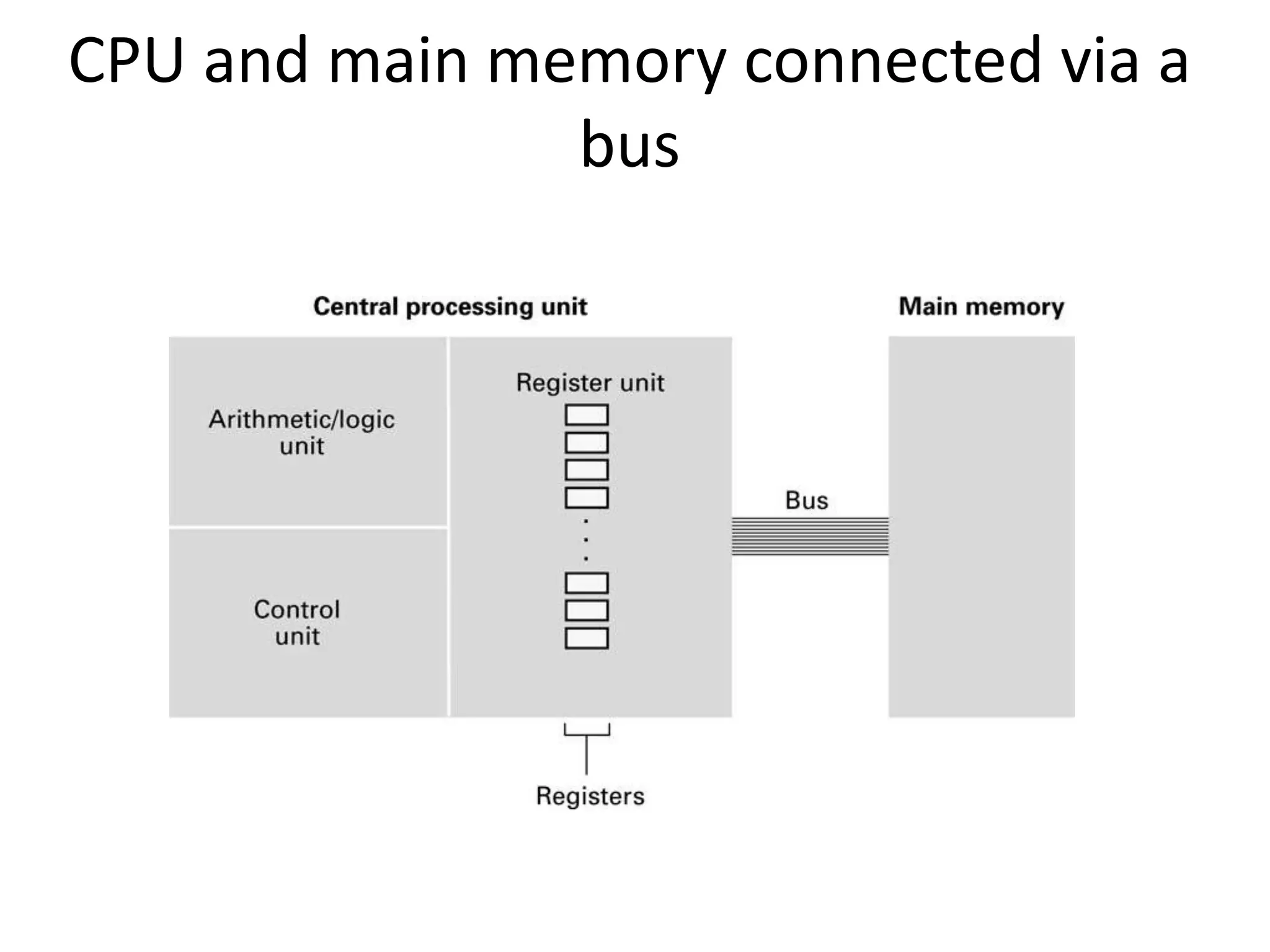

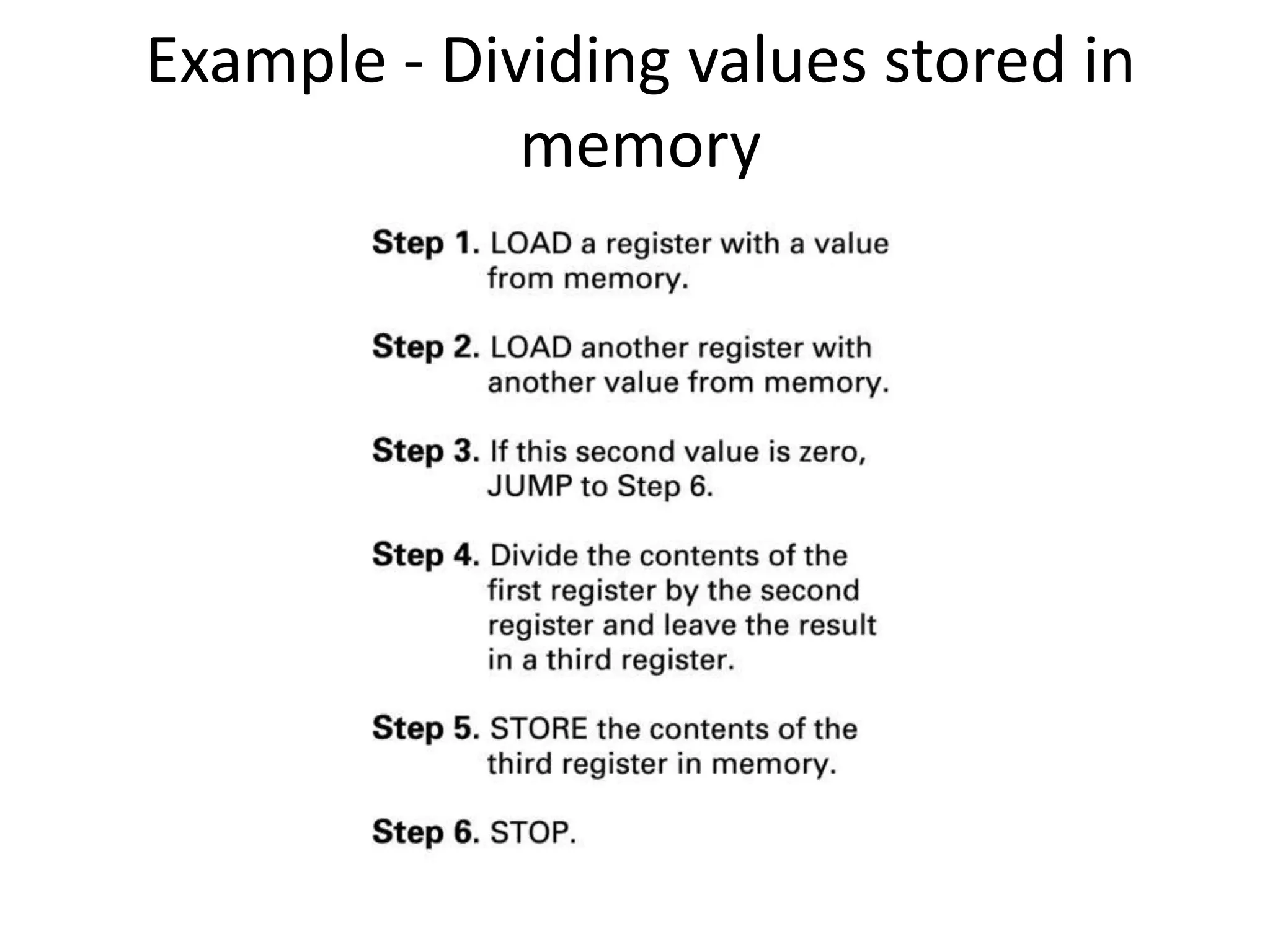

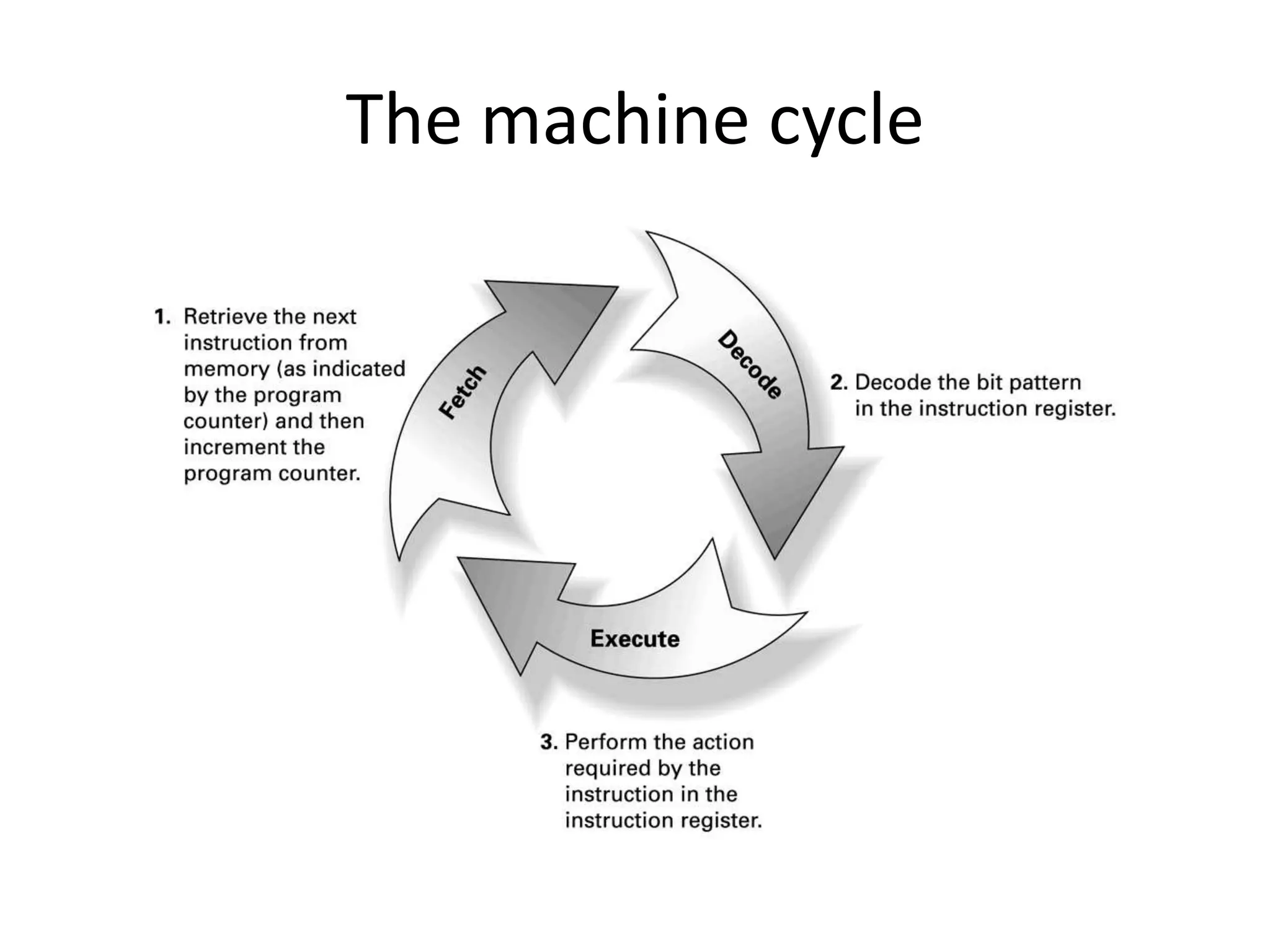

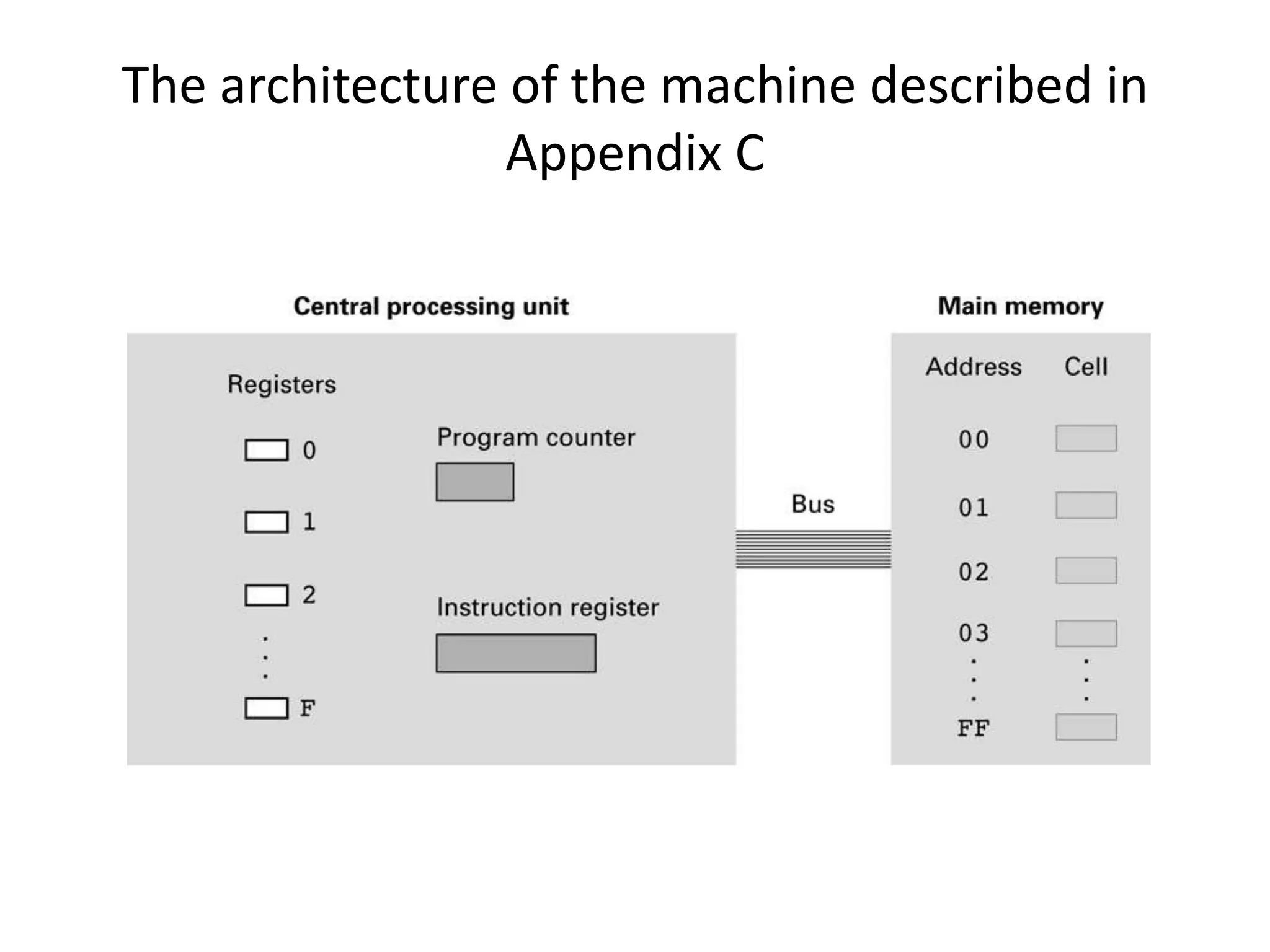

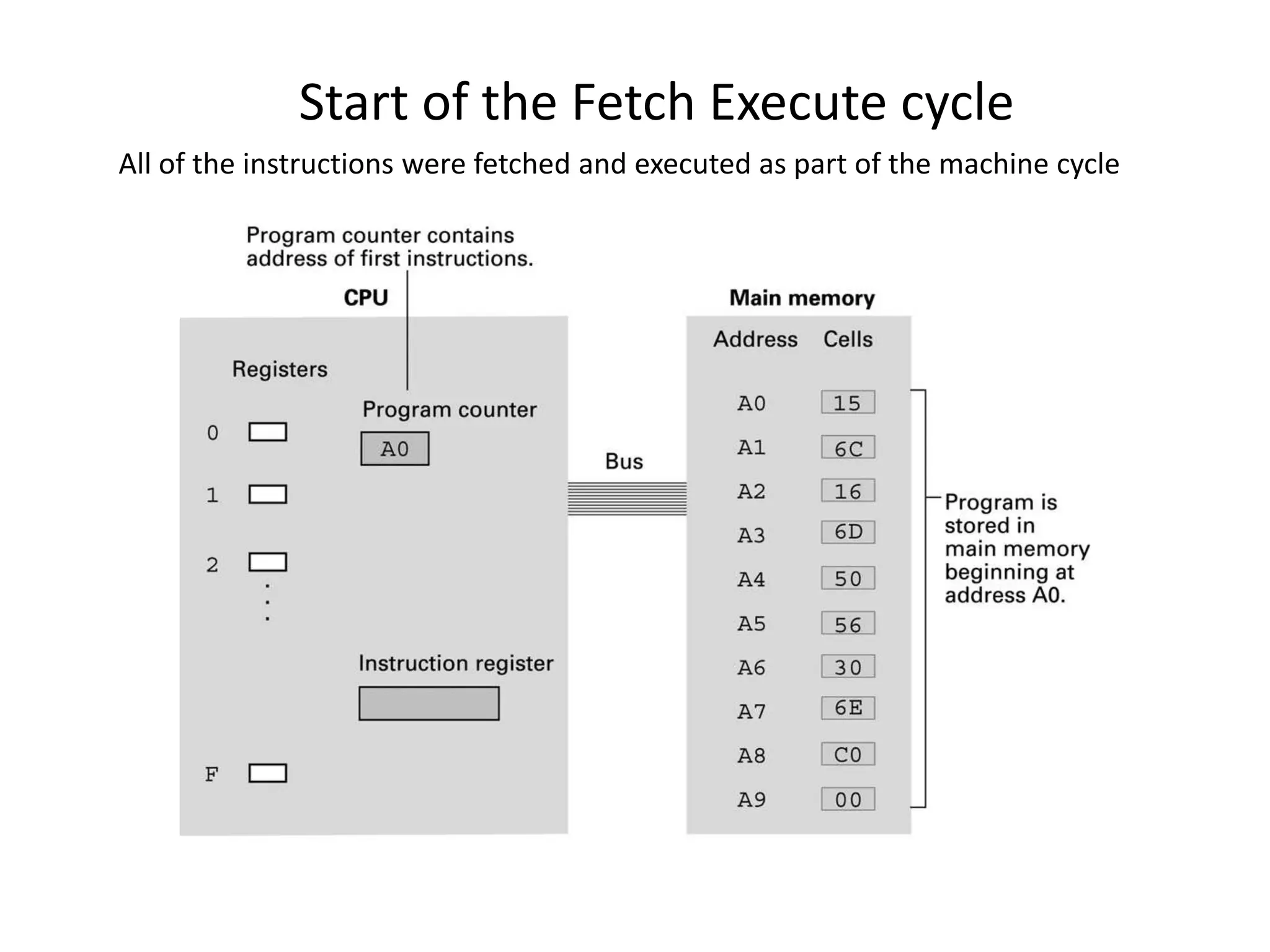

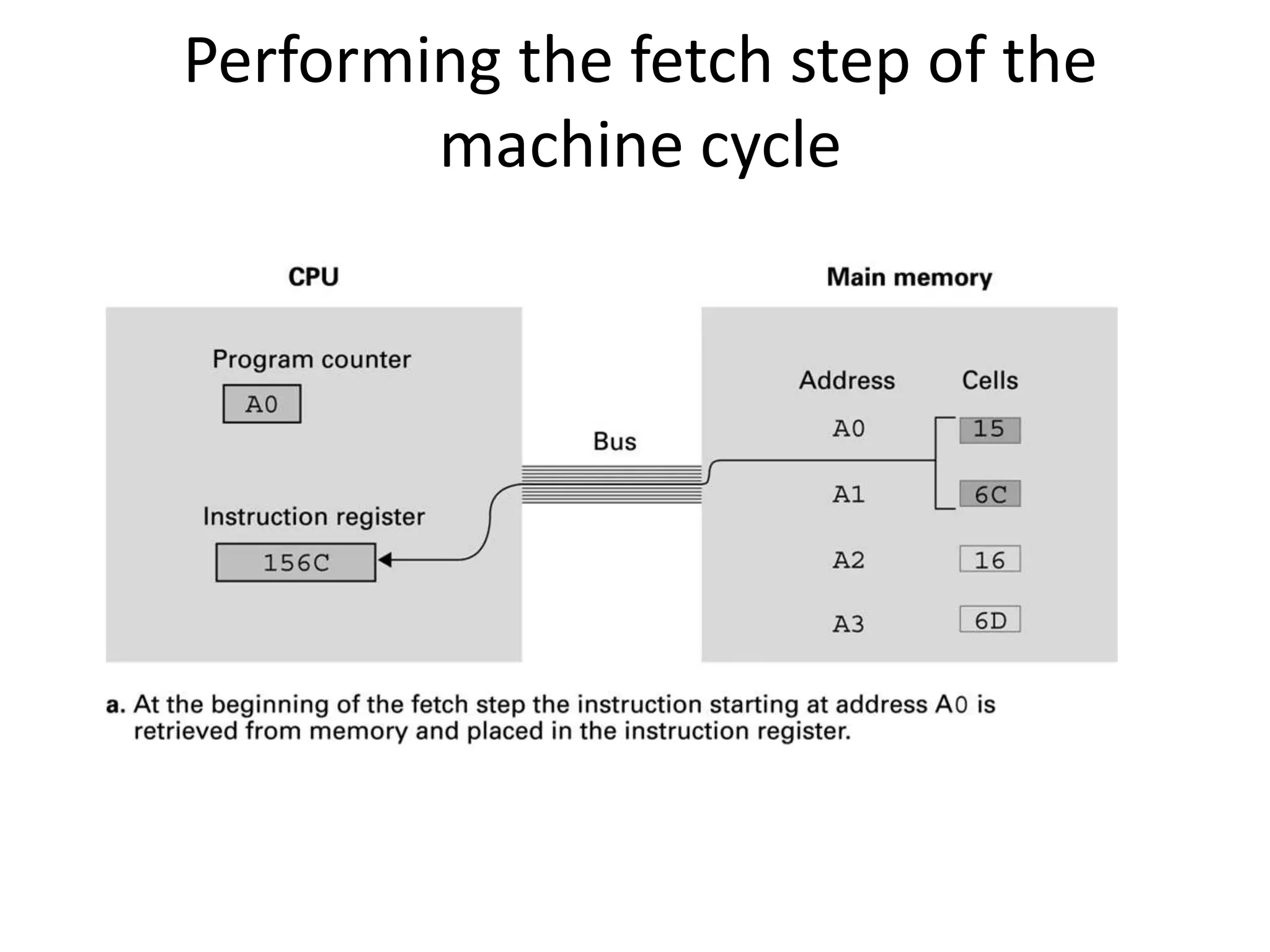

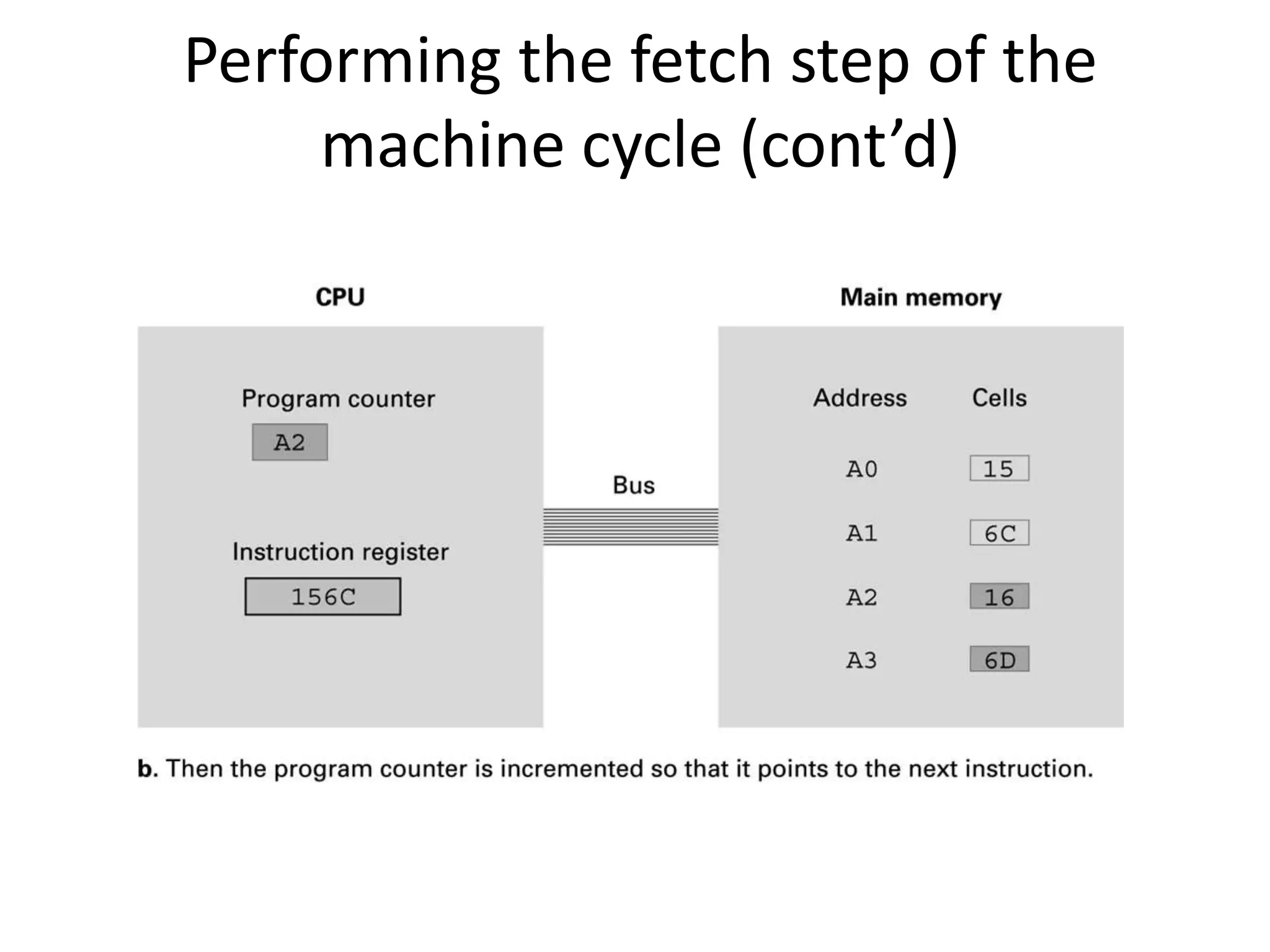

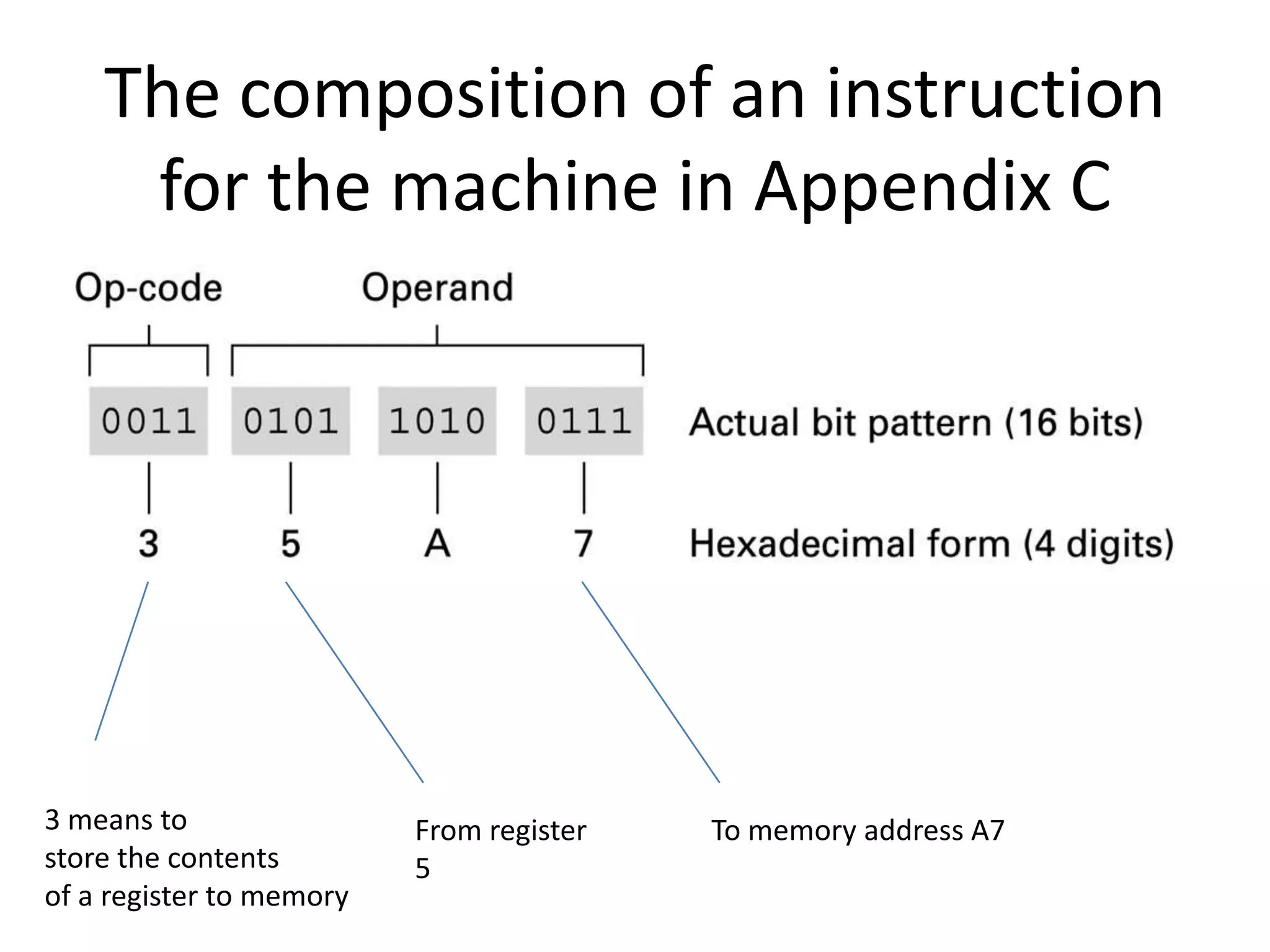

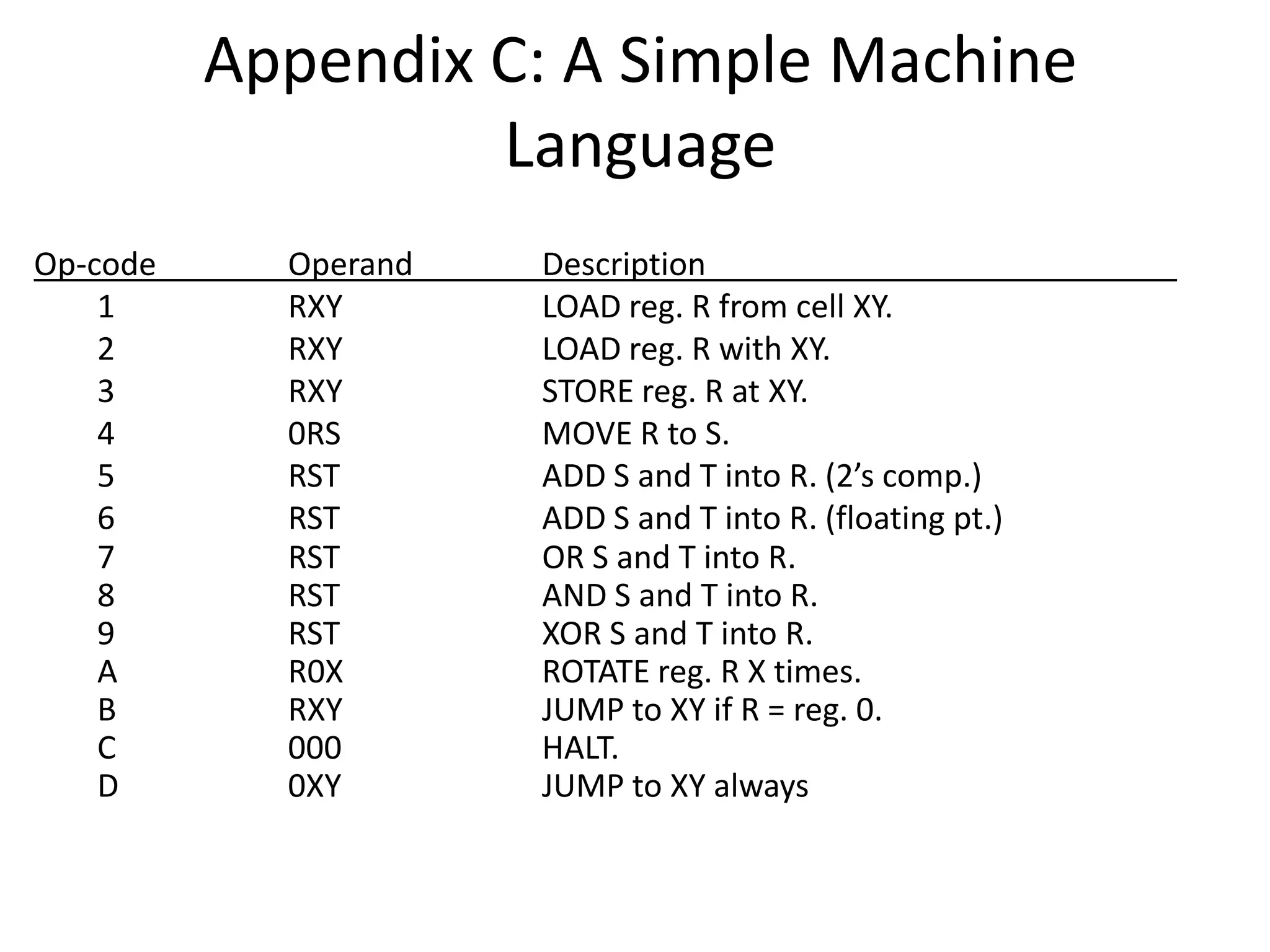

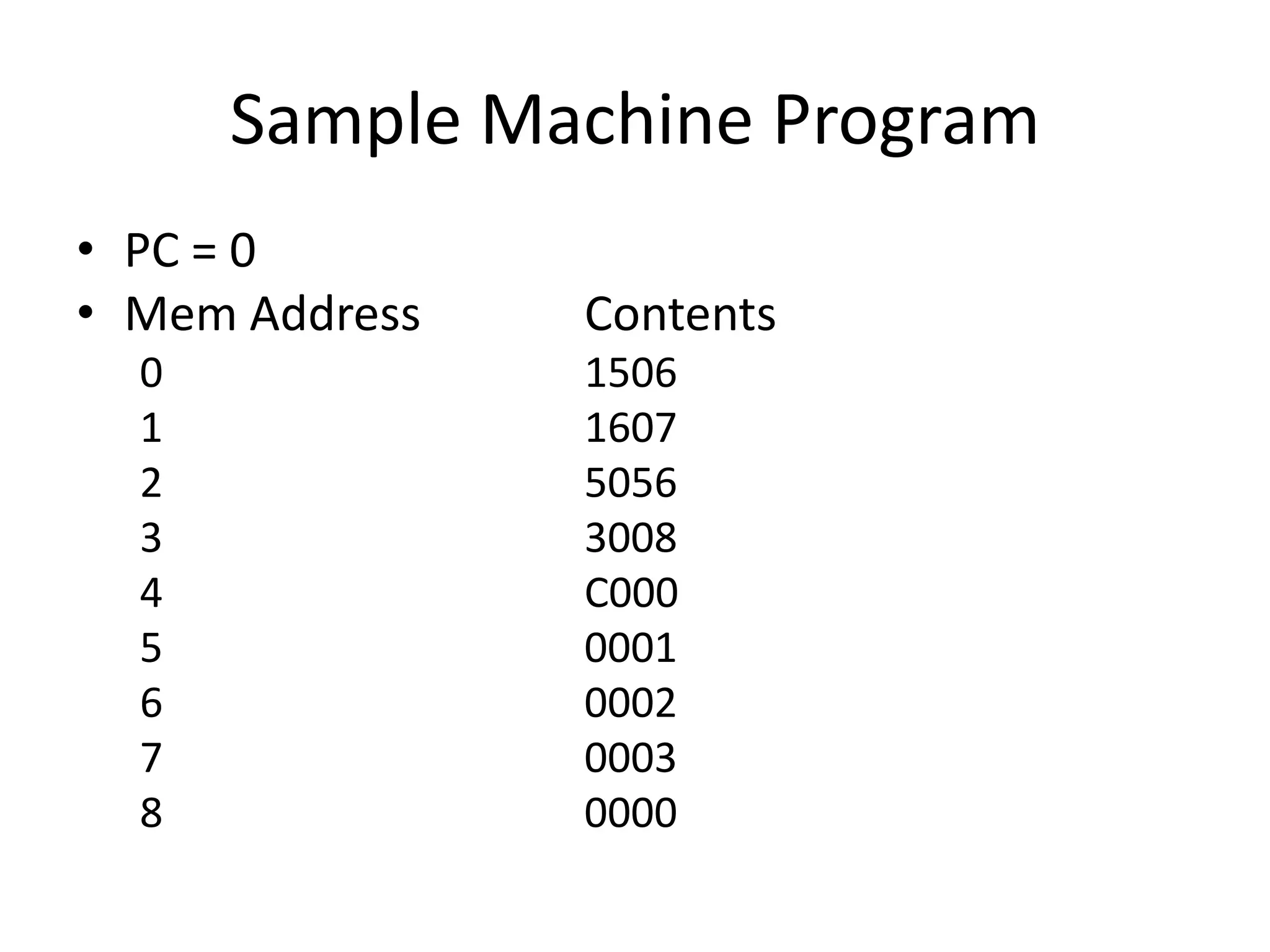

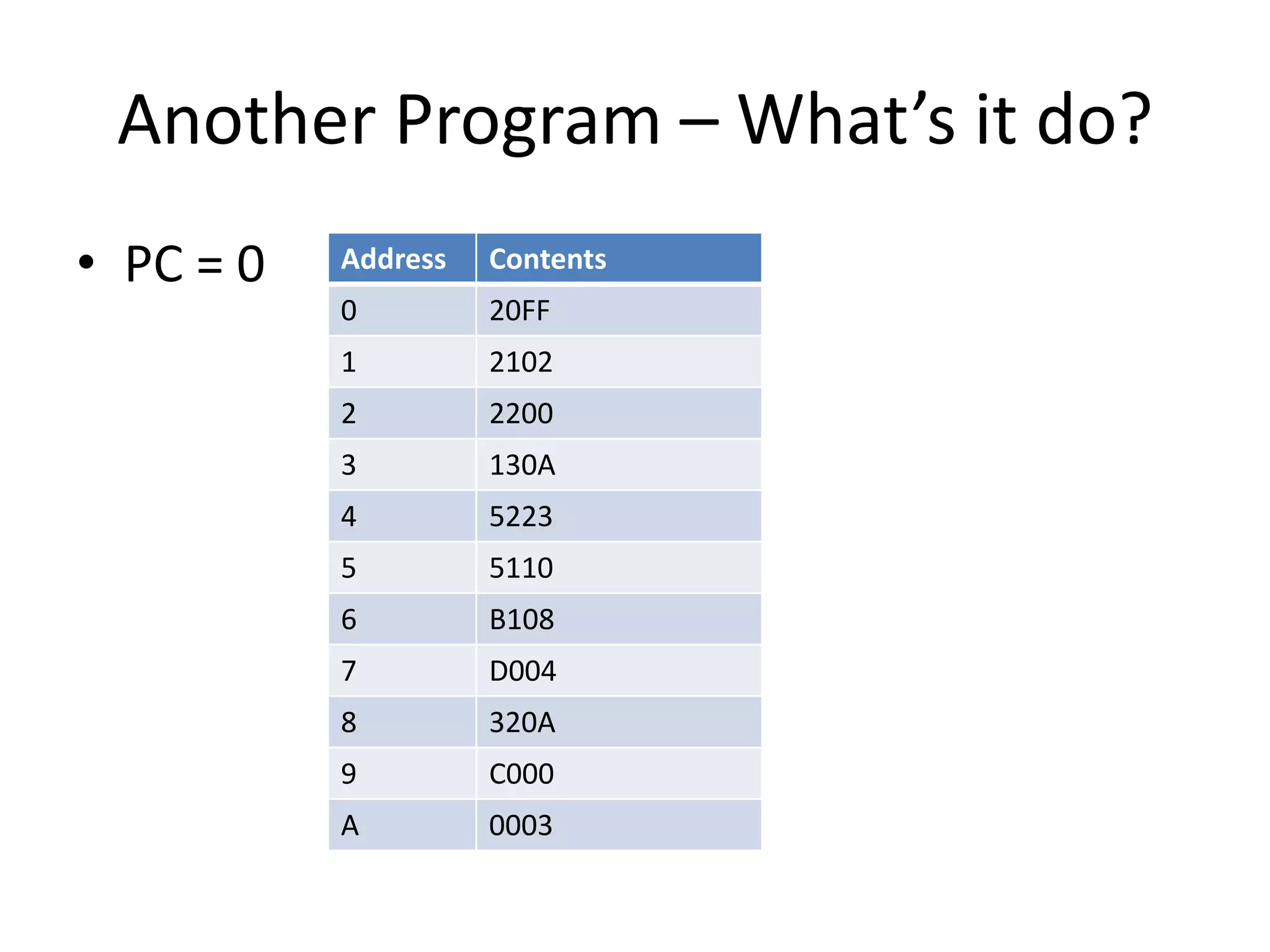

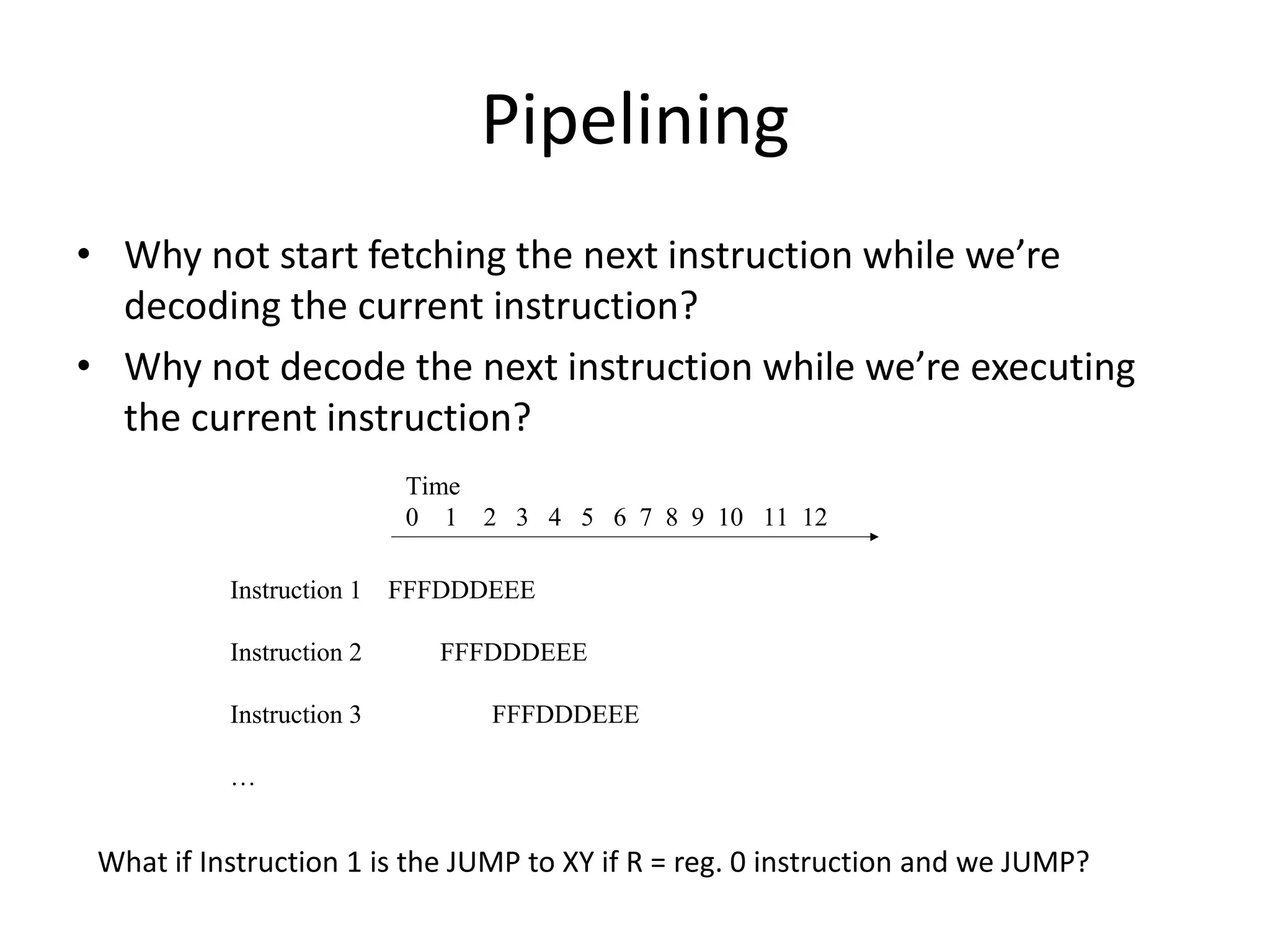

The document describes the Von Neumann architecture of modern computers including the central processing unit (CPU), main memory, and input/output system. It discusses how programs are stored in memory and executed by the CPU through sequential instruction processing. Machine instructions, machine languages, and common instruction types are defined. Examples of instruction execution including data transfer and arithmetic operations are provided. The document also discusses techniques for improving performance including pipelining and parallel processing.