The document discusses the ARM architecture and interrupt handling. It provides background on ARM and compares RISC and CISC architectures. It describes ARM's instruction sets, data sizes, registers including the program counter and current program status register. It discusses exception handling in ARM, including saving state on exception entry and exit. Interrupts and exceptions are compared to system calls. Memory organization during exceptions is also covered.

![- SSM 24-1 [ Na_Min_Yeop ]

- naminyeop@naver.com

ARM Architecture

& Interrupt Handling

http://infocenter.arm.com/help/index.jsp](https://image.slidesharecdn.com/armarchitecture-151012160636-lva1-app6891/75/Arm-architecture-1-2048.jpg)

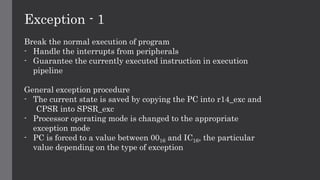

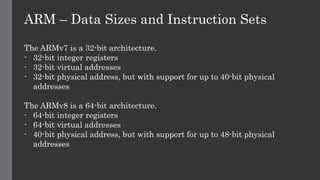

![PC( Program Counter)

When the processor is executing in ARM state:

- All instructions are 32 bits in length

- All instructions must be word aligned

PC value is stored in bits [31:2]

- bits [1:0] equal to zero (word-aligned)

R14 is used as the subroutine link register (LR) and stores the

return address when Branch with Link (BL) operations are

performed, calculated from the PC.

To return from a linked branch

- MOV r15,r14

- MOV pc,lr](https://image.slidesharecdn.com/armarchitecture-151012160636-lva1-app6891/85/Arm-architecture-9-320.jpg)

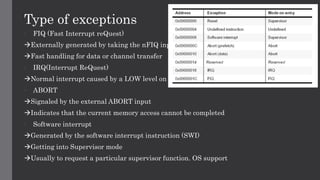

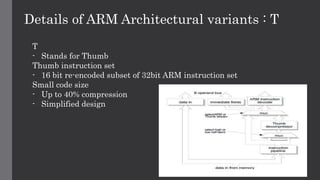

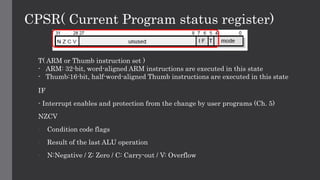

![CPSR( Current Program status register)

Mode: Processor mode

[ ARM7 TDMI ]

- User mode(usr): Normal program execution mode

- Fast Interrupt mode(fiq): Supports a high-speed data transfer or

channel process

- Interrupt mode(irq): Used for general-purpose interrupt

handling

- Supervisor mode(svc): Protected mode for the operating system

- Abort mode(abt): implements virtual memory and/or memory

protection

- System mode(sys): A privileged user mode for the operating

system. (runs OS tasks)

- Undefined mode(und): supports a software emulation of

hardware coprocessors](https://image.slidesharecdn.com/armarchitecture-151012160636-lva1-app6891/85/Arm-architecture-11-320.jpg)

![Understand of Interrupt

In systems programming, an interrupt is a signal to the processor emitted by

hardware or software indicating an event that needs immediate attention. An

interrupt alerts the processor to a high-priority condition requiring the

interruption of the current code the processor is executing. The processor responds

by suspending its current activities, saving its state, and executing

a function called an interrupt handler (or an interrupt service routine, ISR) to

deal with the event. This interruption is temporary, and, after the interrupt

handler finishes, the processor resumes normal activities.[1] There are two types of

interrupts: hardware interrupts and software interrupts.

https://en.wikipedia.org/wiki/Interrupt](https://image.slidesharecdn.com/armarchitecture-151012160636-lva1-app6891/85/Arm-architecture-16-320.jpg)