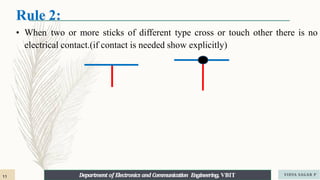

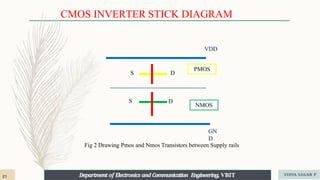

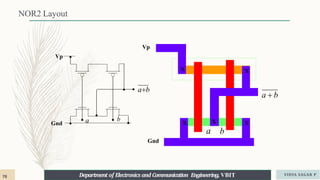

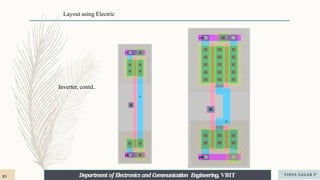

The document discusses VLSI circuit design processes. It covers topics like VLSI design flow, MOS layers, stick diagrams, design rules and layout diagrams. It provides layout diagrams for inverters and logic gates. It also discusses scaling of MOS circuits. Stick diagrams are introduced as a way to show relative placement of transistors without exact sizing or placement details. Design rules for a 2μm CMOS process are presented.