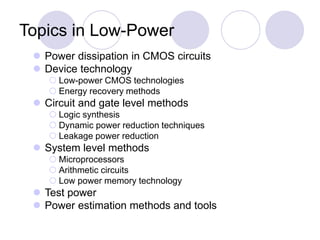

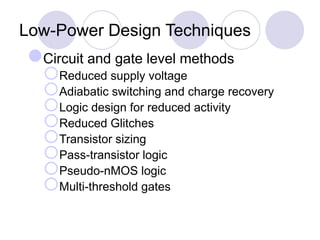

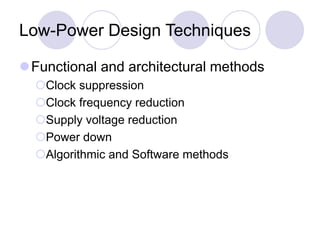

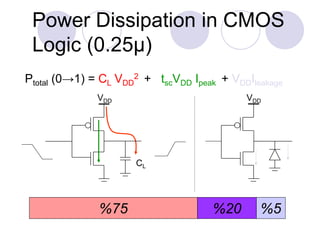

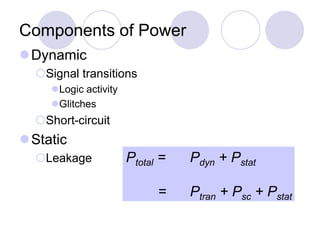

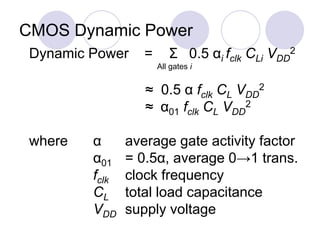

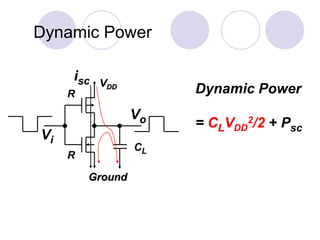

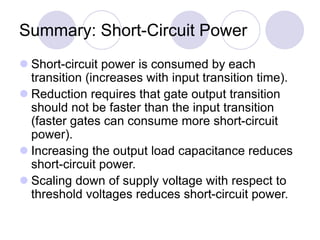

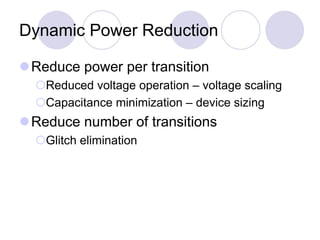

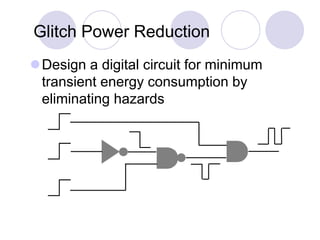

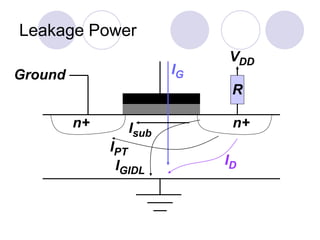

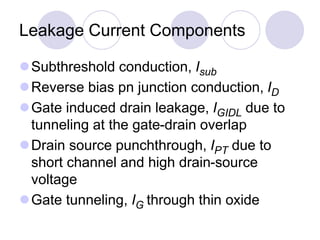

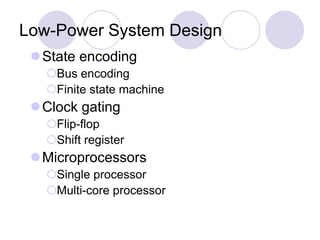

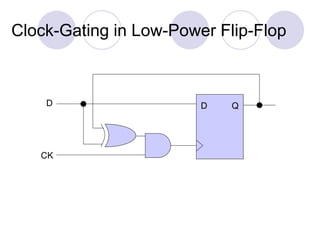

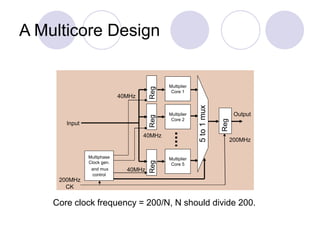

This document discusses various methods for low power design in VLSI circuits. It covers reducing dynamic and static power sources. Dynamic power is lowered through reducing supply voltage, glitch elimination, and minimizing switching activity. Static leakage power is decreased using multi-threshold devices. System level techniques include clock gating, multiple cores, and state encoding to reduce power. Challenges in low power design are also addressed.