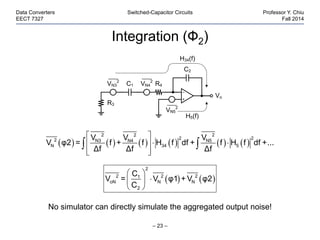

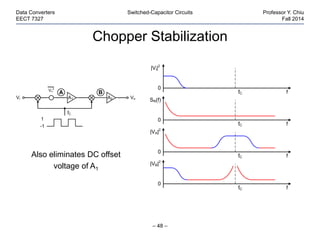

This document discusses switched-capacitor circuits. It begins by introducing the concept of using switched capacitors to emulate resistors and implement functions like integration. It then provides examples of basic switched-capacitor circuits like integrators. It discusses issues like noise and non-ideal effects in switched-capacitor circuits. It also provides examples of applications that use switched-capacitor circuits, such as filters, sigma-delta modulators, and pipelined ADCs.