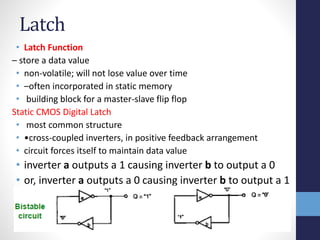

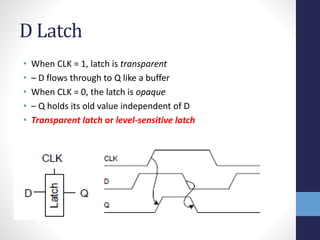

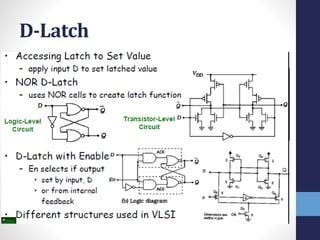

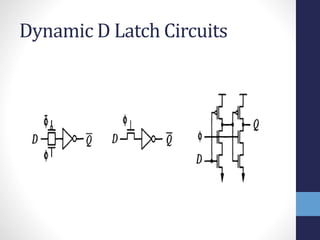

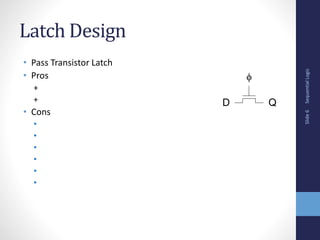

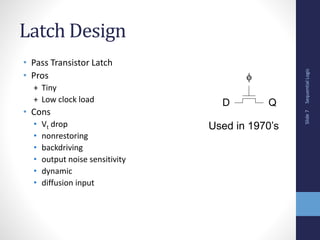

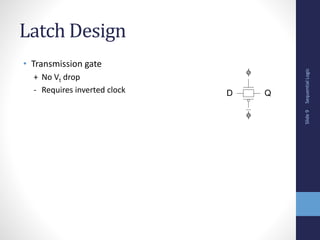

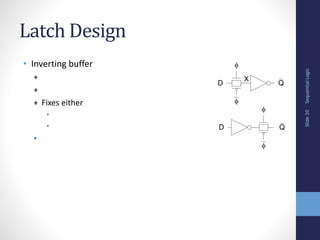

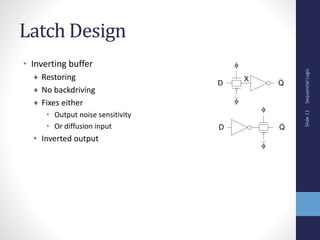

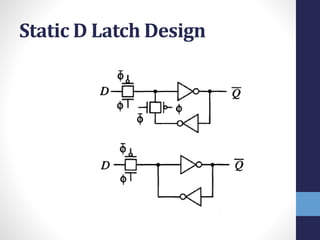

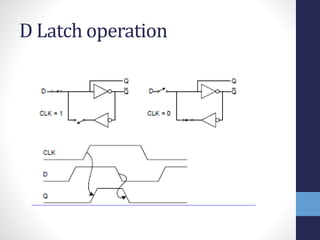

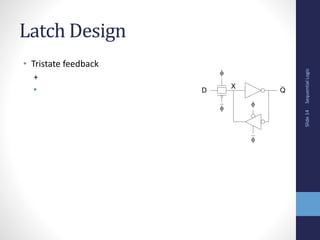

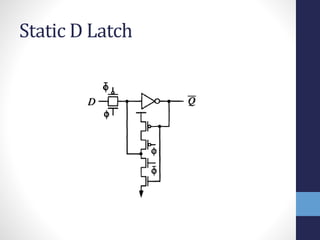

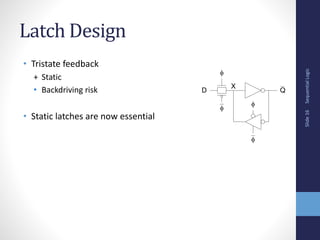

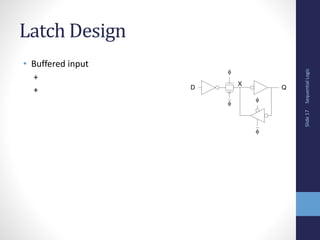

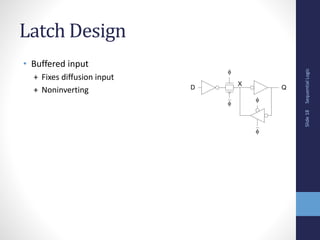

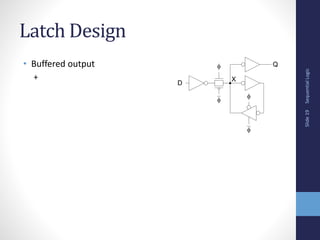

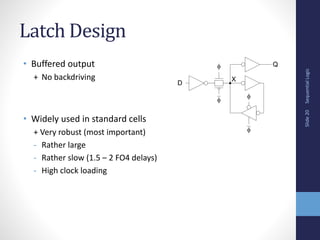

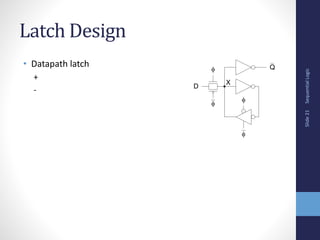

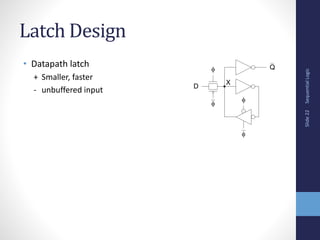

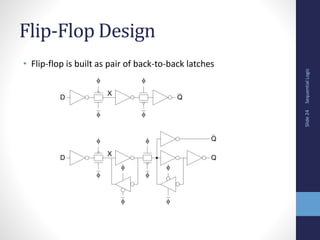

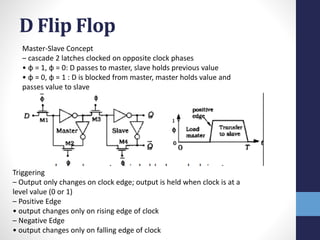

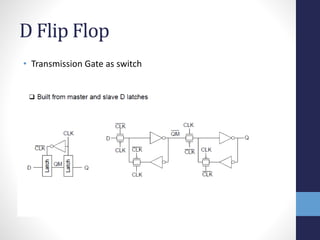

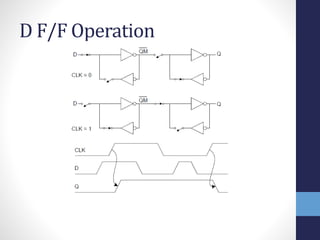

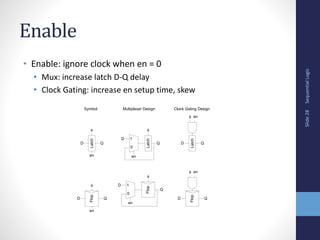

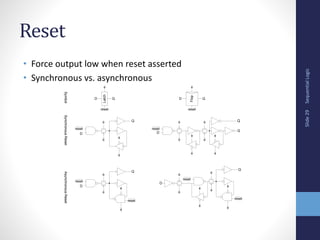

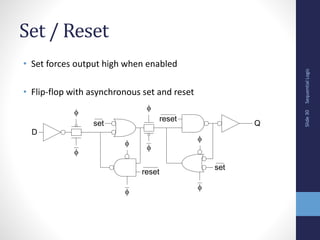

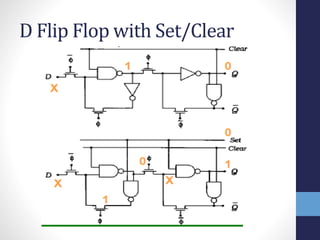

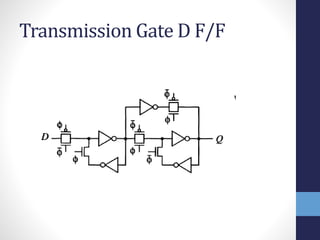

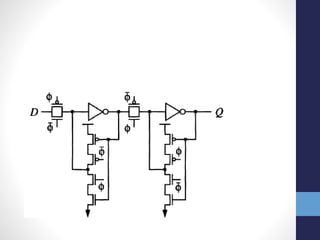

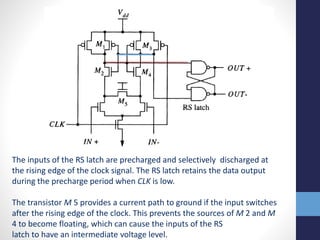

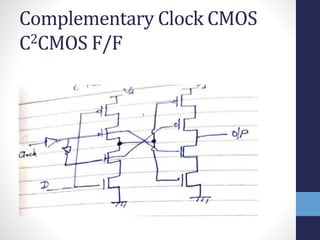

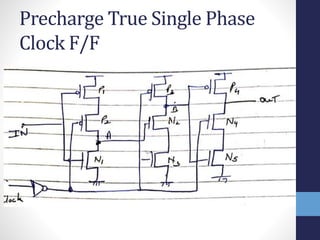

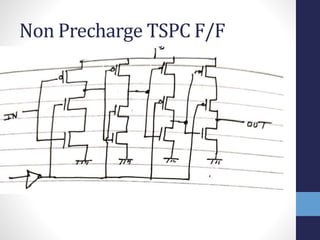

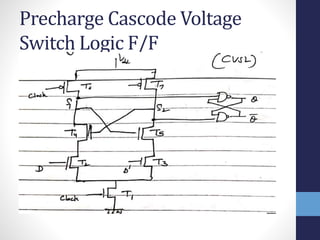

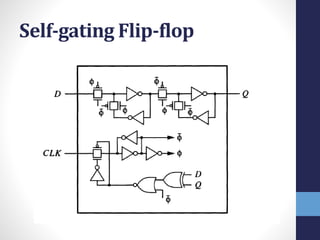

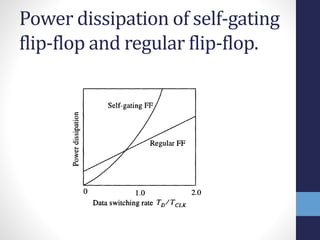

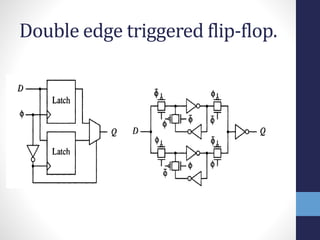

The document discusses latches and flip-flops. It describes how a latch stores a data value and is non-volatile, while a flip-flop is built from two back-to-back latches clocked on opposite phases. Various latch and flip-flop circuit designs are presented, including pass transistor, transmission gate, buffered input/output, and master-slave designs. Features like enables, resets, and sets are also discussed along with their synchronous and asynchronous implementations in flip-flops. Different flip-flop circuit styles are covered such as transmission gate, complementary CMOS, precharge, and self-gating designs.