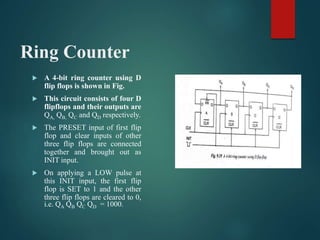

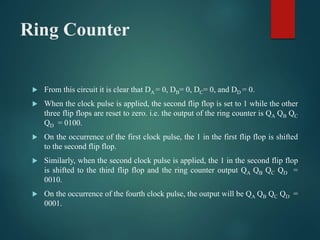

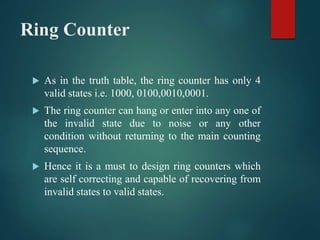

This document describes a ring counter circuit using D flip-flops. A ring counter consists of flip-flops connected in a loop such that a single '1' circulates around the flip-flops as long as a clock signal is applied. The document explains that in a 4-bit ring counter, the output shifts from 1000 to 0100 to 0010 to 0001 and then back to 1000 with each clock pulse as the '1' circulates through the flip-flops. It also notes that a ring counter can enter an invalid state due to noise but should be designed to self-correct back to the valid counting states.