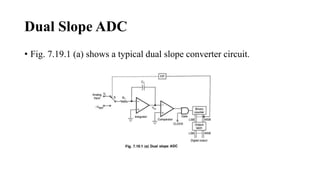

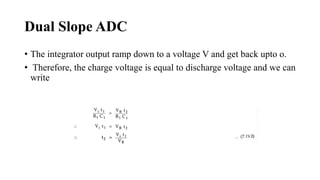

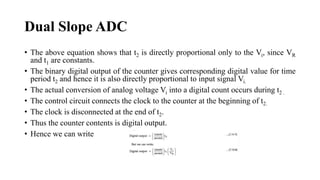

The document describes the operation of a dual slope analog-to-digital converter (ADC). It consists of an integrator, comparator, counter, and reference voltage. In dual slope ADC, the analog input voltage is integrated for a fixed time and compared against the counter. Then, a reference voltage is integrated in the opposite direction until the integrator output reaches zero, at which point the counter value represents the digital output. The speed is slow but accuracy is high, as it corrects for drifts in the integrator.