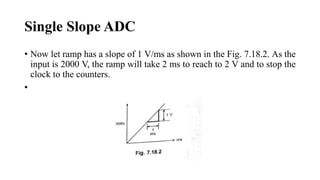

- Single slope ADCs consist of a ramp generator and counters. The analog input is compared to a ramping reference voltage from the generator.

- When the reference voltage exceeds the input voltage, the comparator output changes, stopping the clock to the counters.

- The latched counter value is then displayed, with the number representing the input voltage. For example, an input of 2.000V would cause the ramp to exceed the voltage after 2ms, resulting in a counter value of 2000 being displayed.