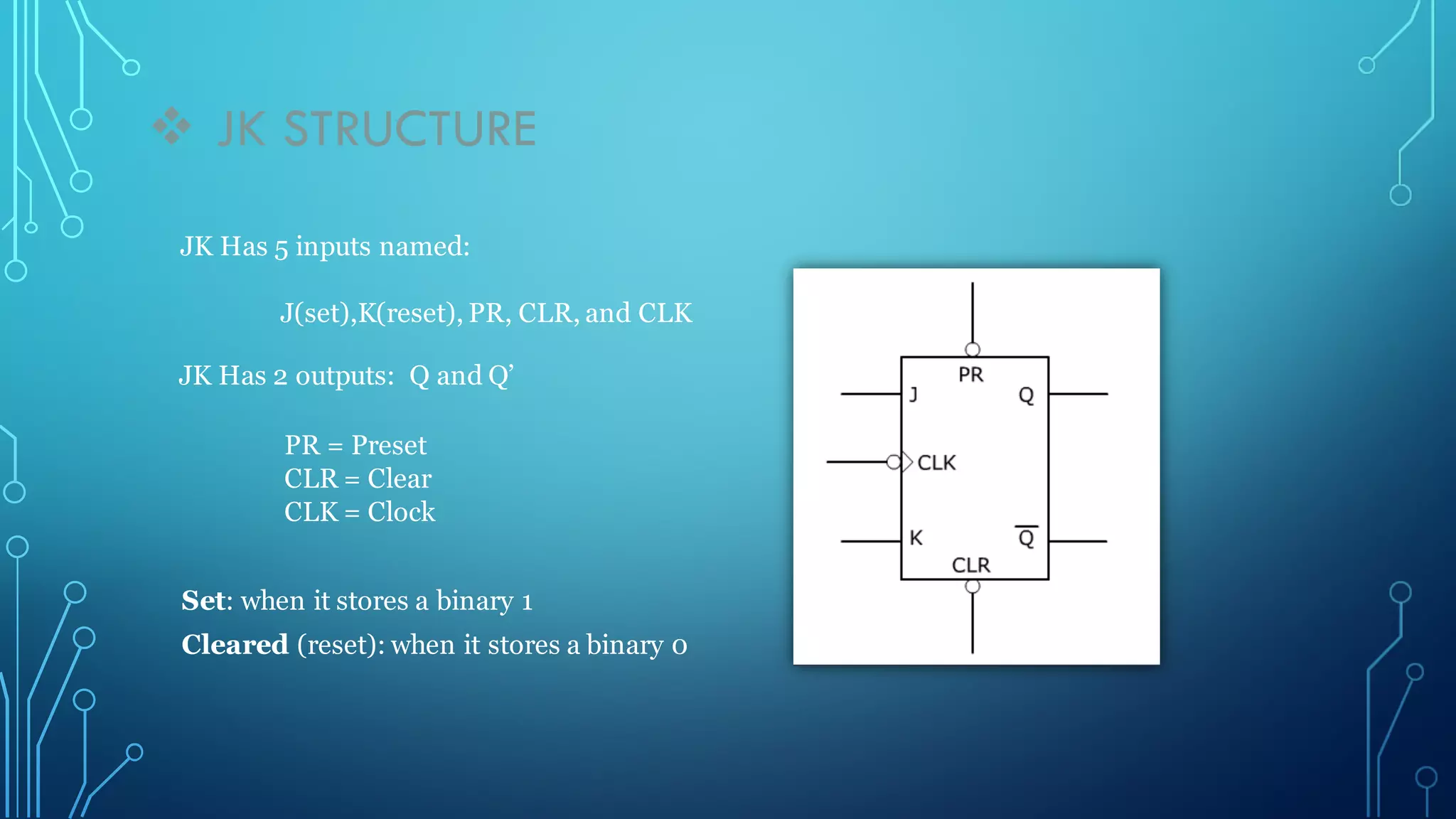

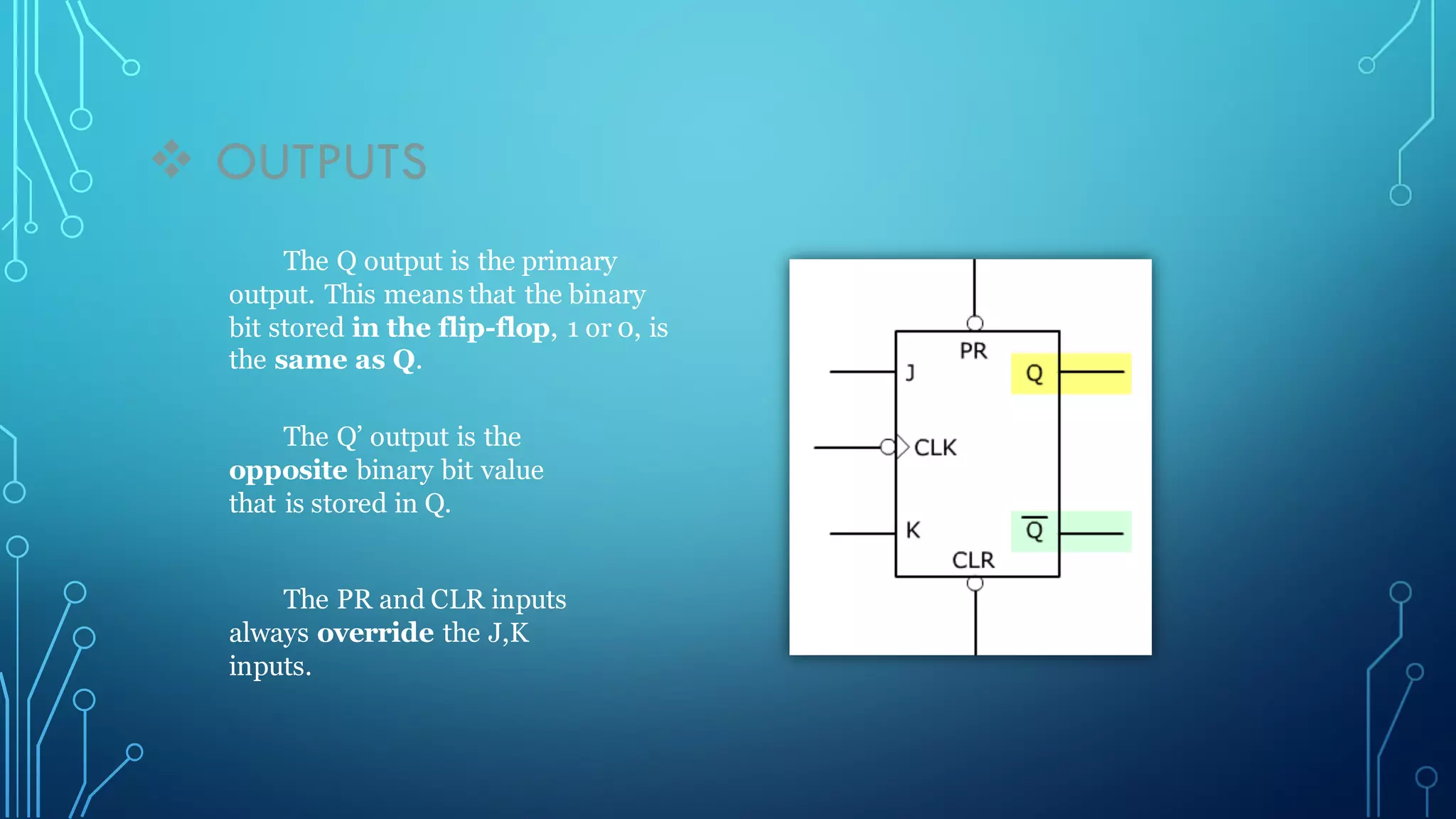

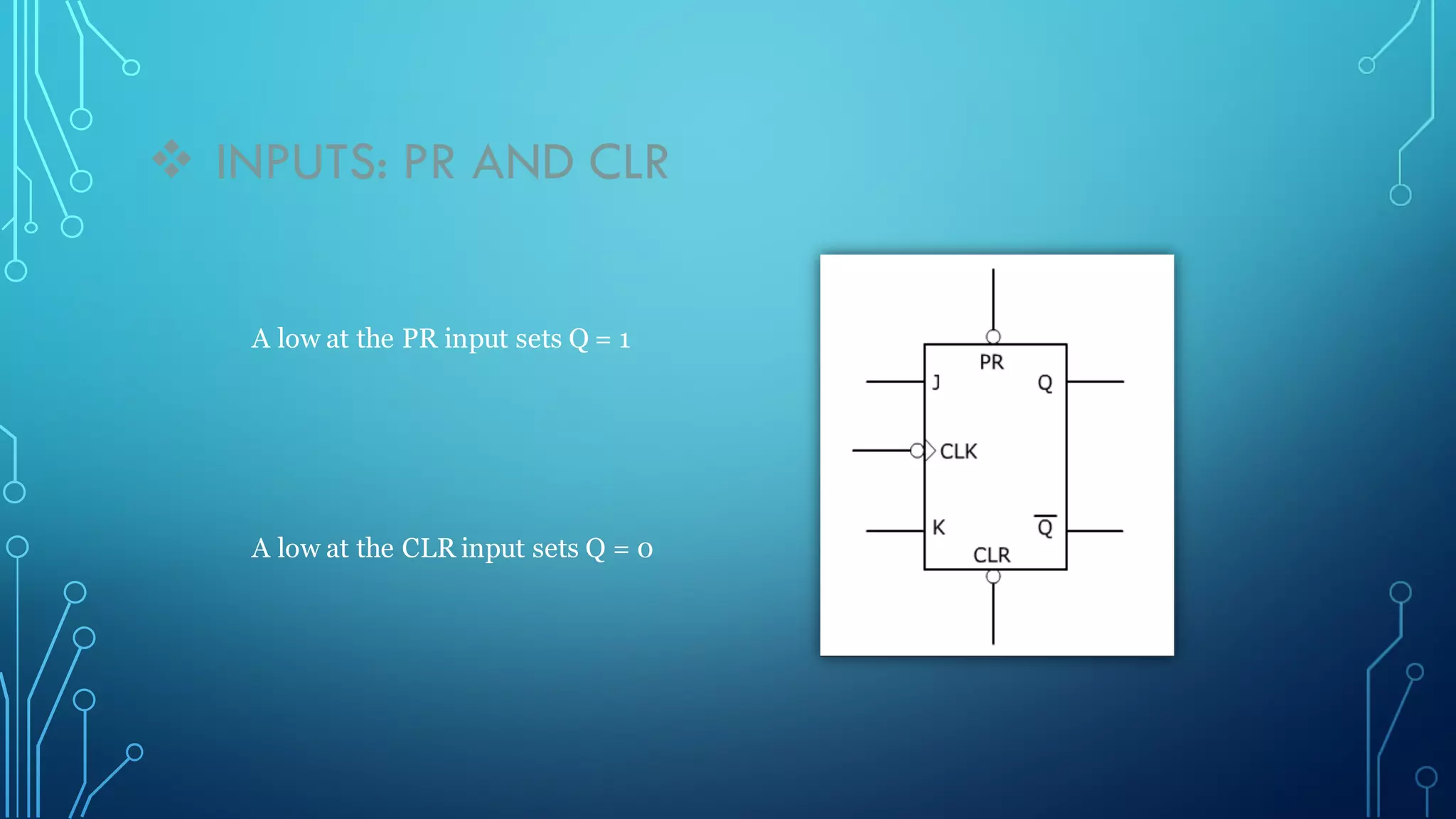

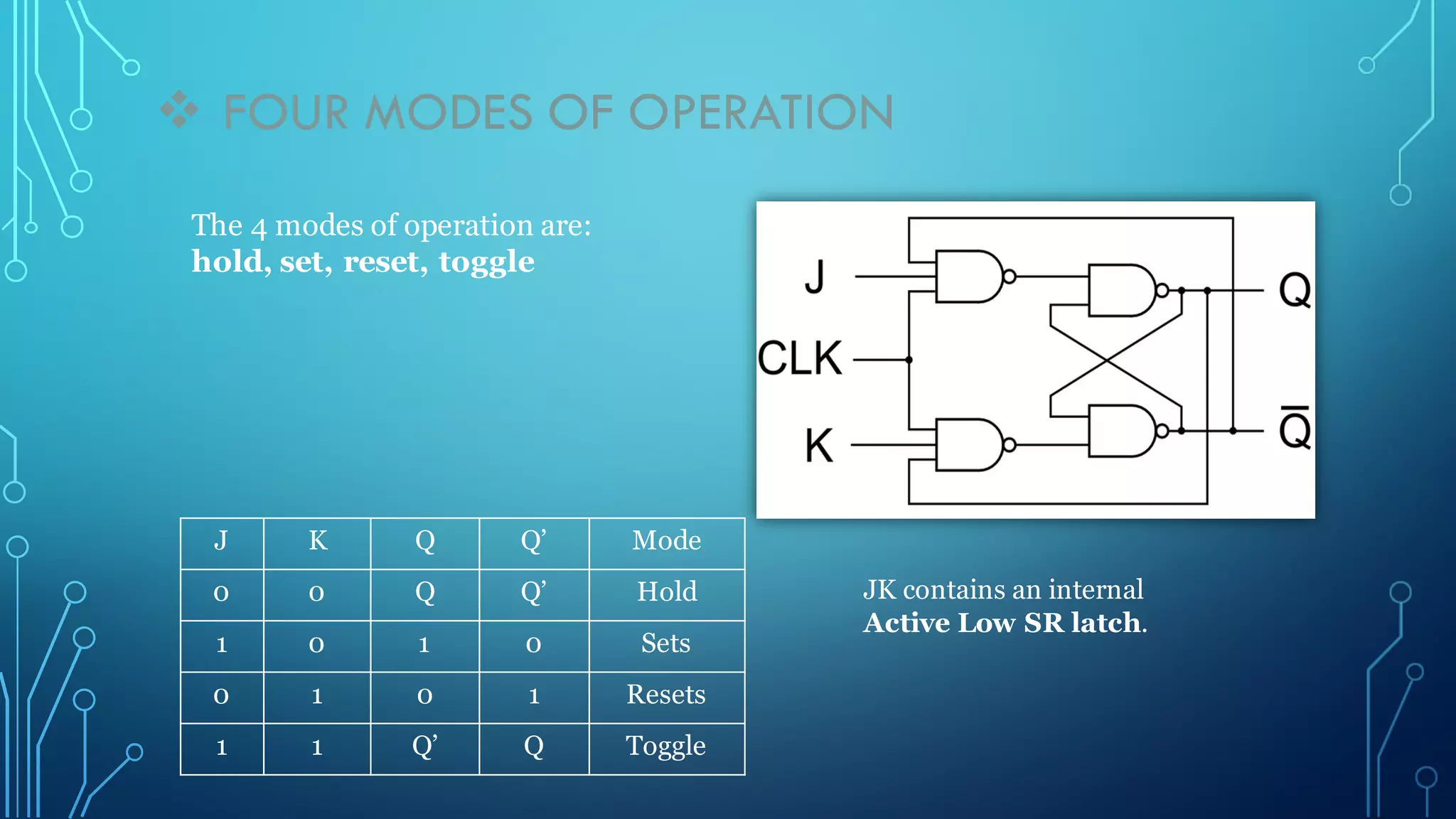

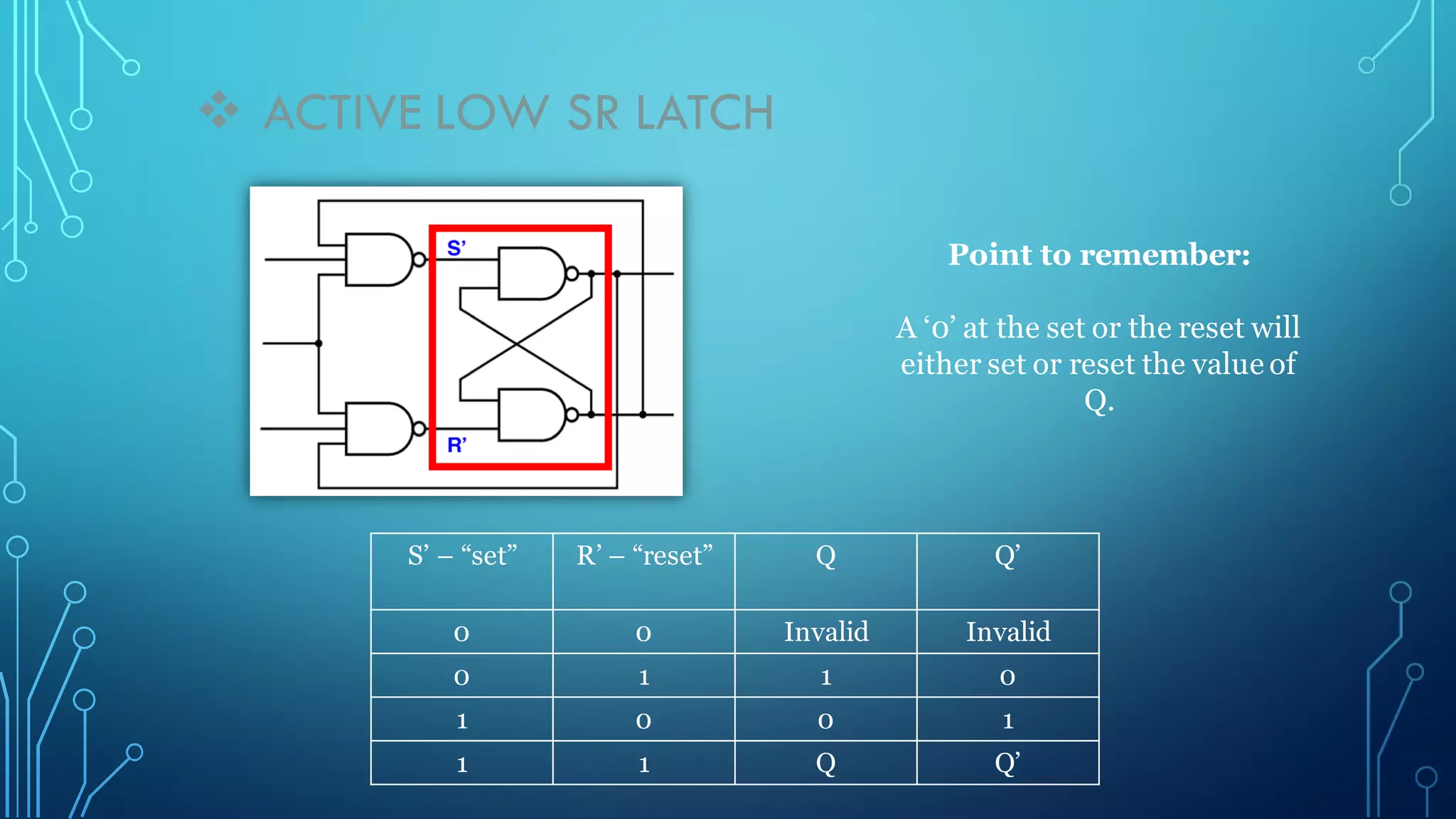

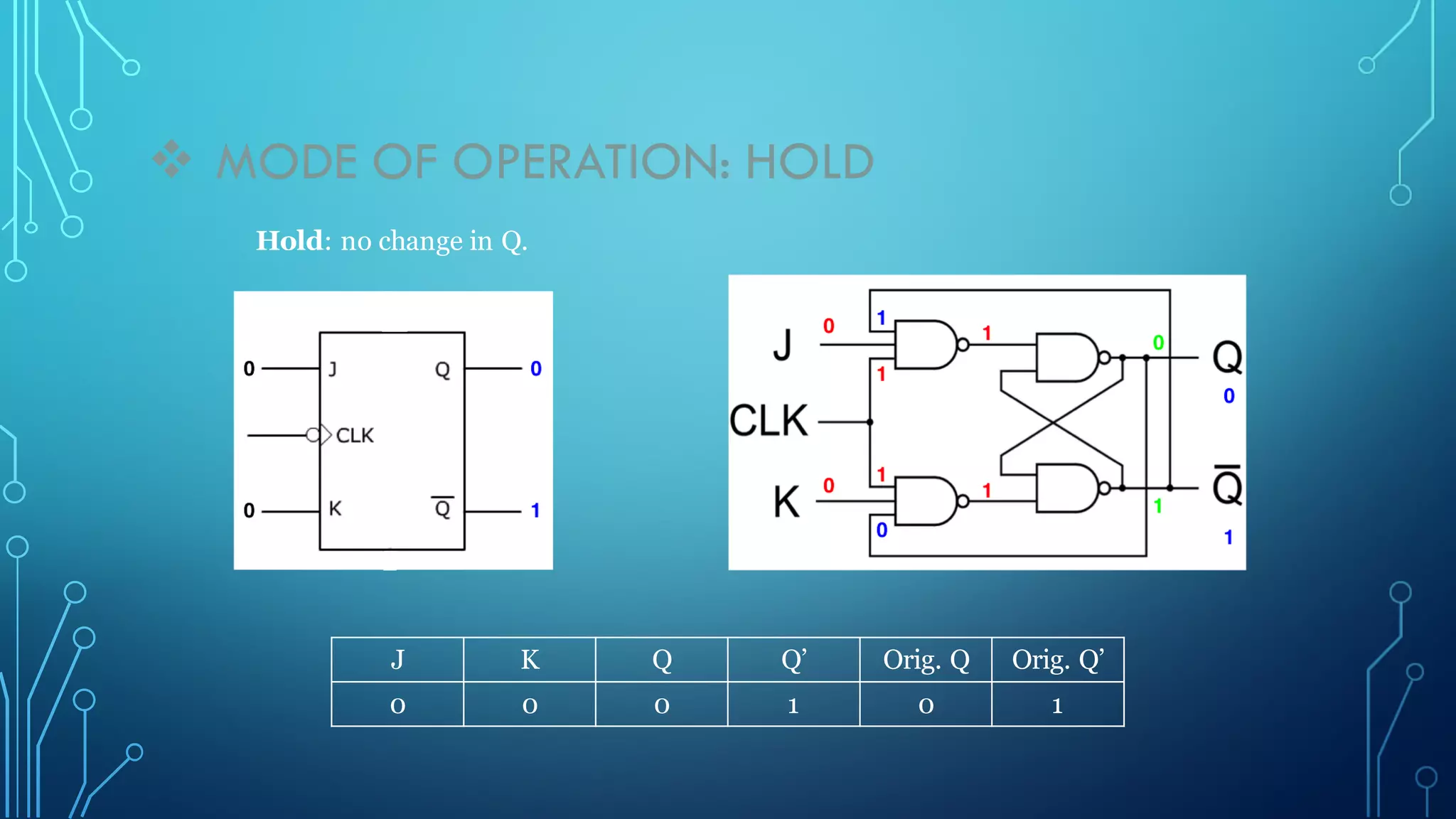

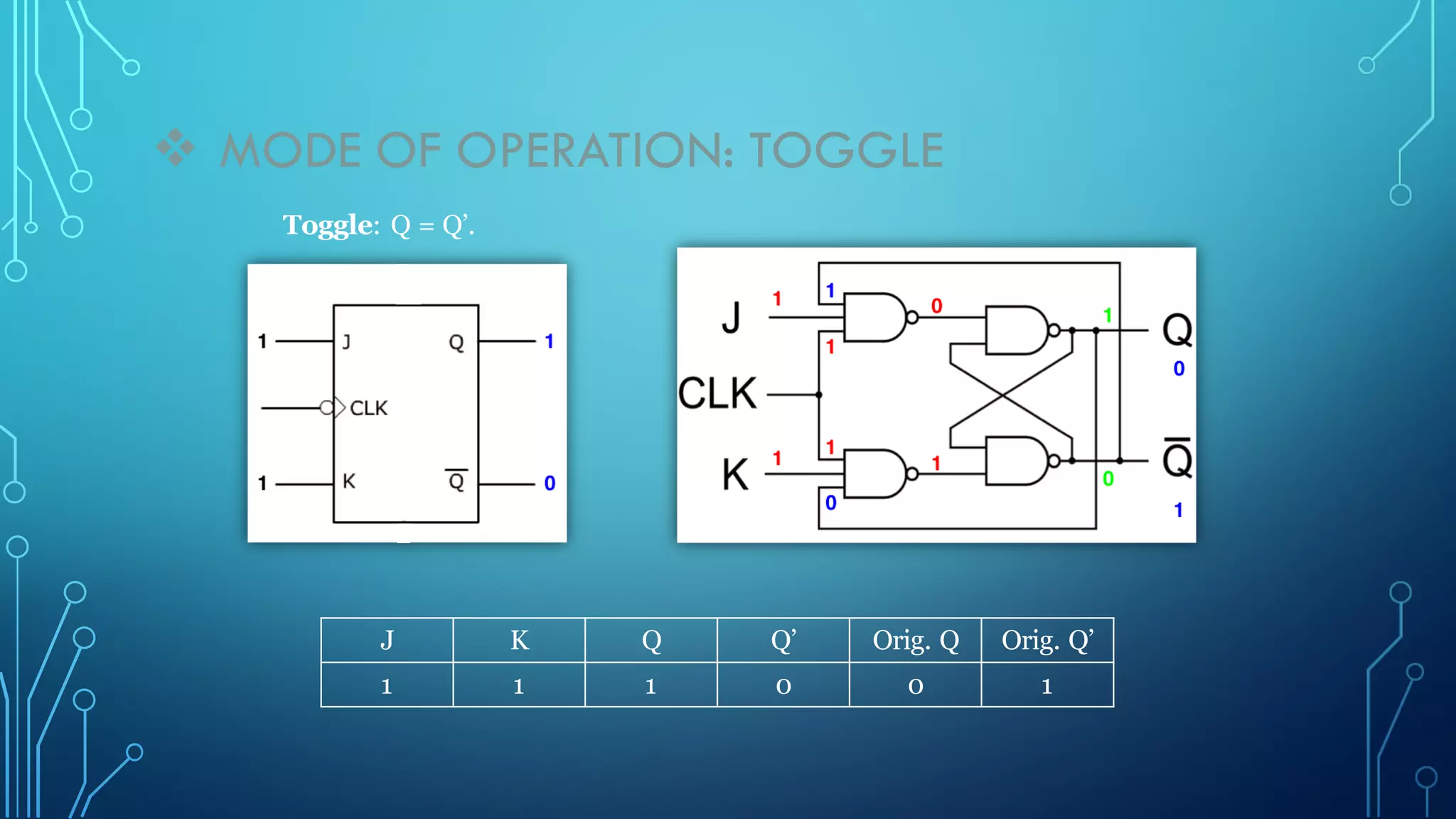

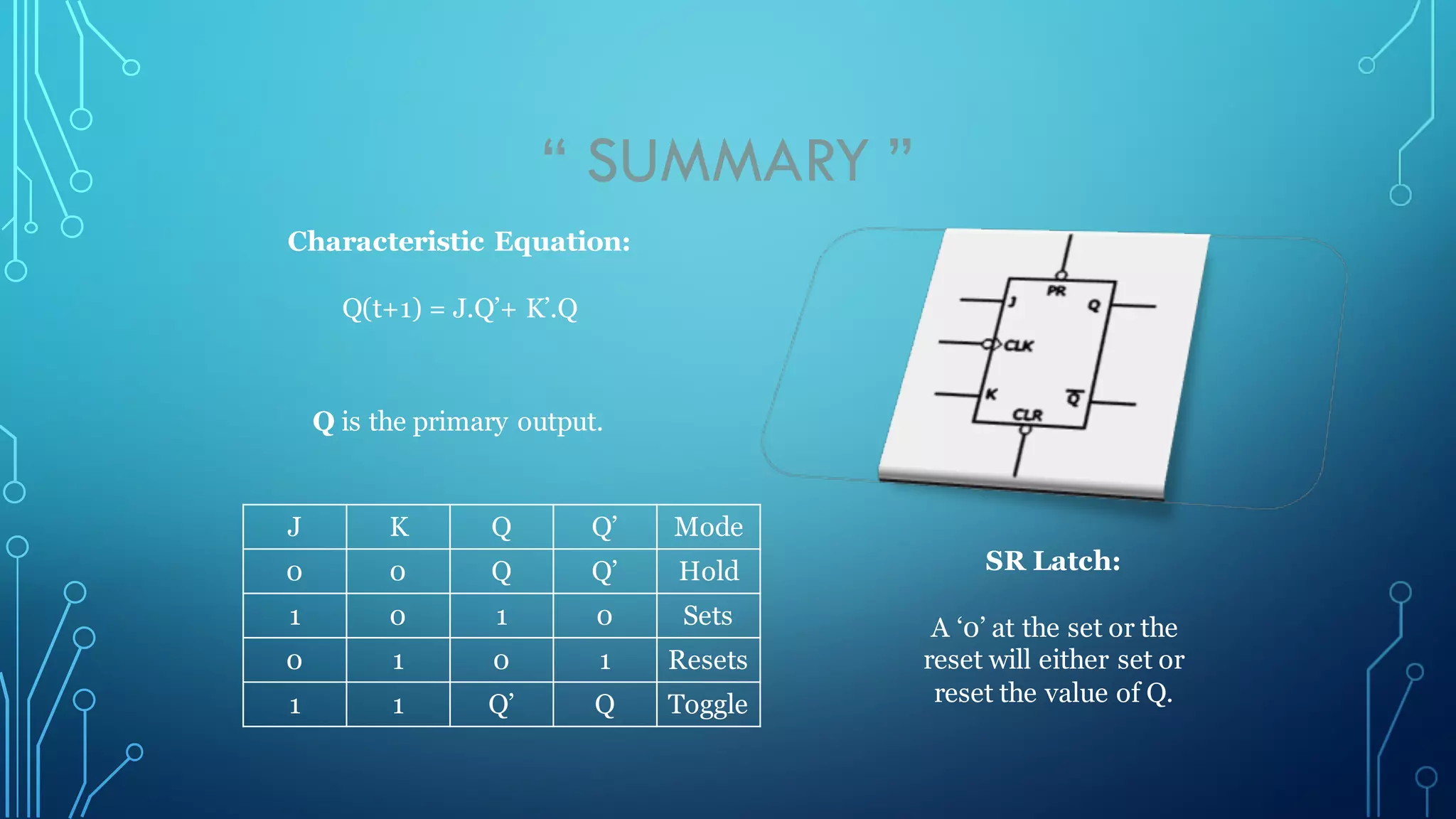

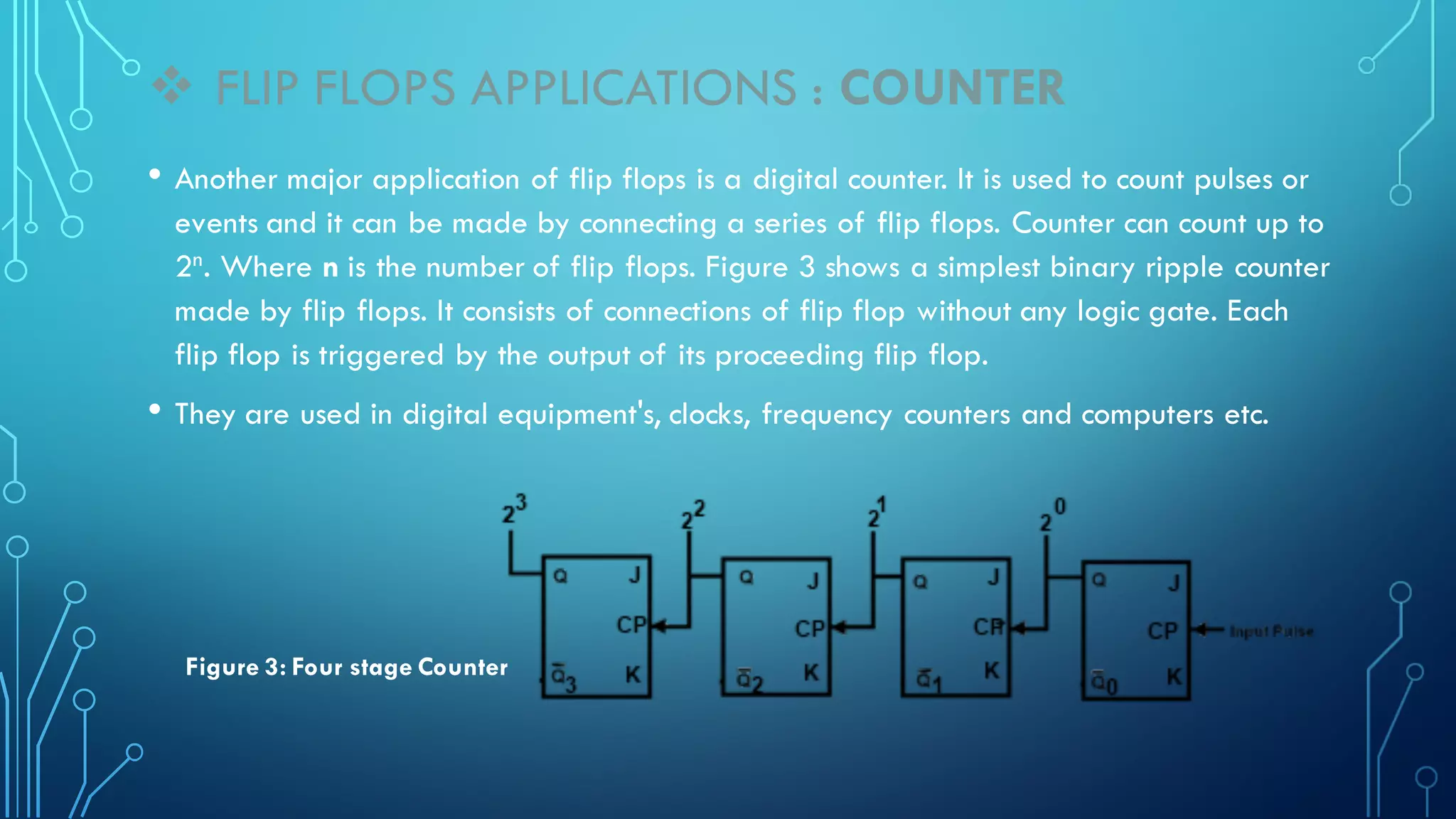

JK flip-flops have two outputs, Q and Q', and four modes of operation: hold, set, reset, toggle. The primary output is Q. There are two stable states that can store state information. JK flip-flops are used for data storage in registers, counting in counters, and frequency division. They can divide the frequency of a periodic waveform in half by toggling on each input clock pulse.