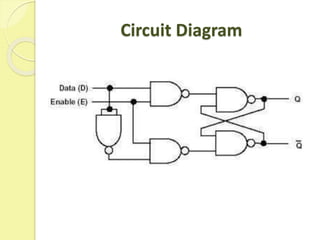

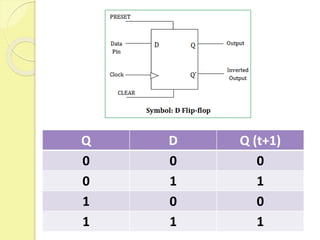

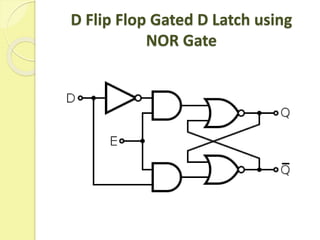

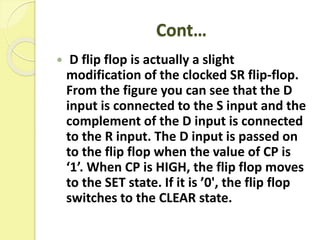

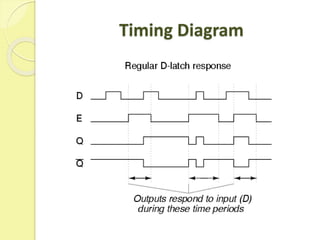

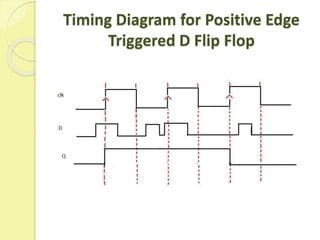

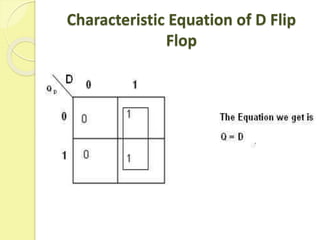

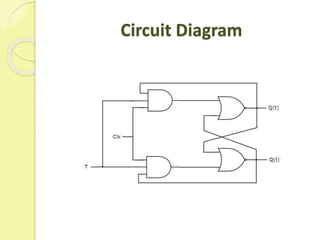

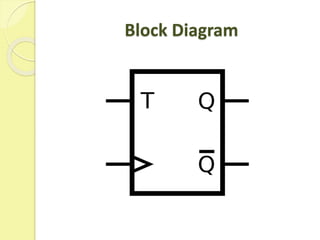

The document discusses the design and functioning of D and T flip-flops in digital electronics, providing details on their circuit diagrams, characteristics, and truth tables. The D flip-flop is described as a modification of the clocked SR flip-flop with a data input that transfers information during a clock pulse. T flip-flops are introduced as a single-input version of JK flip-flops, designed to toggle their state based on clock signals.