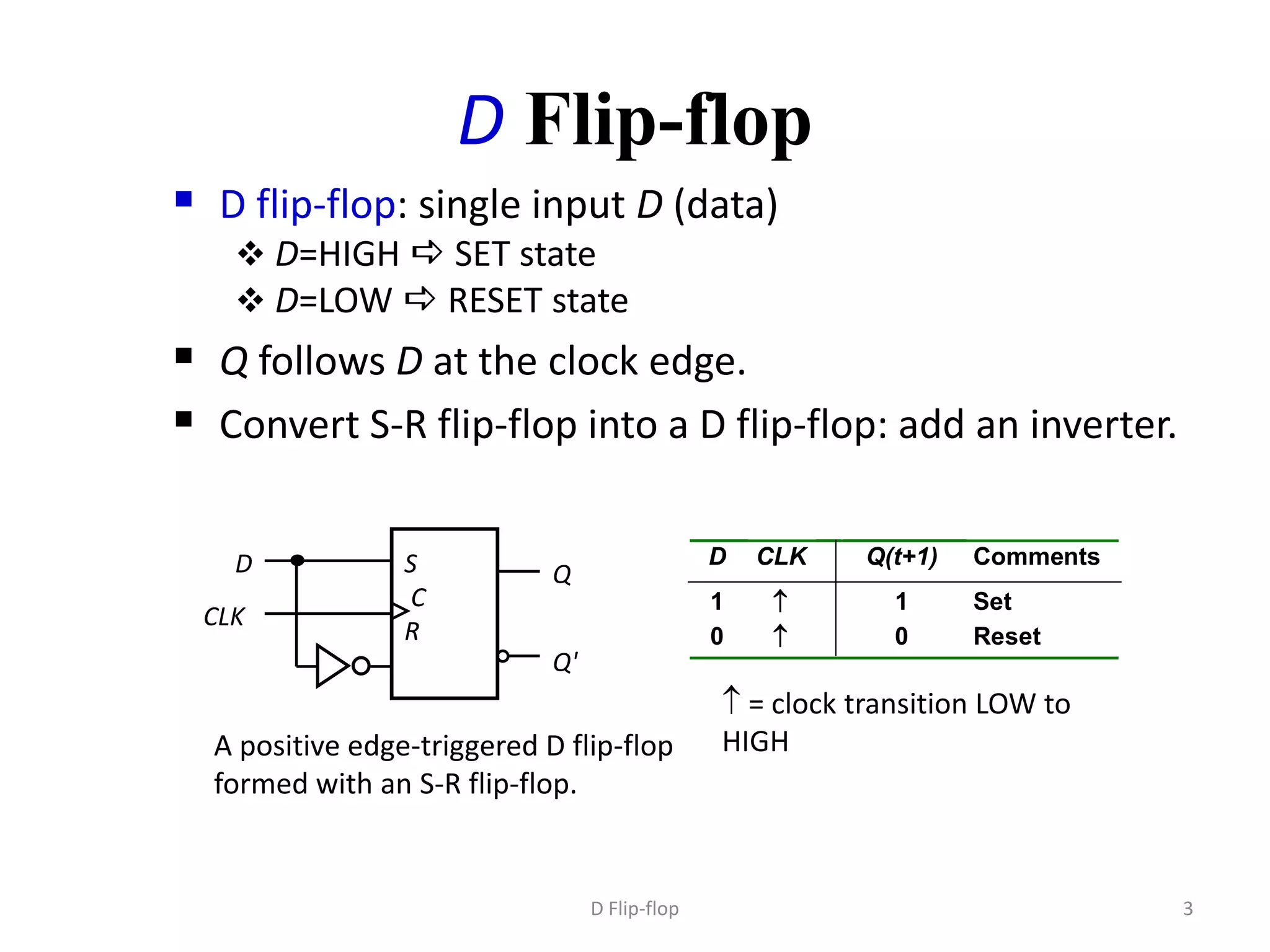

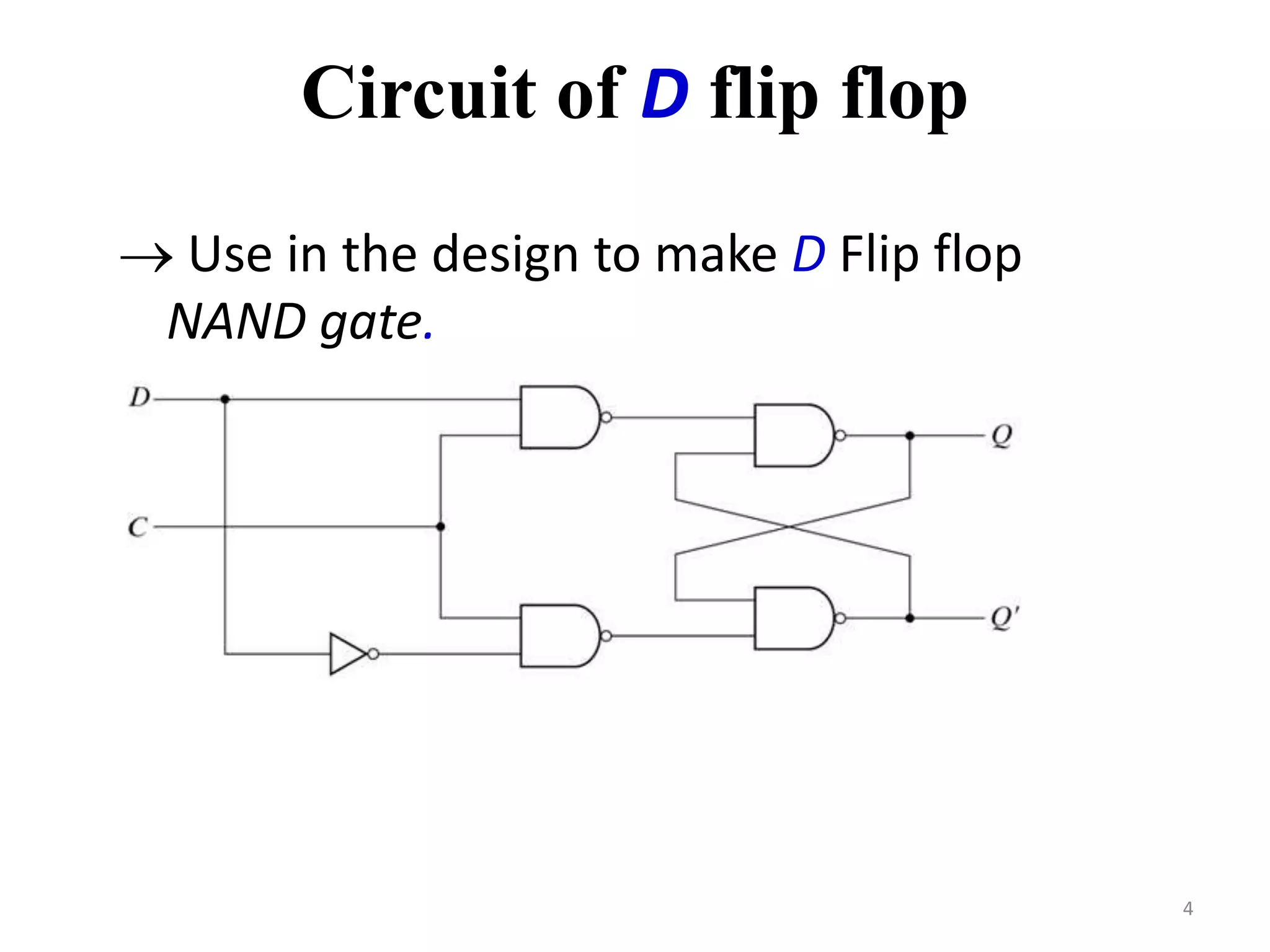

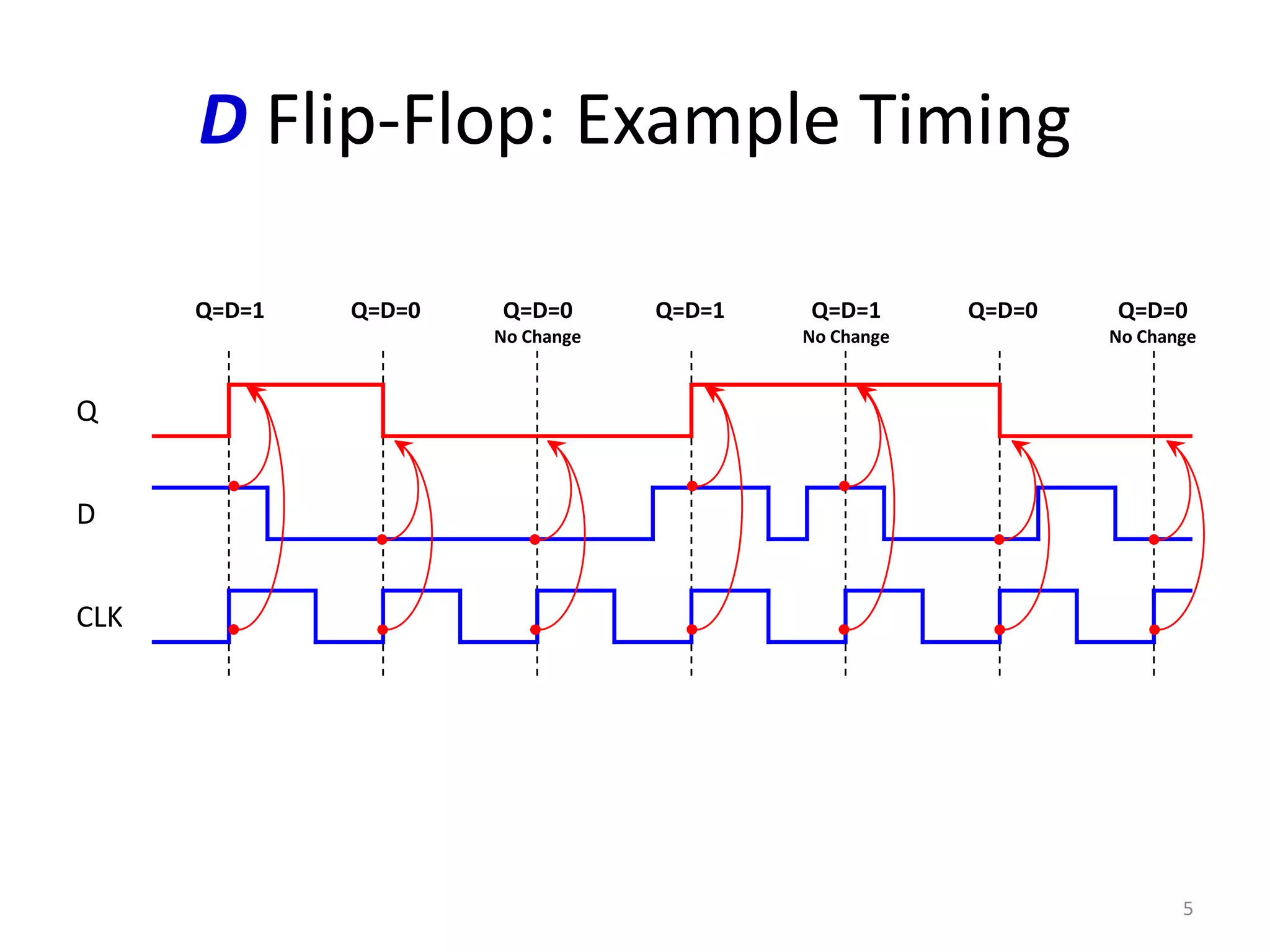

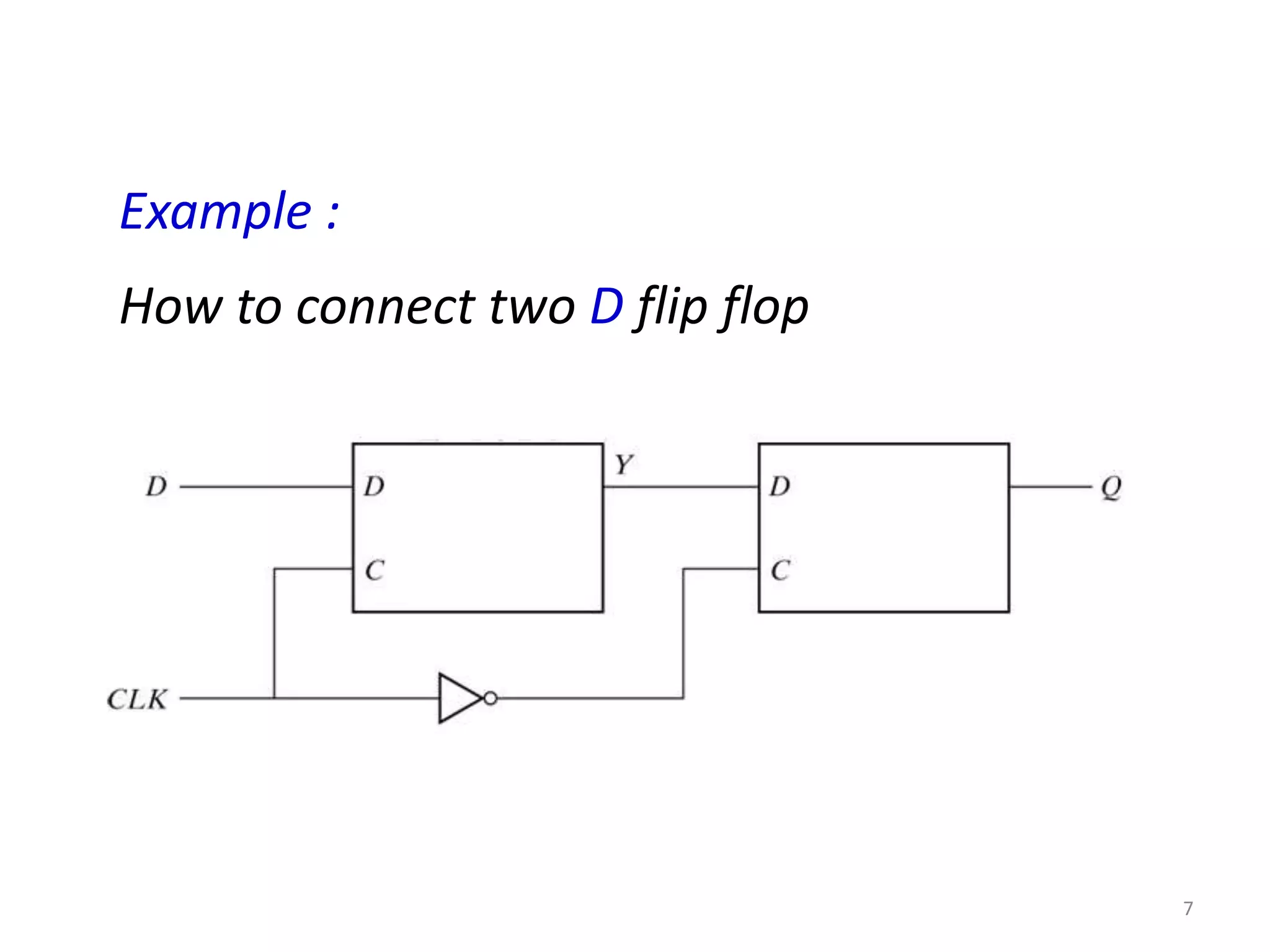

This document discusses D flip-flops. It states that a D flip-flop stores one bit of data and its output, Q, follows the input, D, at the rising or falling edge of the clock signal, CLK. A D flip-flop can be constructed by adding an inverter to an S-R flip-flop. The document provides examples of the timing diagram of a D flip-flop and how positive and negative edge triggered D flip-flops work. It also discusses using D flip-flops to create a ring counter and provides an example of a 6-bit ring counter with its output states over 6 clock cycles.