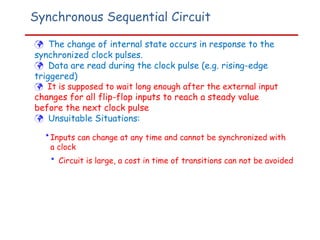

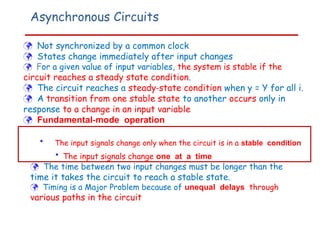

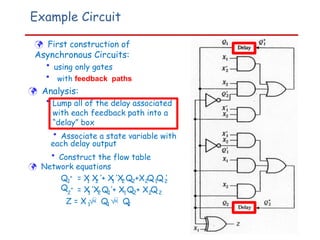

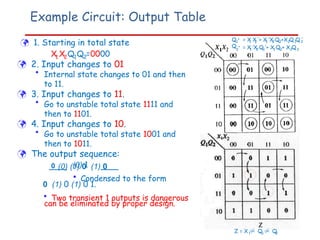

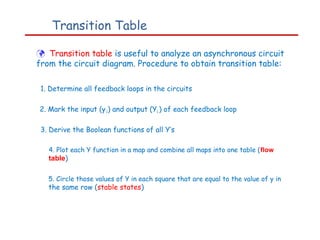

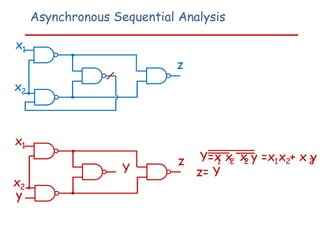

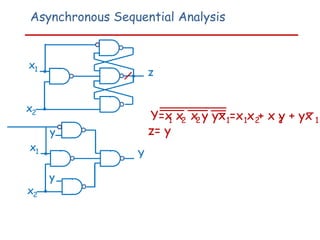

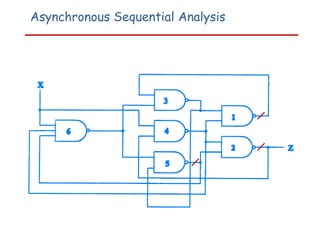

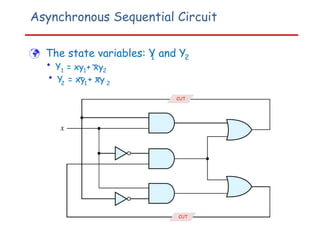

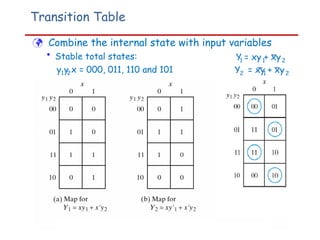

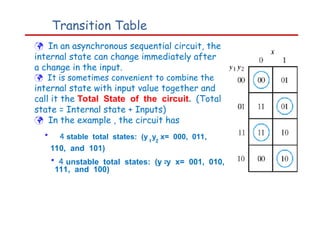

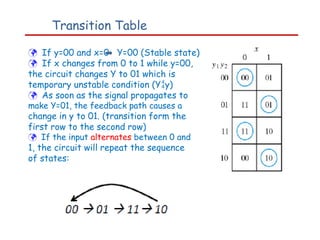

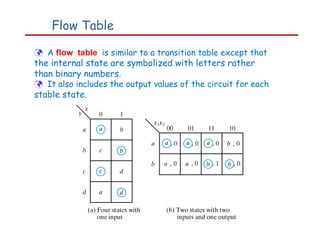

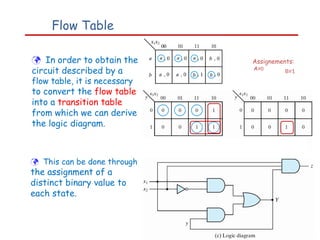

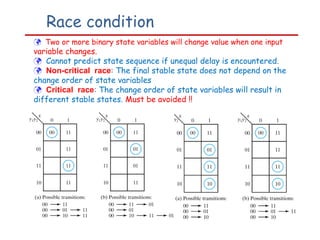

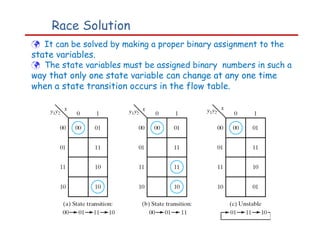

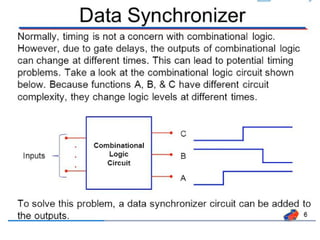

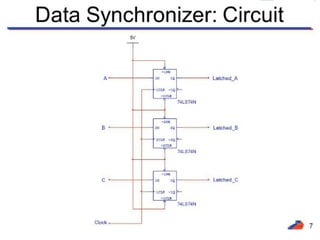

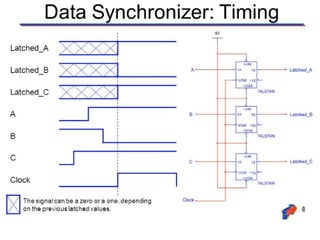

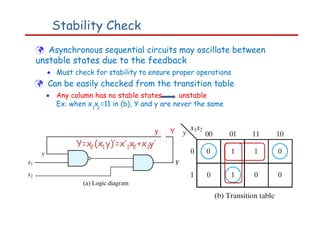

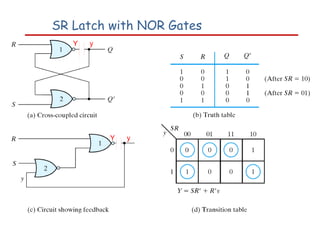

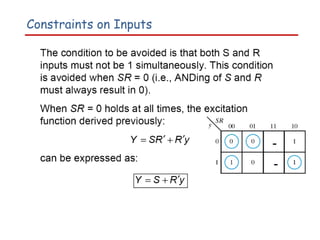

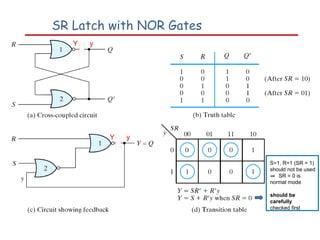

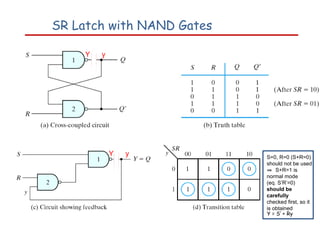

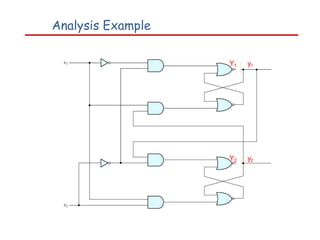

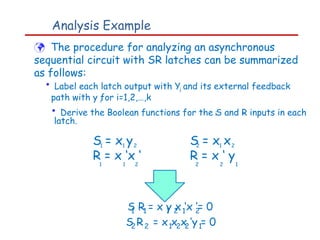

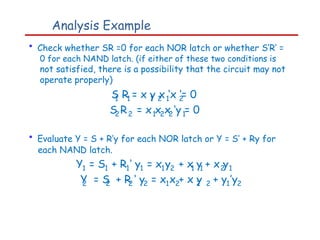

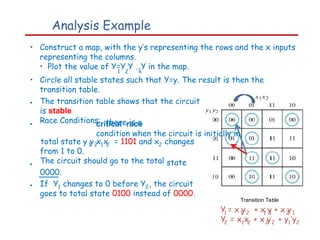

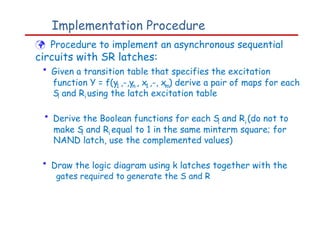

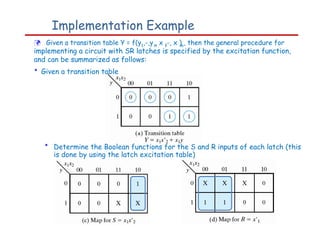

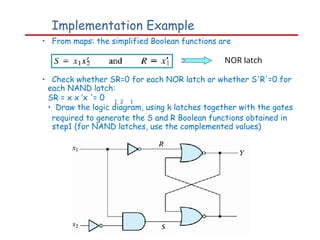

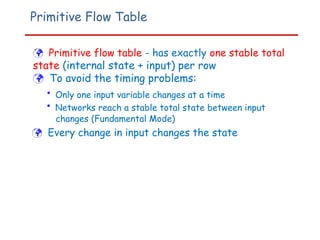

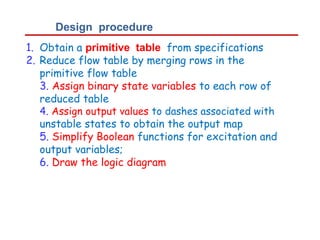

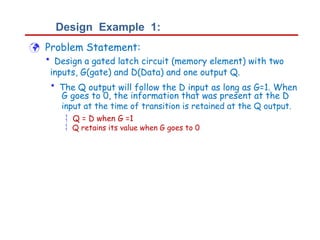

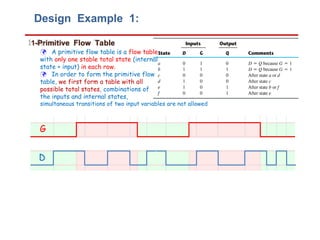

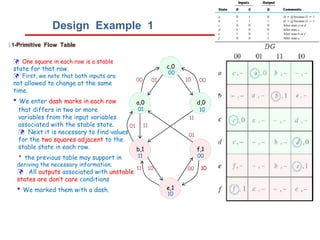

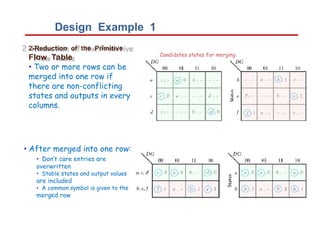

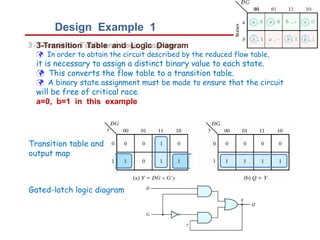

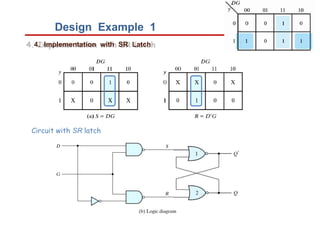

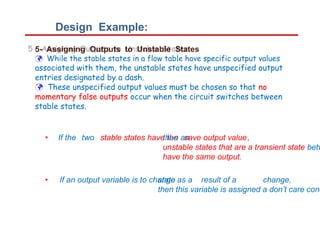

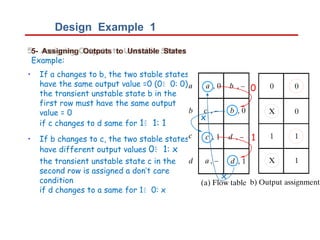

This document discusses asynchronous sequential logic circuits, highlighting differences between synchronous and asynchronous designs, including state changes, timing problems, and analysis procedures. It covers essential concepts such as stable and unstable states, race conditions, and various circuit implementations, including SR latches and gated latch circuits. The document also provides examples and detailed methodologies for constructing and analyzing asynchronous circuits.