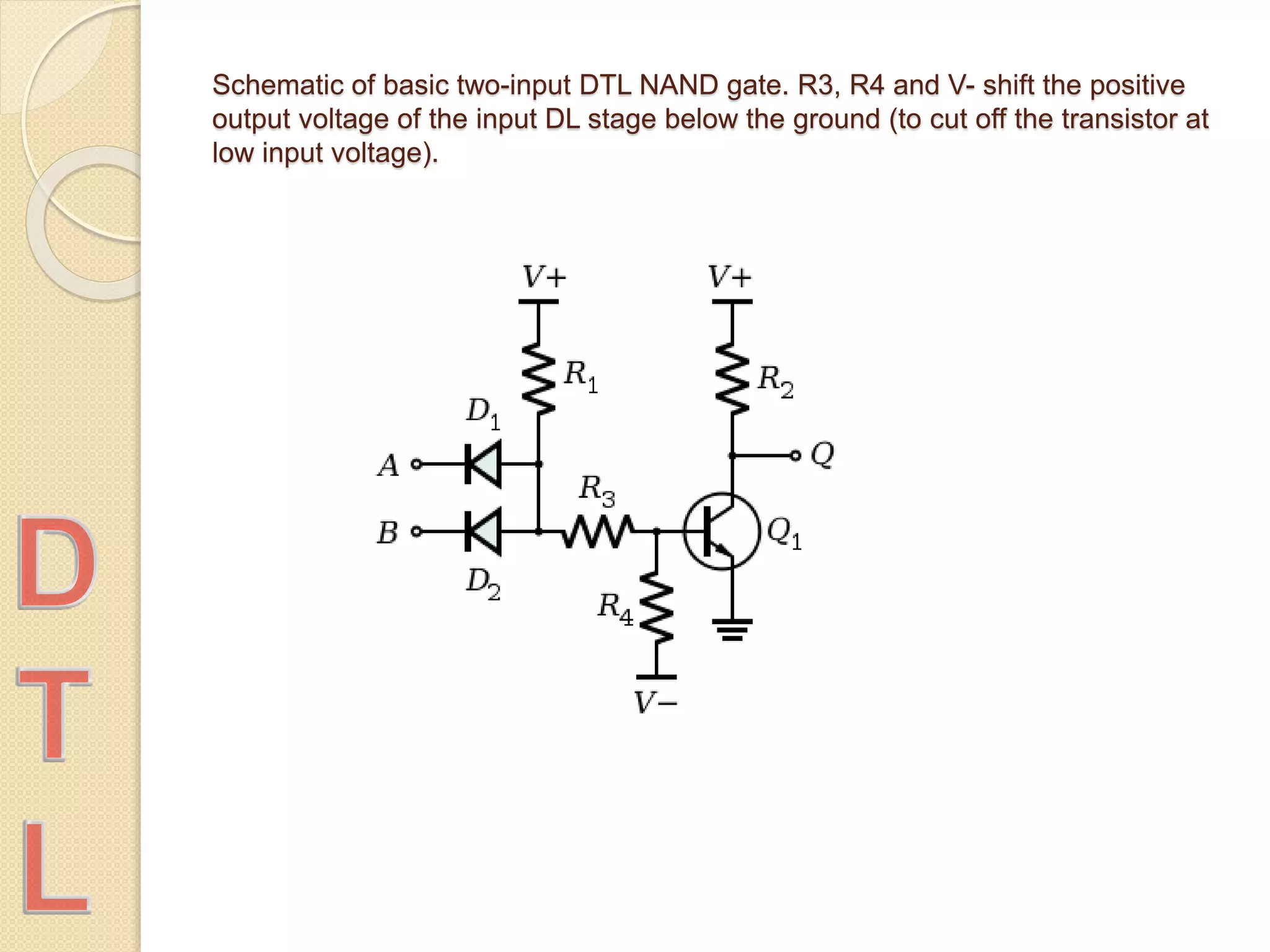

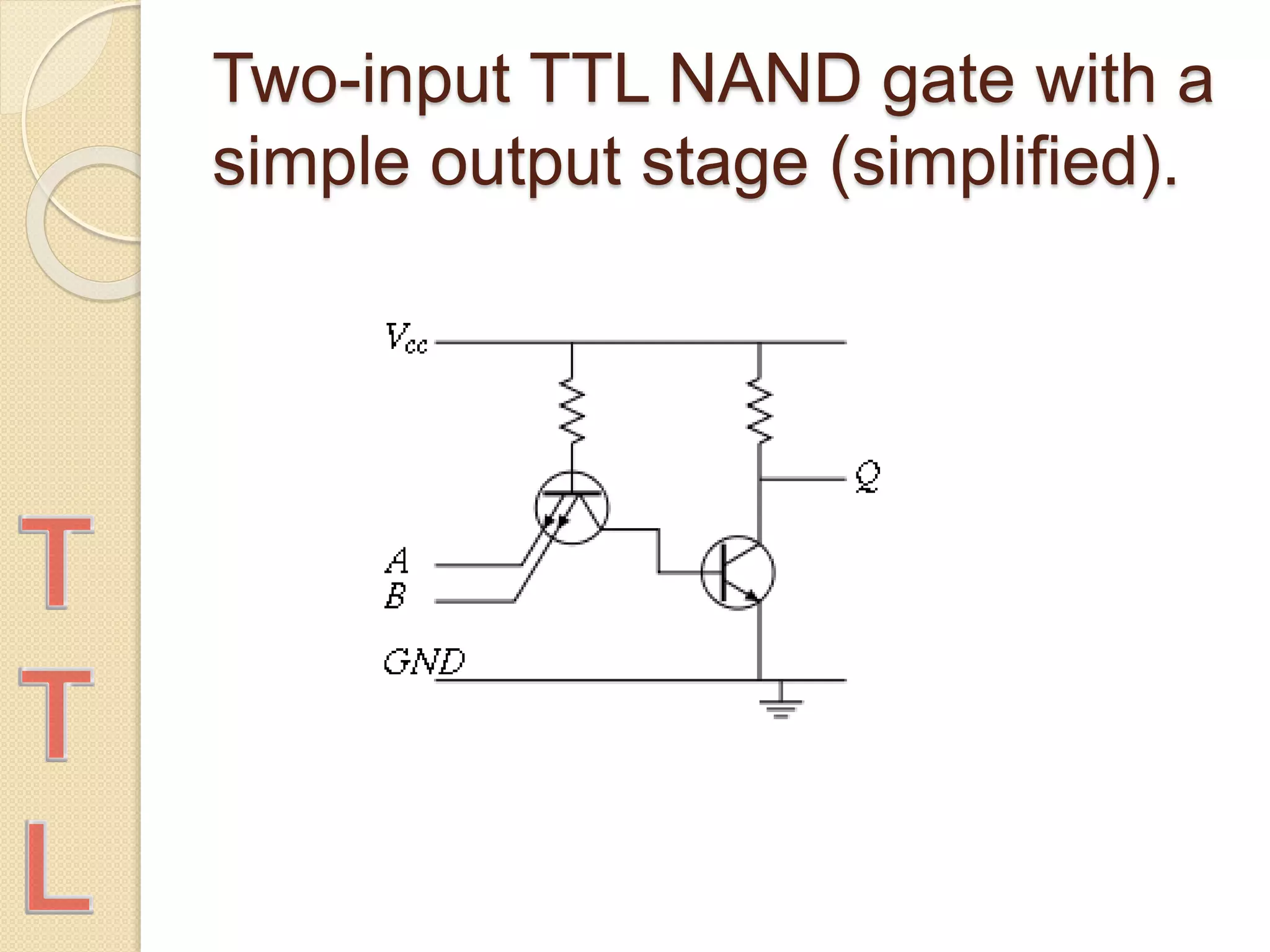

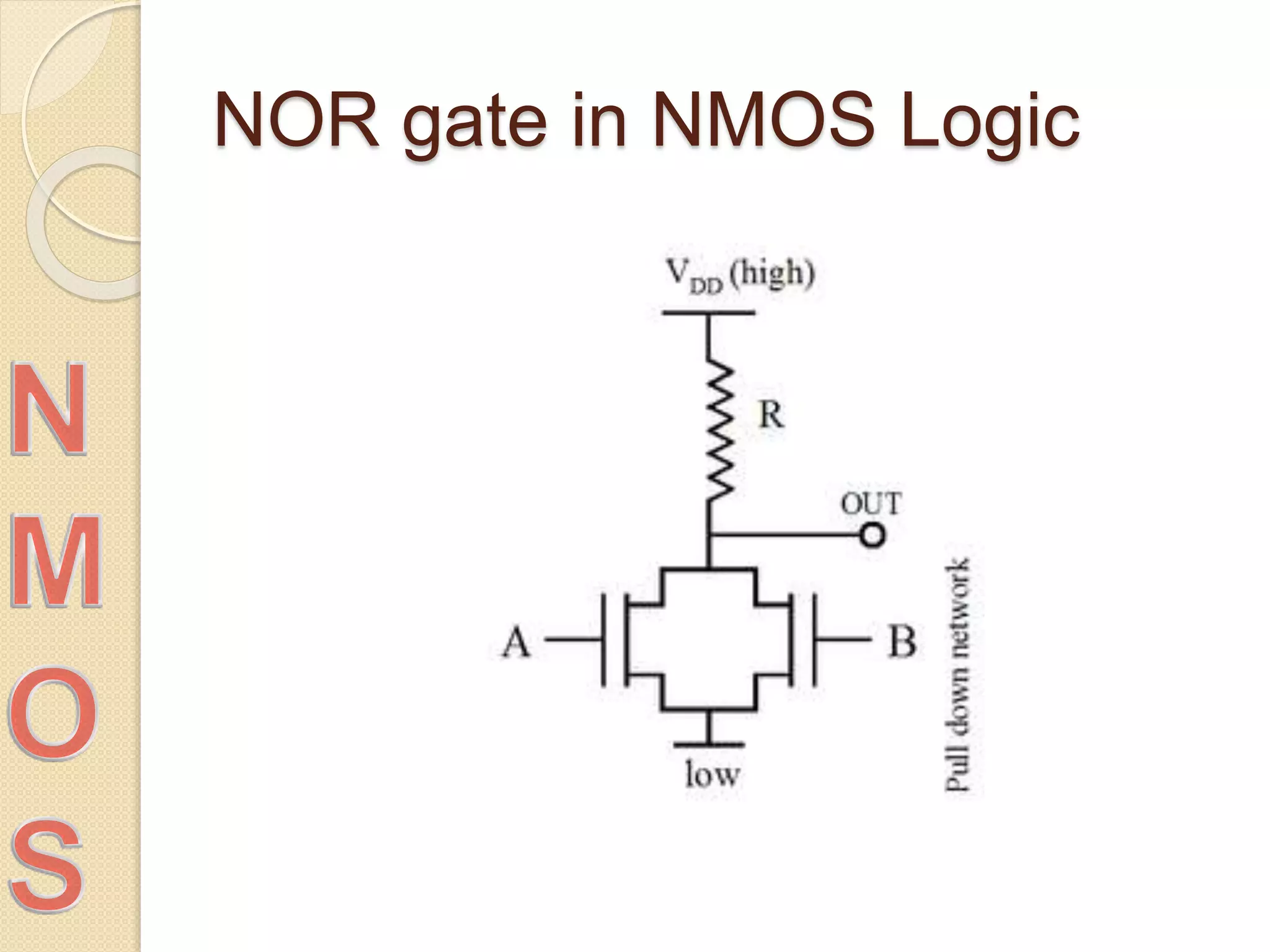

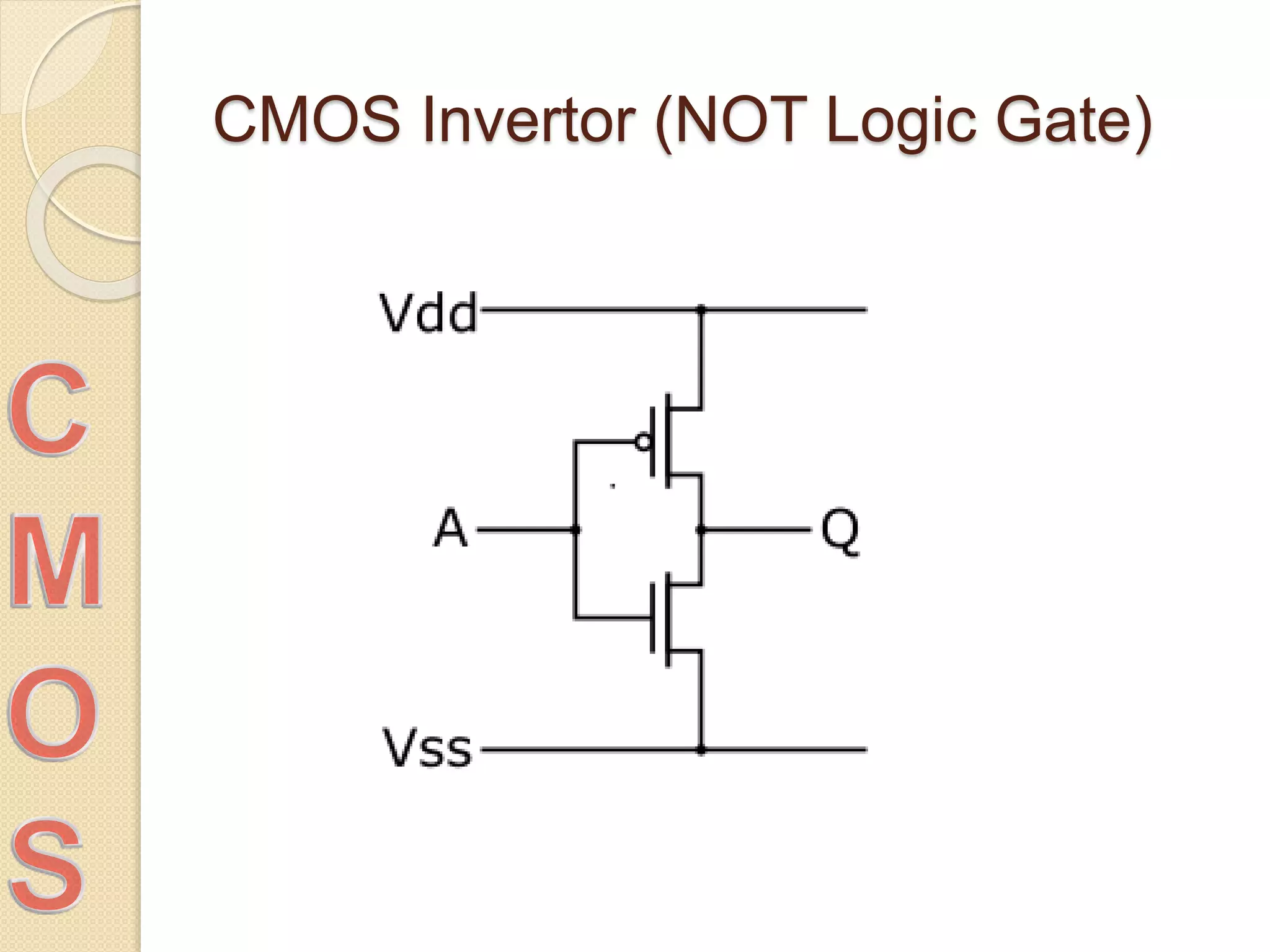

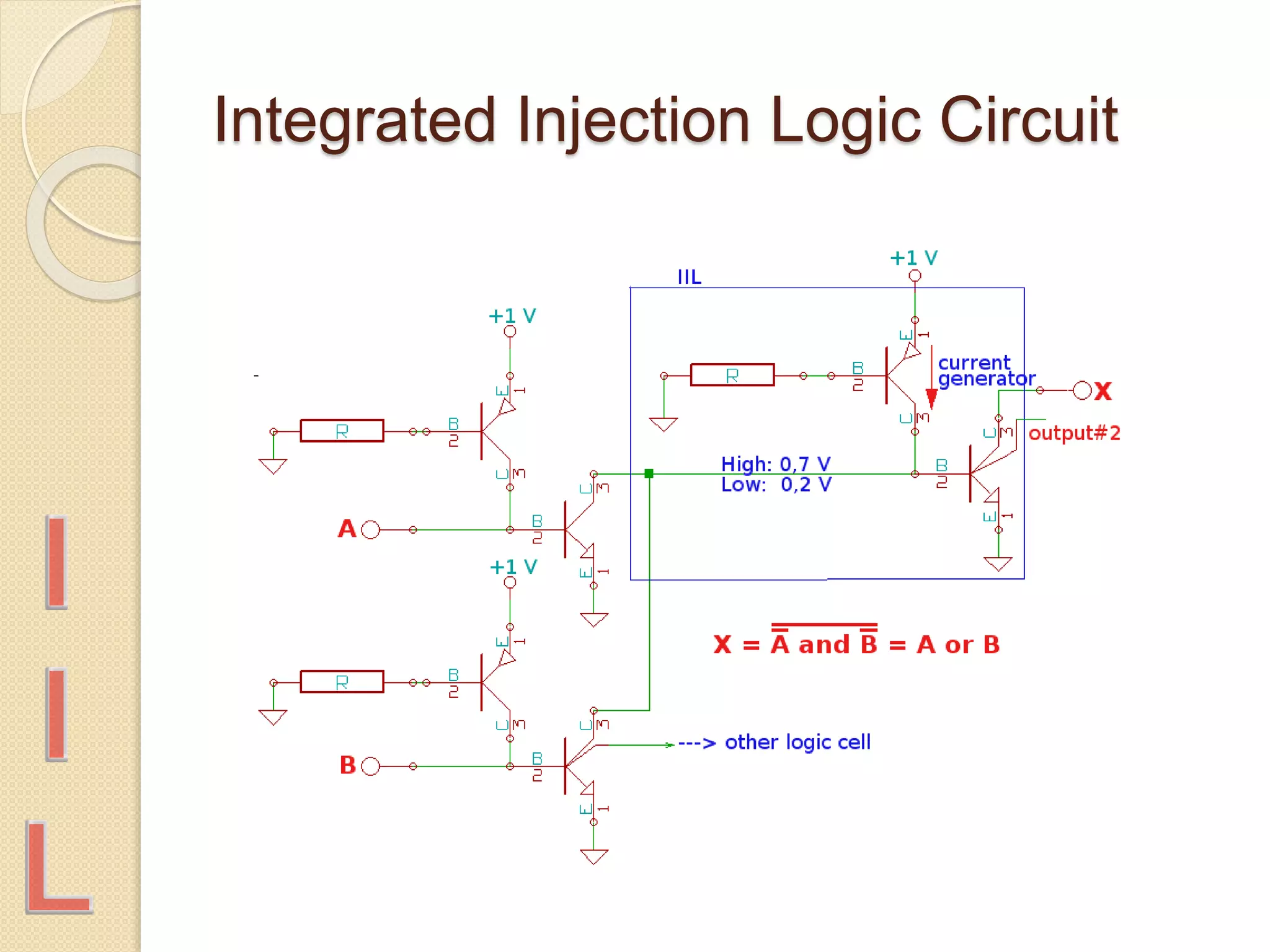

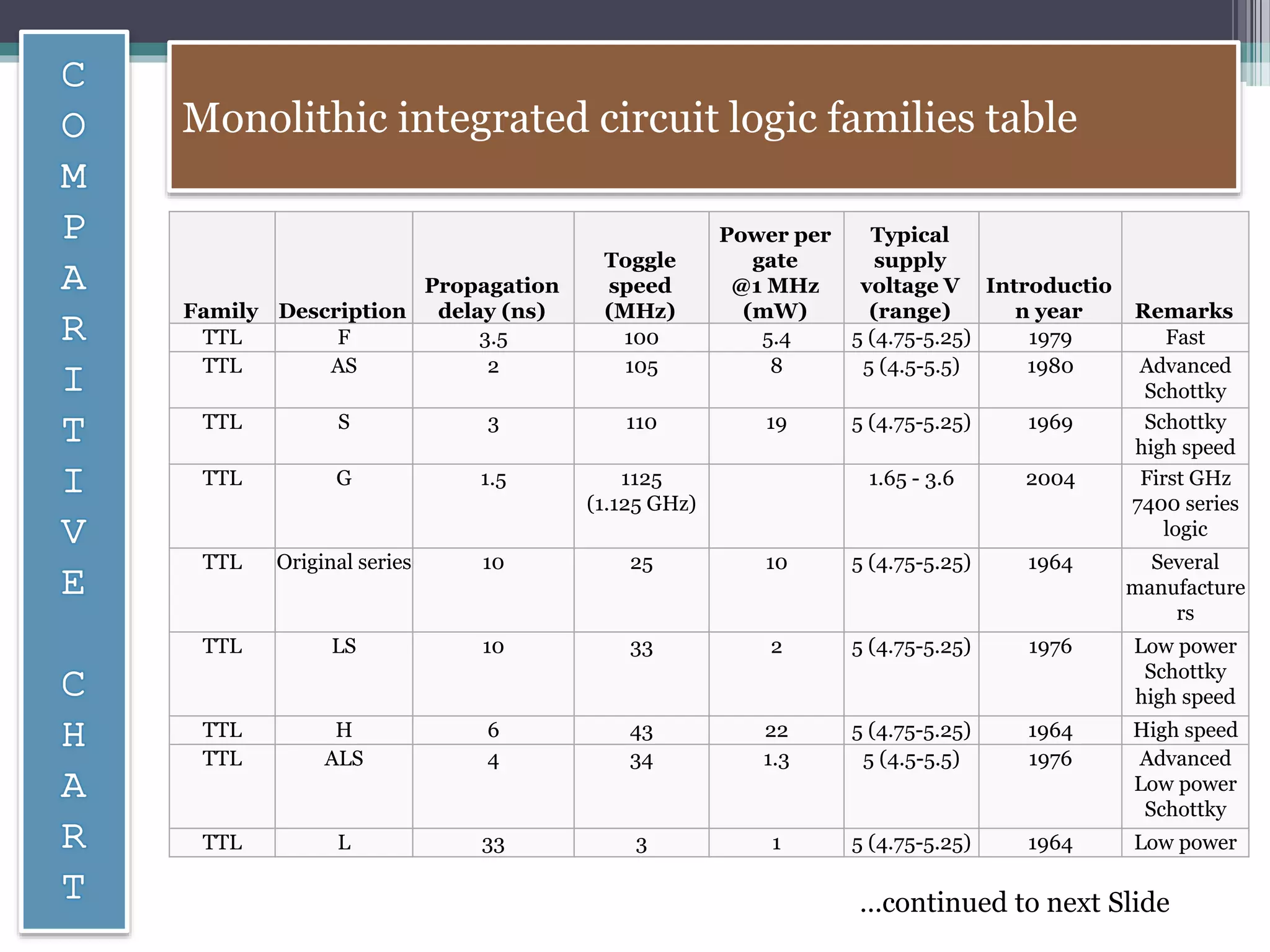

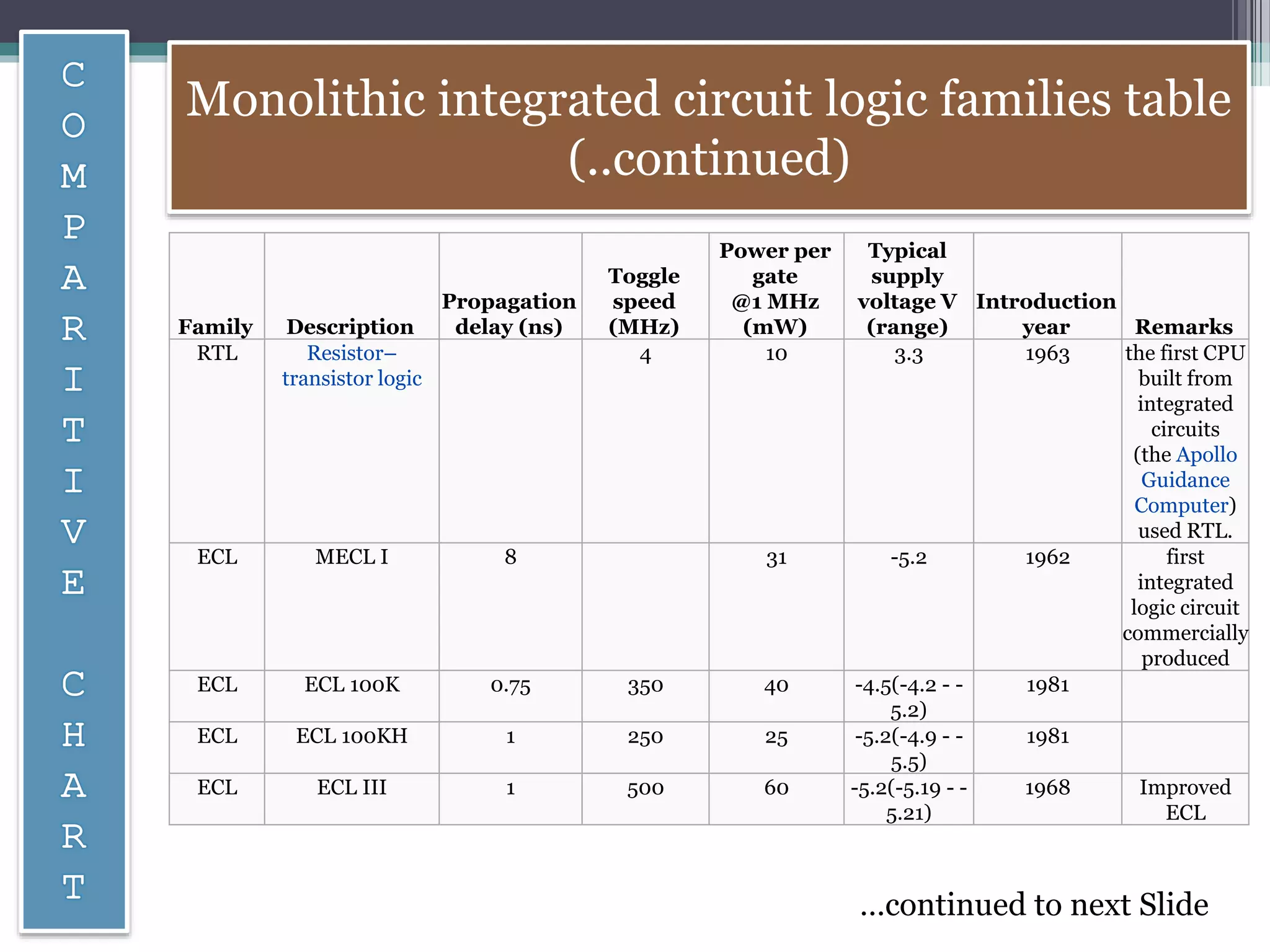

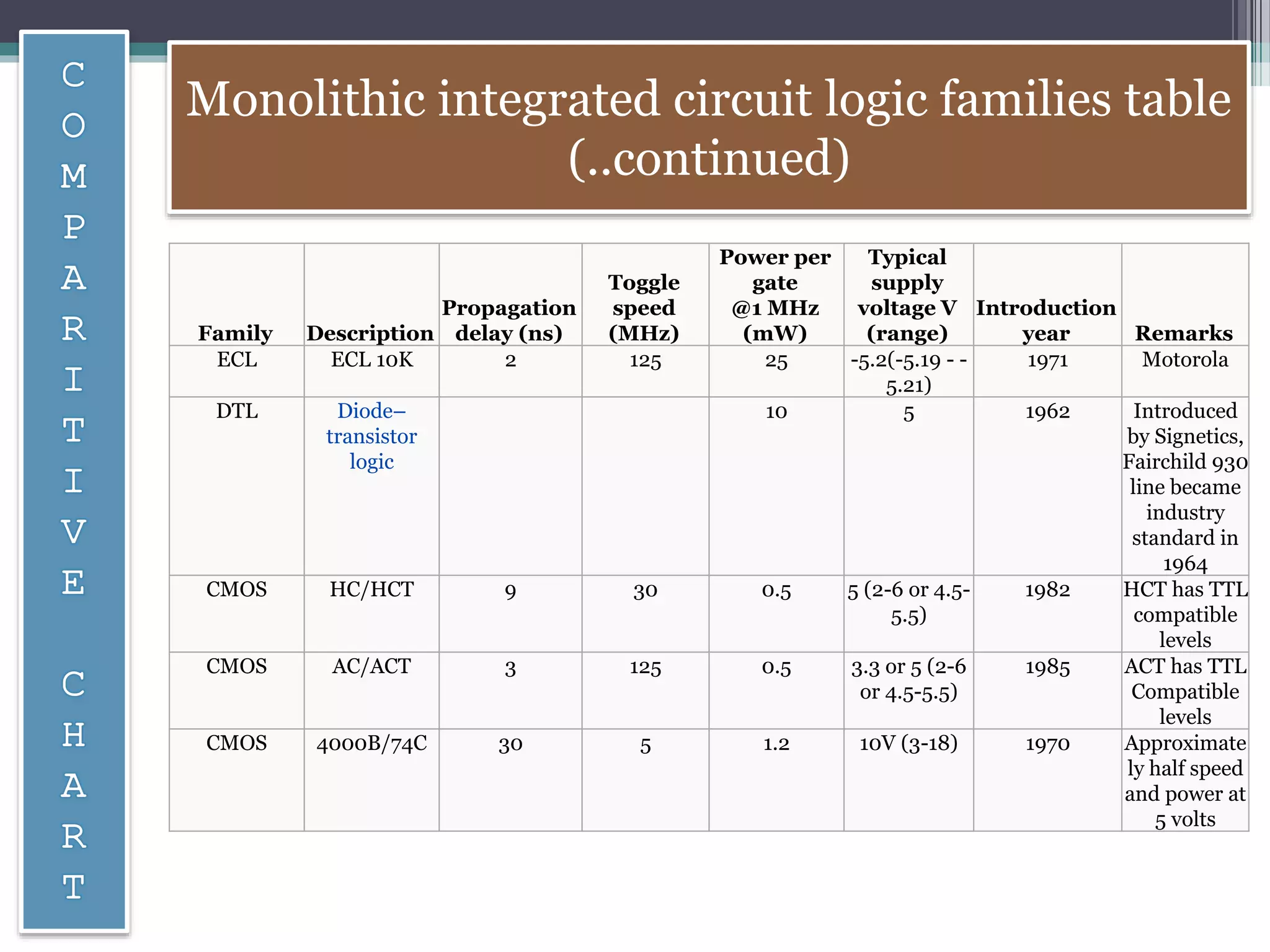

The document discusses various logic families used in digital integrated circuits, including resistor–transistor logic (RTL), diode–transistor logic (DTL), transistor–transistor logic (TTL), emitter-coupled logic (ECL), metal–oxide–semiconductor logic (both p-type and n-type), complementary metal–oxide–semiconductor logic (CMOS), integrated injection logic (I2L), and gunning transceiver logic (GTL). Each family is characterized by its construction, performance metrics like propagation delay and power consumption, historical development, and specific advantages and disadvantages. Overall, the document serves as an overview of the technologies employed in building electronic logic gates and their applications in various systems.