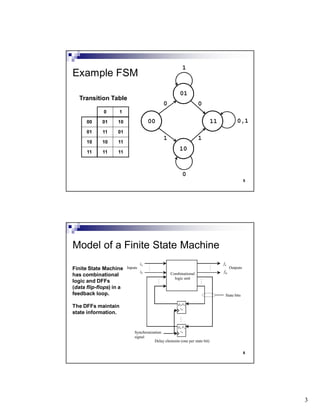

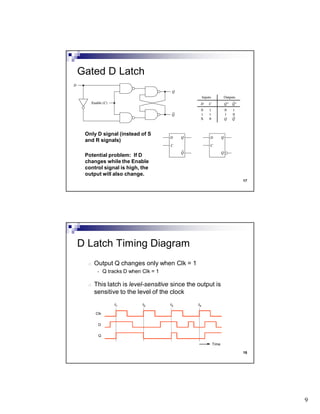

The document discusses sequential circuits and their components. It begins with an overview of sequential circuits and finite state machines. It then covers different types of flip-flops like D flip-flops and their usage. Counters and sequencers are presented as examples of sequential circuits. Details about designing a 3-bit up counter like its state table and logic equations are provided. Finally, registers are discussed including an example of a 4-bit register with parallel load.