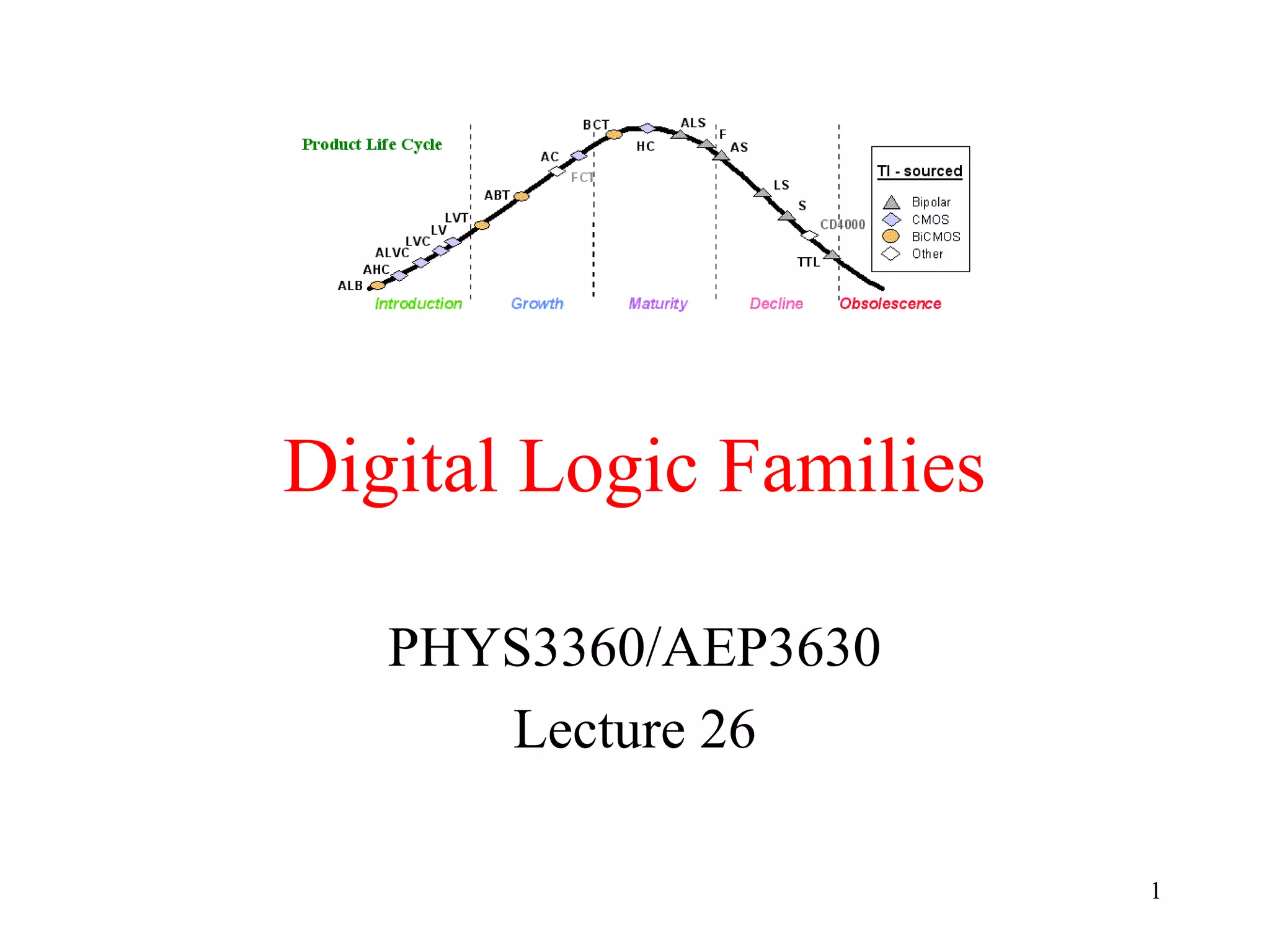

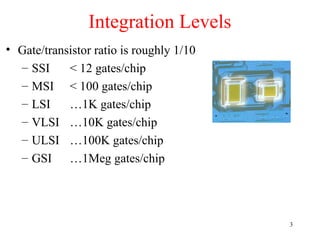

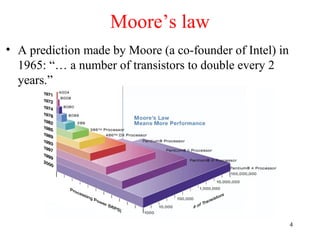

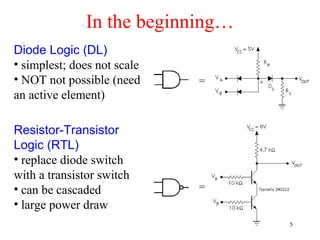

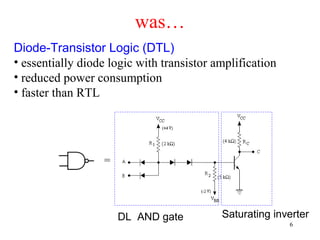

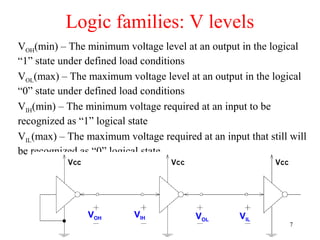

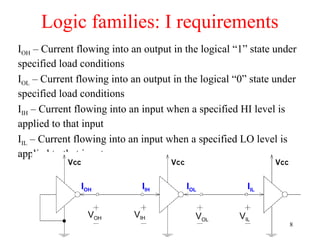

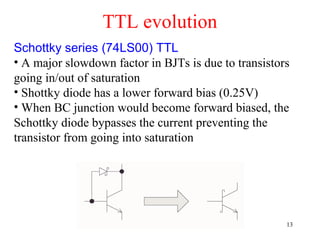

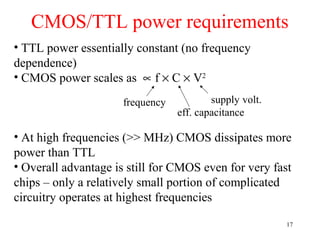

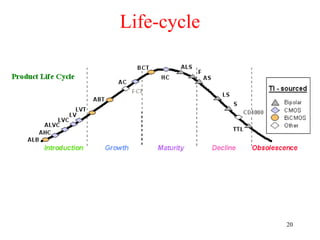

Digital logic families have evolved significantly over time, starting with simple families like diode logic and resistor-transistor logic. Transistor-transistor logic (TTL) was introduced in 1964 and helped standardize digital design. TTL evolved through families like Schottky TTL that improved speed. Emitter-coupled logic (ECL) provided the fastest speeds but had high power consumption. Complimentary MOS (CMOS) logic provided very low static power, scaling abilities, and eventually surpassed TTL. CMOS families have continued advancing through lower supply voltages and greater integration levels according to Moore's Law.