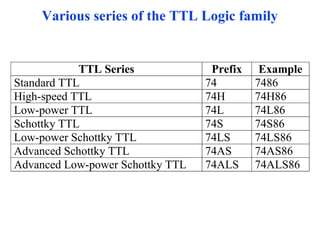

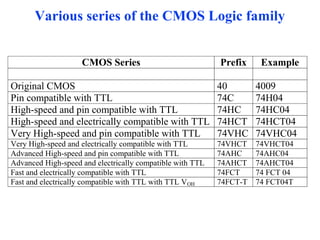

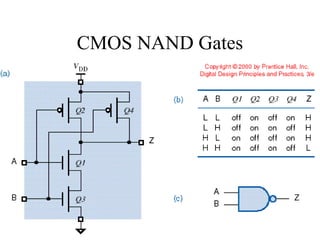

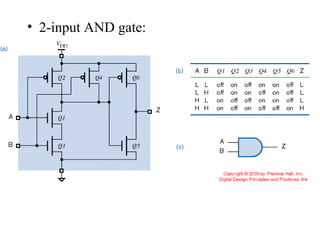

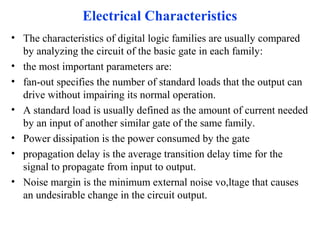

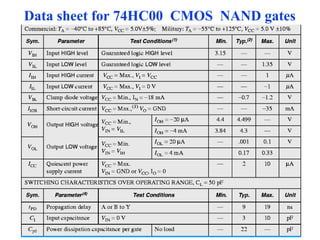

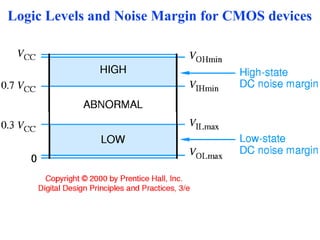

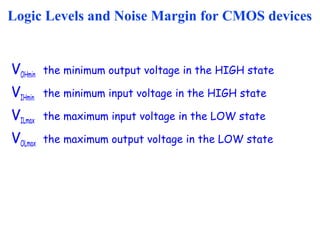

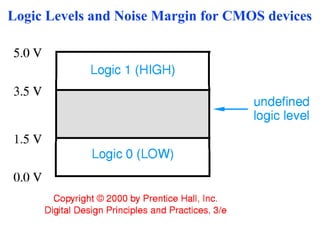

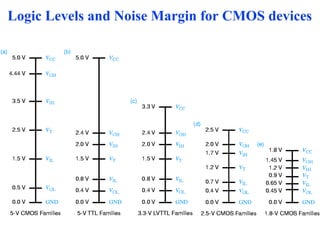

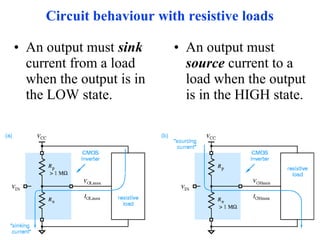

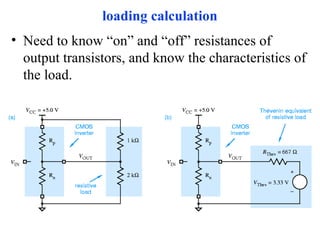

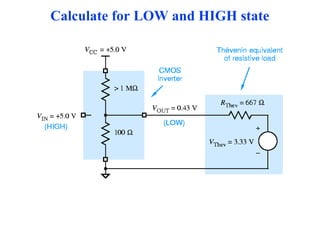

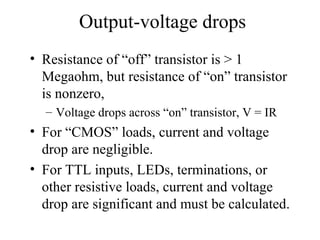

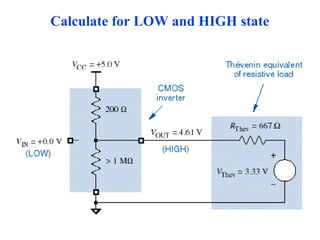

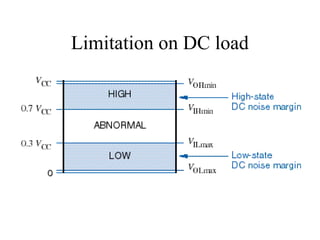

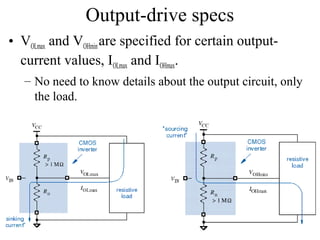

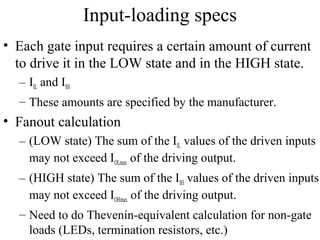

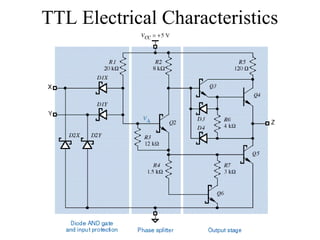

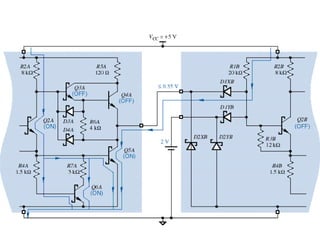

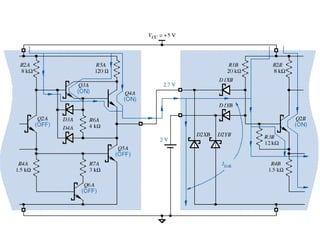

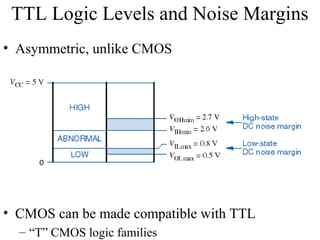

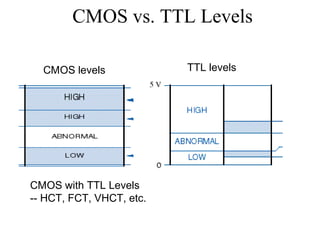

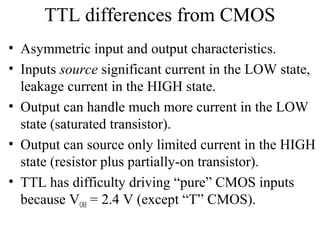

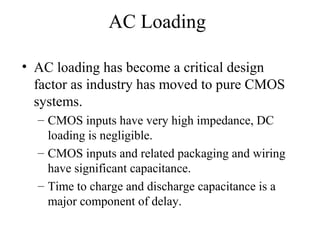

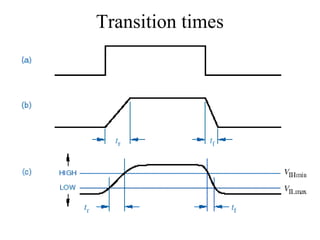

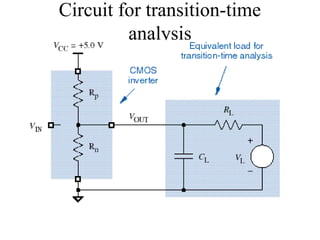

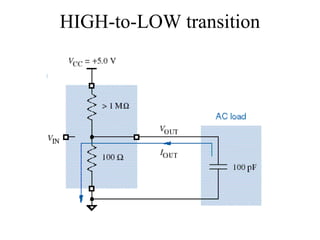

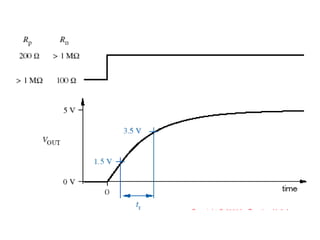

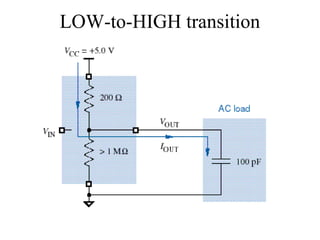

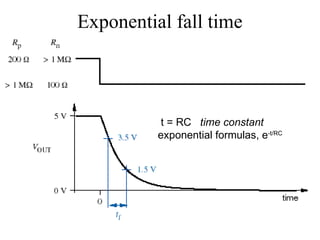

Digital logic families classify integrated circuits by their circuit technology. A logic family consists of chips that perform logic functions like AND and OR with similar input/output characteristics. Popular families include TTL, ECL, MOS, and CMOS. CMOS uses fewer transistors than other families for inversion and is known for low power. Logic levels and noise margins define input and output voltage thresholds. Transition times and capacitive loading affect a circuit's propagation delay.