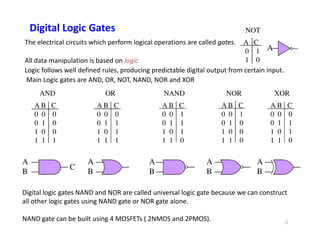

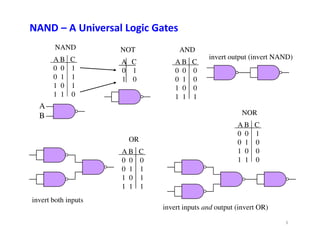

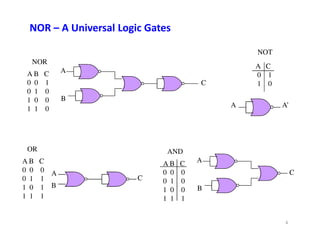

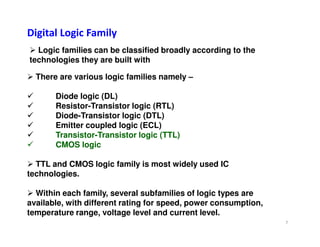

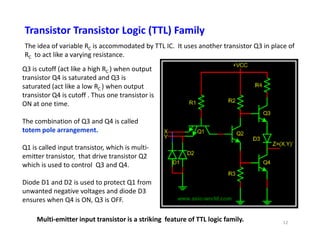

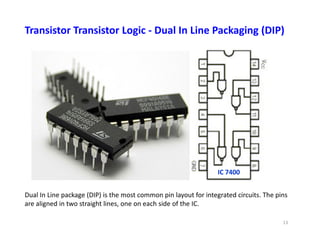

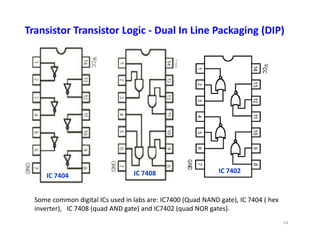

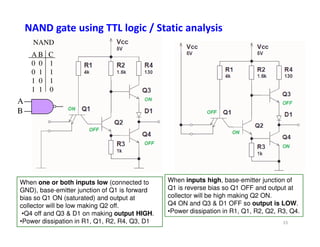

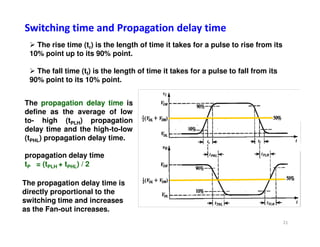

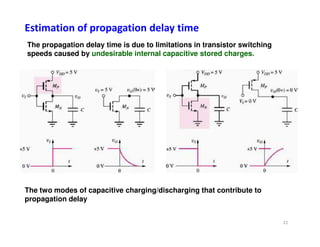

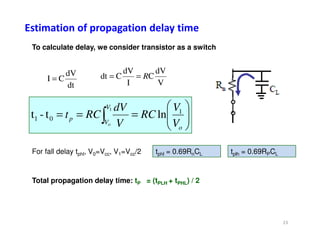

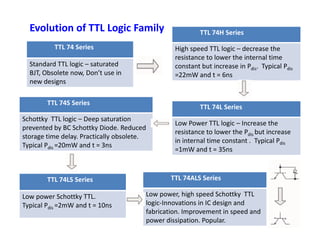

Digital logic gates called NAND and NOR are considered universal logic gates because all other logic gates can be constructed using only NAND gates or only NOR gates. Transistor-Transistor Logic (TTL) is one of the most widely used integrated circuit logic families. TTL uses a multi-emitter input transistor and a totem-pole output stage to provide a variable output resistance and achieve high noise immunity. Key parameters for logic families include input/output voltage levels, propagation delay, power dissipation, and noise margins.