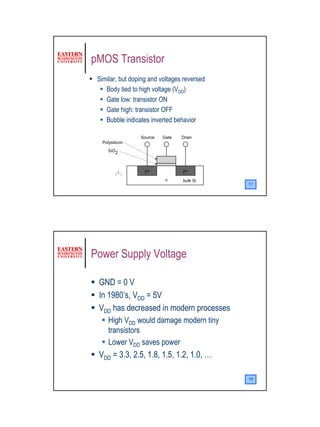

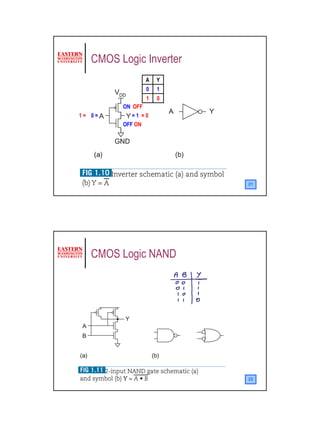

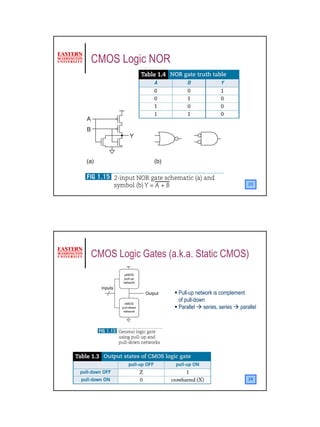

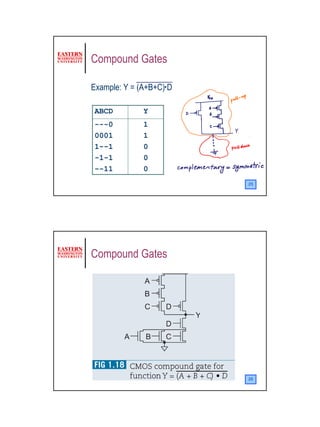

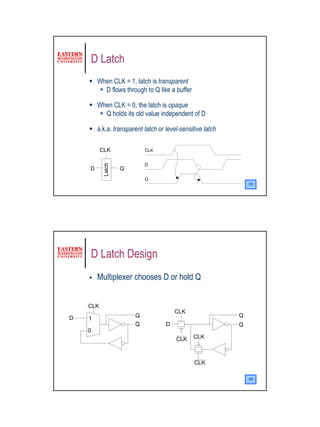

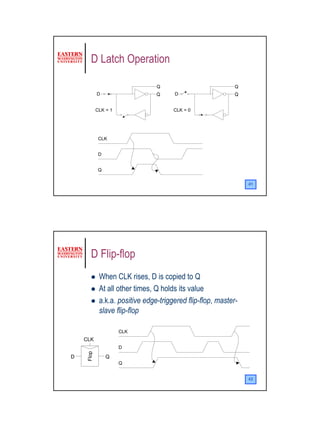

CMOS VLSI design involves integrating many transistors on a single chip using complementary MOS (CMOS) technology. CMOS uses both n-type and p-type MOS transistors and allows for designing digital circuits that are fast, cheap, and low power. Key topics covered in the document include the history of integrated circuits and Moore's law, MOS transistor operation, CMOS logic gate design, multiplexers, latches, and flip-flops. The document provides an introduction and overview of the key concepts in CMOS VLSI design.