The document describes a proposed low power, high speed multiplier circuit designed using a technique called New Vedic VLSI. The multiplier uses a Vedic multiplication method to generate partial products faster. An addition section with a carry look ahead adder is used to sum the partial products, providing faster operation than a ripple carry adder. Simulation results showed the proposed design consumed 41.868 μw of power over 10ns, compared to 65.4 μw for a design using a ripple carry adder, for a 23.592 μw power reduction. The high speed, low power multiplier design is suitable for applications like digital signal processors that require efficient multiplication.

![1

Abstract—During designing of VLSI circuit, one would

concentrate in the optimization of different entities. Among these

entities, power dissipation is a critical parameter in the field of

modern VLSI design. In this paper, High speed low power

multiplier has been designed by adopting effective technique

called New Vedic VLSI Technique (NNVT). It increases the

performance by using carry look ahead adder as it can produce

carry bits faster. The proposed multiplier is implemented and

power analysis on a 012µm CMOS technology using

Microwind3.1. Based on the power analysis result it is shown

that when the carry look ahead adder is used, the power

consumption is 41.868 µw in 10ns while ripple carry adder causes

65.4µw power consumption in 10ns. The speed of the multiplier is

enhanced by using the Vedic multiplication technique. The

proposed high speed low multiplier can obtain 23.592 µw power

reductions in modified New Vedic VLSI Technique (NNVT)

when compared to convention multiplier. The high speed

processor requires high speed multipliers and the New Vedic

VLSI Technique (NNVT) suitable for this purpose.

Index Terms—Carry look ahead adder, Dsp processor, Low

power, Multiplier, NNVT.

I. INTRODUCTION

HIS the speed of the processor architectures such as

CISC, RISC etc is increased with the help of Arithmetic

operations in different digital circuits. The speed-up

process involves two important parameters viz. multiplication

and addition process. Though Multiplication is a less common

operation than addition, it is essential for many structures such

as microprocessor, digital signal processing and graphics

engines. Many of the DSP algorithms have the need of high

speed multiplier as the multiplication process dominates the

execution time in such algorithm.

New developments in the technology induce the need for

higher and higher speed in multipliers. Researchers are going

on to design multipliers to achieve high speed, regularity of

layout, low power consumption and thus less area or even

combination of them in multipliers.

Due to the increased complexity in various applications, not

only faster multiplier chips but also smarter and efficient

multiplying algorithms are necessary to implement in the

chips. Array multiplication algorithm and Booth multiplication

algorithm are the two most widely used multiplication

algorithms in the digital hardware. But these two algorithms

suffer by the drawback of large propagation delay associated

with it.

II. RELATED WORK

Multiplication algorithm will be used to demonstrate

method of designing different cells and thus they can fit into

large structure. The product of two unsigned (positive) binary

numbers forms the most basic form of multiplication process

which can be accomplished through the traditional method and

simplified to base 2. For instance, consider multiplication of

two positive 4-bit binary integers (1410 and 610). The

multiplication process can be done as.

1110:1410 Multiplicand

0110:610 Multiplier

……………..

1110

0000 Partial Product

1100

0000

……………….

01010100:8410 Product

S * T-bit multiplication is done by forming „N‟ partial

products of „S' bits each, and then obtaining the sum of the

appropriately shifted partial product which produces an S+T-

bit result „R‟ whereas Binary multiplication is just equivalent

to a logical „AND‟ operation. Therefore, the partial product

can be generated by logical „AND‟ of the appropriate bits of

the multiplicand and multiplier. Then, each column of partial

products must be added and carry values should be passed to

the next column, if any. If the multiplicand is denoted as

S=(Sm-1, Sm-2, ….., S1, S0) and the multiplier as T=(Tn-1, Tn-2,

…..,T1,T0). For unsigned multiplication, the product can be

obtained by the equation

There are various types of Multiplication [1] and Adders.

The various types of multiplications are Array Multiplication,

2‟s complement array multiplication, Serial/Parallel

multiplication, Wallace tree multiplication, Booth encoding.

The most familiar multiplication method is „add and shift‟

algorithm [2]. Next, in case of parallel multipliers, main

parameter that determines the performance of the multiplier is

the number of partial products (pp) to be sum. Then partial

products to be summed can be efficiently conquered by

Modified Booth algorithm [3] which is one of the most

popular algorithms. The speed improvements can be achieved

by Wallace Tree algorithm by reducing the number of

sequential adding stages.

The combination of both Modified Booth algorithm and

Wallace Tree technique [4] can increase the performance of

one multiplier. But due to the increase in parallelism,

intermediate sums to be added and the amount of shifts

between the partial products will increase which reduces the

Low Power Multiplier using VEDIC Carry

Look ahead Adder Technique

S.Vijayakumar, Dr.J.Sundararajan, Dr.P.Kumar, S.Rajkumar

T

International Journal of Applied Engineering Research ISSN 0973-4562 Volume 10, Number 9 (2015)

© Research India Publications ::: http://www.ripublication.com

7319](https://image.slidesharecdn.com/d3b1009d-3ebc-4e5e-9b0d-d6a1f4e37e8d-160716150648/85/JOURNAL-PAPER-1-320.jpg)

![2

speed, increases the silicon area due to irregularity of structure

and also increases power consumption due to increase in

interconnect because of complex routing.

Alternatively, the serial-parallel multipliers [5] increases

speed to achieve better performance in terms of area and

power consumption. The selection of the type of multiplier

(parallel/serial) actually depends on the nature of application

in which we are using.

III. PROPOSED ARCHITECTURE

In this paper multiplier which increase speed and reduces

power using Vedic technique and carry look ahead adder is

proposed.

The proposed multiplier mainly consist of two parts

-Multiplication section (Vedic multiplication)

-Addition section (carry look ahead adder)

Fig . 1. NNVT-Proposed Archticture

A. Vedic Multiplication Technique

The primary advantage of Vedic mathematics is that it

reduces the typical calculations in conventional mathematics

to very simple one. The proposed Vedic multiplier [6] is based

on the “Urdhva Tiryagbhyam” sutra (algorithm) which

literally means “Vertically and crosswise”.

1) Vedic Multiplier for 2x2 Module

Consider two 2 bit numbers S and T where S = s1s0 and T

= t1t0. The Vedic multiplier can be implemented as shown in

Fig. 2.

Fig . 2. NNVT Method for two 2-bit Binary Numbers

First, the LSB were multiplied and which produces the

LSB of the final product (vertical). Next, the least significant

bit is multiplied with the next nearer bit of the multiplier and

then sum with the product of least significant bit of multiplier

and next nearer bit of the multiplicand (crosswise).

The resulted sum gives the second bit of the final product.

The resulted carry is added with the partial product which is

attained by multiplying the MSB to give the sum and carry. In

the final product, the carry be fourth bit and the sum is the

third bit.

This 2X2 Vedic multiplier module can be implemented

using four input AND gates & two half-adders as

specified in the block diagram shown in Fig. 3. Very precisely,

the total delay is only 2-half adder delays [7], after the

generation of final bit products, which is very similar to Array

multiplier.

Fig. 3. Block Diagram of 2x2 bit Vedic Multiplier

Thus we can switch over to the implementation of 4x4 bit

Vedic multiplier which makes use of the 2x2 bit multiplier as

a basic building block. The similar technique can be extended

for both input bits 4 & 8. But in case of higher no. of input

bits, little modification is required.

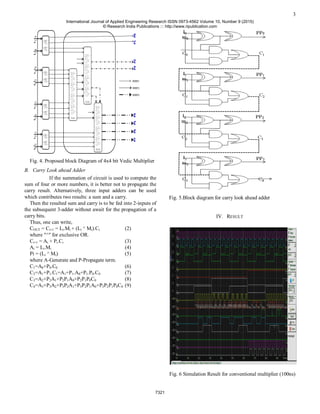

2) Vedic Multiplier for 4x4 Module

The 4x4 bit Vedic multiplier module can be obtained by

using four 2x2 VM as shown in Fig. 3. Let‟s analyze 4x4

multiplications, say S= s3 s2 s1 s0 and T= t3 t2 t1 t0. The finial

output of multiplication result is – p7 p6 p5 p4 p3 p2 p1 p0.

Now, s and t can be divided into two parts, t3 t2 & t1 t0 for T

and s3 s2 & s1 s0 for S. multiplication process is done by using

the fundamental of Vedic multiplication, that is, taking two bit

at a time and using 2 bit multiplier block and then addition

process is done using carry look-ahead adder. The

multiplication process is represented by the structure shown in

Fig. 4.

International Journal of Applied Engineering Research ISSN 0973-4562 Volume 10, Number 9 (2015)

© Research India Publications ::: http://www.ripublication.com

7320](https://image.slidesharecdn.com/d3b1009d-3ebc-4e5e-9b0d-d6a1f4e37e8d-160716150648/85/JOURNAL-PAPER-2-320.jpg)

![4

V. CONCLUSION

Thus the low power multiplier has been designed using the

New Vedic VLSI Technique (NVVT). This multiplier is

designed with two different types of adder viz., ripple carry

adder and carry look-ahead adder and the obtained power

results were compared. Based on these power results, it has

been shown that carry look ahead adder is more efficient than

the other and the power difference between them is 23.592

µw. Hence our motivation to reduce power if finely fulfilled.

This work can be used for high speed DSP processor

applications.

VI. FUTURE WORK

The power obtained from proposed multiplier is to

decreased further by using a block Enable Technique

REFERENCES

[1] Neil H.E. Weste, David Harris and Ayan Banerjee, CMOS VLSI Design

, A circuits and system perspective, 3rd Edition, Pearson Education,

2005, pp. 345-358.

[2] M.Mottaghi Dastjerdi ,A.afzali Kusha,m.Pedram “BZFAD A Low

Power Low Area Multiplier Based on Shift and Add Architecture” IEEE

Trans. Very Large Scale Integr .(VLSI)Syst., Vol.17, no-2,pp302-306,

Feb. 2009.

[3] Nishat Bano (2012) “VLSI Design of Low Power Booth Multiplier”

International Journal of Scientific & Engineering Research. Vol. 3,

Issue 2, pp421-423, Feb.2012.

[4] Jagadeshwar Rao M, Sanjay Dubey (2012) “A High Speed Wallace Tree

Multiplier Using Modified Booth Algorithm for Fast Arithmetic

Circuits” IOSR Journal of Electronics and Communication Engineering

(IOSRJECE). Vol.3, Issue 1, PP 07-11, Oct. 2012.

[5] A. Aggoun, A.F. Farwan, M.K. Ibrahim and A. Ashur (2004) “Radix-2n

serial–serial multipliers” IEE Proc.-Circuits Devices System.. Vol. 151,

no. 6, pp503-509, Dec.2014.

[6] Swami Bharati Krishna Tritha, Vedic Mathematics, Motilal Banarsidass

Publisher, 1991, pp.26-35.

[7] Rejisha Krishnan, Mr.S.Vijayakumar, “Multiplierless FIR Filter Design

using Global Valued Numbering and Architecture” International

Computing, Communication and Networking Technologies (ICCCNT),

July.2014.

Fig. 7. Simulation Result for proposed multiplier (100ns)

TABLE I

POWER COMPARISONS PROPOSED AND CONVENTIONAL

MULTIPLIER

Type Power (µw)

10(ns) 100(10ns) 200(ns)

Conventional

multiplier

65.46µw 131 µw 149µw

Proposed

multiplier

41.868 µw 96.040 µw 123µw

Graph.1 conventional versus Proposed Multiplier

0

20

40

60

80

100

120

140

160

Conventional

Multiplier

Proposed

Multiplier

10 ns

100ns

200ns

International Journal of Applied Engineering Research ISSN 0973-4562 Volume 10, Number 9 (2015)

© Research India Publications ::: http://www.ripublication.com

7322](https://image.slidesharecdn.com/d3b1009d-3ebc-4e5e-9b0d-d6a1f4e37e8d-160716150648/85/JOURNAL-PAPER-4-320.jpg)