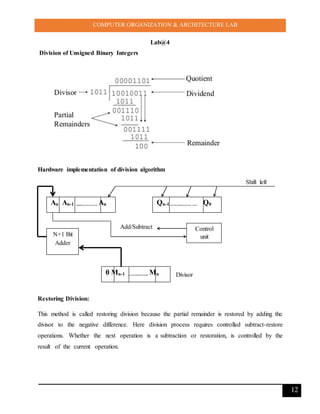

This document contains information about a computer organization and architecture lab. It includes details about the lab report format, integer representation using fixed point, two's complement, addition and subtraction algorithms and hardware. It also discusses logical operations, and provides MATLAB code examples for 4-bit binary addition, subtraction, multiplication and restoring division algorithms.

![COMPUTER ORGANIZATION & ARCHITECTURE LAB

5

Main program to add two unsigned binary number [4 bit binary adder]

%******* Main Program Code*******%

display('Enter First Binary Sequence')

for i=1:4

a(i)=input('');

end

display('Enter Second Binary Sequence')

for i=1:4

b(i)=input('');

end

carry=0;

for i=4:-1:1

c(i)=xors(xors(a(i),b(i)),carry);

carry=ors(ands(a(i),b(i)),ands(xors(a(i),b(i)),carry));

end

%*******************************************

fprintf('%d',a)

fprintf('n')

fprintf('%d',b)

fprintf('+n')

display('=====================')

fprintf('%d%d',carry,c)

fprintf('n')

Function for AND operation

function [res] = ands(a,b)

if(a==1) && (b==1)

res=1;

else

res=0;

end

end

Function for XOR operation

function [res]= xors(a,b)

if (a~=b)

res=1;

else

res=0;

end

end

Function for OR operation

function [res] = ors(a,b)

if (a==0) && (b==0)

res=0;

else

res=1;

end

end](https://image.slidesharecdn.com/computerorganizationandarchitecturelabmanual-180122124043/85/Computer-organization-and-architecture-lab-manual-5-320.jpg)

![COMPUTER ORGANIZATION & ARCHITECTURE LAB

6

Lab@2

%%***** Matlab code for subtraction *******%%

display('Enter First Number')

for i=1:4

a(i)=input('');

end

display ('Enter Second Number')

for i=1:4

b(i)=input('');

end

%%2's complement of Second Sequence

for i=1:4

b(i)=xor(1,b(i));

end

c=1;% for 2's complement we add 1 so initialize carry as 1

for i=4:-1:1

[s (i) c] = adder ( a(i) , b(i) , c);

end

display('result')

%% Carry decide the result is in negative or positive. ifCayy is 0 then

%% result is negative else result is positive

if (c==0)

for (i=1:4)

s(i) = xor(1,s(i));

end

car=1;

for (i=4:-1:1)

[s(i) , car] = adder(s(i),0,car);

end

%display('Negative')

fprintf('-')](https://image.slidesharecdn.com/computerorganizationandarchitecturelabmanual-180122124043/85/Computer-organization-and-architecture-lab-manual-6-320.jpg)

![COMPUTER ORGANIZATION & ARCHITECTURE LAB

7

fprintf('%d',s)

else

%display('Positive')

fprintf('+')

fprintf('%d',s)

end

% Plotting input and output

subplot(3,1,1)

stem(a,'R');

xlabel('First sequence');

subplot(3,1,2);

stem(b,'G');

xlabel('Second Sequence');

subplot(3,1,3);

stem(s,'B');

xlabel('Result(a-b)');

Function for Addition Operation

function [res,car] = adder(a,b,c)

res= xor(xor(a,b),c);

car= or(and(a,b),and(xor(a,b),c));

end](https://image.slidesharecdn.com/computerorganizationandarchitecturelabmanual-180122124043/85/Computer-organization-and-architecture-lab-manual-7-320.jpg)

![COMPUTER ORGANIZATION & ARCHITECTURE LAB

10

%% Matlab code for Multiplication of two unsigned 4-bit binary number

clearall;

closeall;

R=[0 0 0 0 0 0 0 0];

display('Enter First Number');

for i=5:8

A(i)=input('');

end

display ('Enter Second Number');

for i=5:8

B(i)=input('');

end

display('***==============================***');

fprintf('Multiplicant=');

fprintf('%d',A);

fprintf('n');

fprintf('Multiplier=');

fprintf('%d',B);

fprintf('n');

fprintf('***************************');

subplot(3,1,1);

stem(A,'G');

xlabel('Multiplicant');

if(B(8)==1)

R=A;% Assign the given number First partial product

end

for i=7:-1:5

if(B(i)==1)

c=0;

for j=8:-1:1

[A(j) c]=adds(A(j),A(j),c);](https://image.slidesharecdn.com/computerorganizationandarchitecturelabmanual-180122124043/85/Computer-organization-and-architecture-lab-manual-10-320.jpg)

![COMPUTER ORGANIZATION & ARCHITECTURE LAB

11

end

c=0;

for j=8:-1:1

[ R(j) c]=adds(R(j),A(j),c);% shifting left

end

else

c=0;

for j=8:-1:1

[A(j) c]=adds(A(j),A(j),c);

end

end

end

%% Result Plotting

fprintf('n');

fprintf('Multiplication result=');

fprintf('%d',R);

fprintf('n');

display('***==============================***');

subplot(3,1,2);

stem(B,'R');

xlabel('Multiplier');

subplot(3,1,3);

stem(R);

xlabel('Result after multiplication');](https://image.slidesharecdn.com/computerorganizationandarchitecturelabmanual-180122124043/85/Computer-organization-and-architecture-lab-manual-11-320.jpg)

![COMPUTER ORGANIZATION & ARCHITECTURE LAB

14

%% Matlab Code for restoring Division algorithm [two 4-bit binary number %%

A = [ 0 0 0 0 ];

B = [0 0 0 0];

disp('Enter Dividend:')

for i=1:4

Q(i)=input('');

end

disp('Enter Divisor:')

for j=1:4

B(j)=input('');

end

%% Display Input Data

display('Dividend:');

Q

display('Divisor:');

B

%% code of 2's complement of Divisor

c=1;

for i=4:-1:1

[nB(i) c]=adds(xor(B(i),1),0,c);

end

%% Main code start

for cnt=1:4

% Shift operation (left Shift A, Q)

[A Q]=shifts(A,Q);

C=0;

% Subtraction operation (A=A-B)

for i=4:-1:1

[A(i) C]=adds(A(i),nB(i),C);

end

% Check MSB of A](https://image.slidesharecdn.com/computerorganizationandarchitecturelabmanual-180122124043/85/Computer-organization-and-architecture-lab-manual-14-320.jpg)

![COMPUTER ORGANIZATION & ARCHITECTURE LAB

15

if(A(1)==0)

Q(4)=1; % Set LSB of Q

else

Q(4)=0; % Set LSB of Q

c=0;

% Addition Operation (A=A+B)

for i=4:-1:1

[A(i) C] = adds(A(i),B(i),C);

end

end

end

%% Result Display

disp('Quotient: ')

Q

disp('Remainder: ')

A

%% Plotting Result

subplot(2,2,1);

stem(Q, 'Y');

xlabel('Dividend');

subplot(2,2,2);

stem(B,'B');

xlabel('Divisor');

subplot(2,2,3);

stem(Q,'R');

xlabel('Quotient');

subplot(2,2,4);

stem(A,'G');

xlabel('Remainder');](https://image.slidesharecdn.com/computerorganizationandarchitecturelabmanual-180122124043/85/Computer-organization-and-architecture-lab-manual-15-320.jpg)