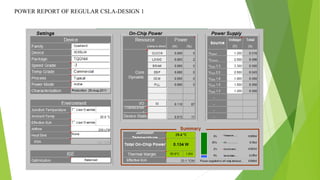

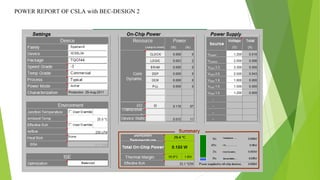

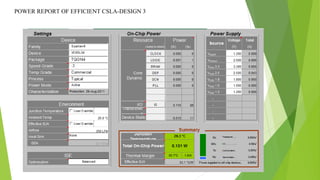

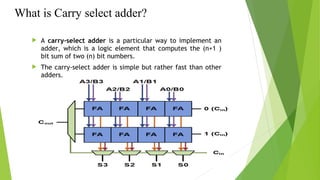

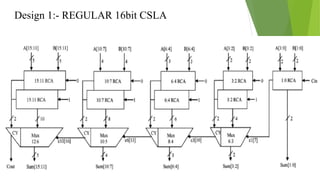

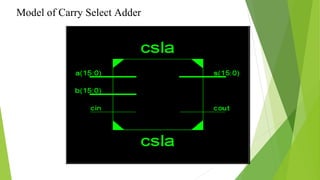

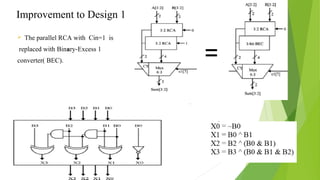

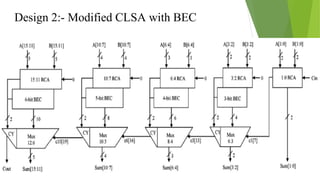

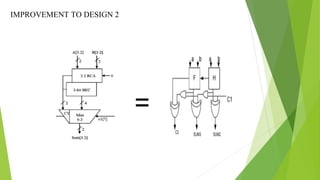

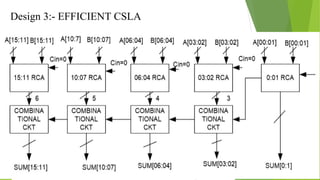

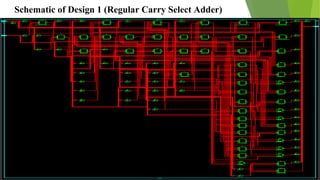

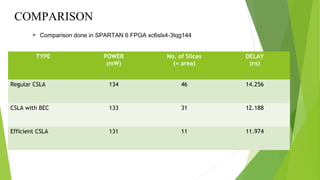

The document discusses the design and development of a carry select adder (CSLA), highlighting its importance in digital circuits for performing efficient addition. It presents three designs: a regular 16-bit CSLA, a modified version with a binary-excess converter, and an efficient CSLA, demonstrating improvements in area, power, and delay. Simulations and results indicate that the efficient CSLA offers lower power consumption and reduced area compared to traditional designs.

![REFERENCE

[1] Laxman Shanigarapu, Bhavana P. Shrivastava ”Area and power efficient carry select

adder” IJIRTS,Vol.1,2013

[2] B. Ramkumar, Harish M Kittur “Low power and Area efficient carry select

adder,”IEEE Trans,Vol.20,Feb 2012.

[3] Y. Kim and L.-S. Kim, “64-bit carry-select adder with reduced area,” Electron. Lett.,

vol. 37, no. 10, pp. 614–615, May 2001.

[4] T. Y. Ceiang and M. J. Hsiao, “Carry-select adder using single ripple carry adder,”

Electron. Lett., vol. 34, no. 22, pp. 2101–2103, Oct. 1998.

[5] Samir Palnitkar, “Verilog Hdl: A Guide to Digital Design and Synthesis”2005,2nd

Edition.

[6] J. M. Rabaey, Digtal Integrated Circuits—A Design Perspective.Upper Saddle River,

NJ: Prentice-Hall, 2001.](https://image.slidesharecdn.com/designanddevelopmentofcarryselectadder-160217075301/85/Design-and-development-of-carry-select-adder-24-320.jpg)