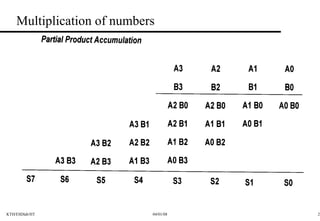

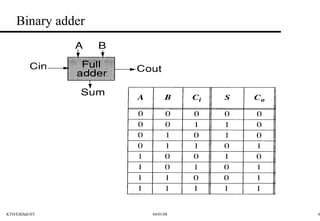

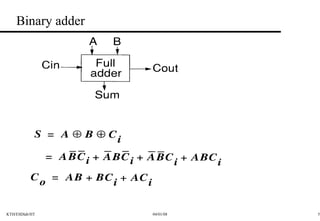

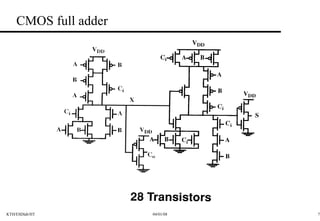

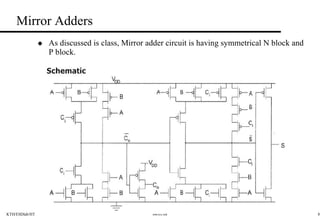

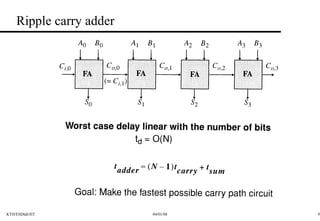

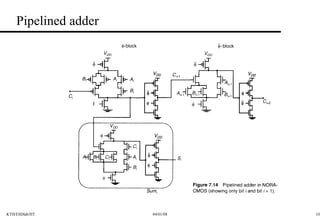

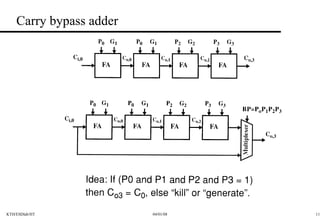

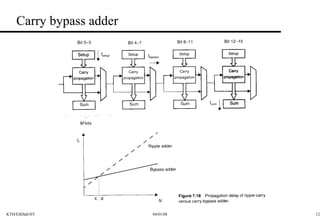

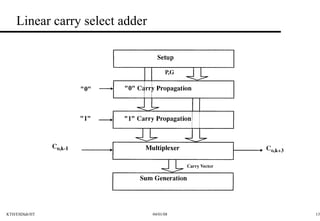

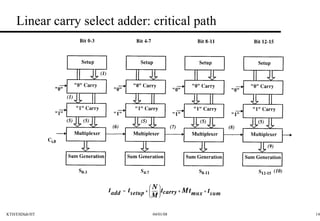

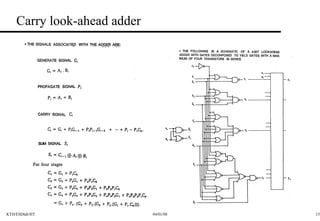

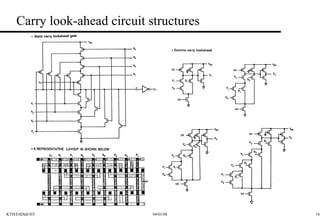

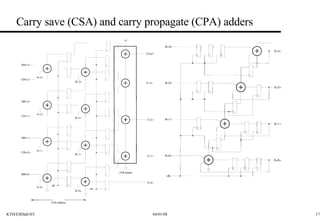

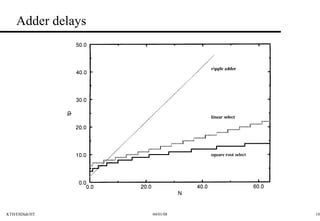

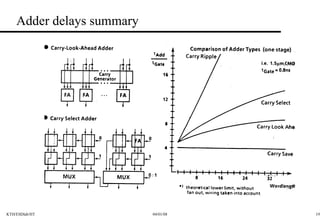

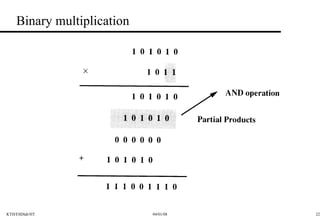

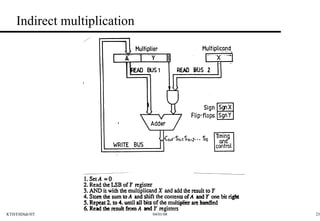

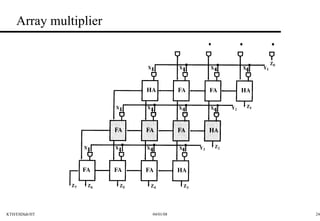

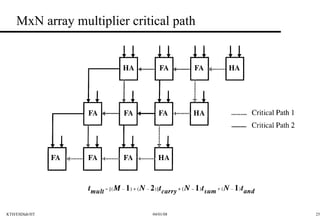

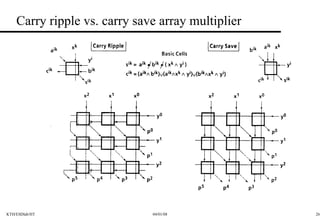

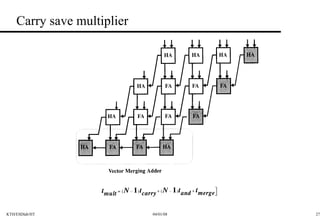

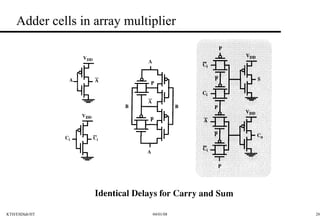

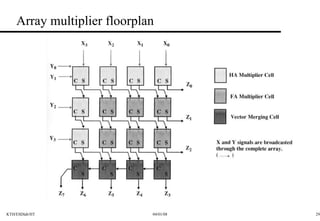

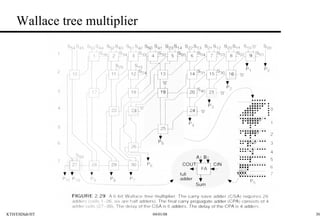

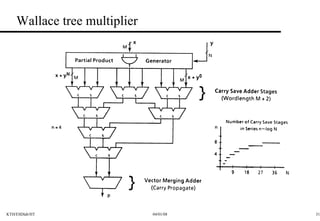

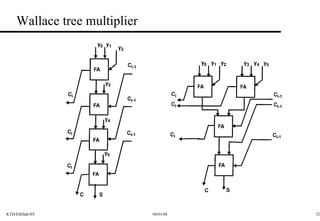

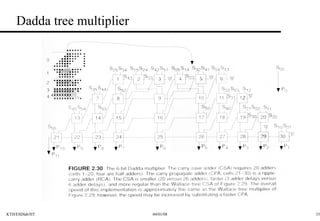

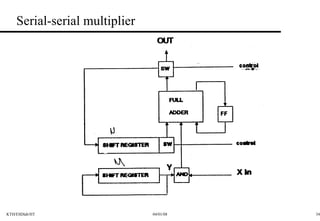

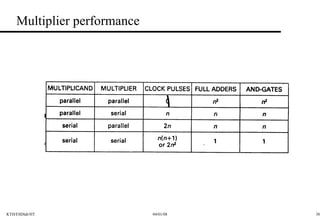

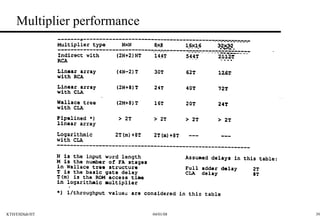

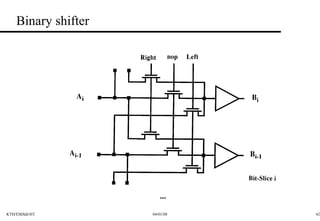

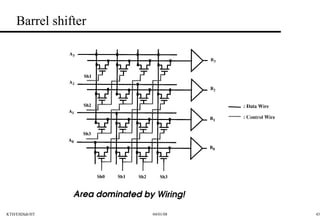

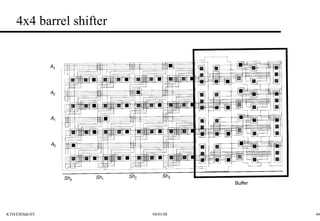

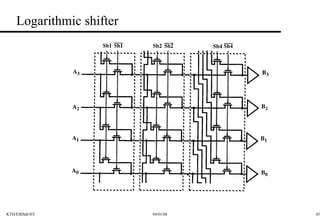

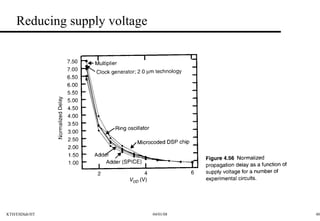

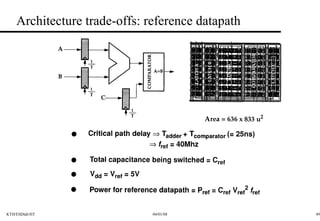

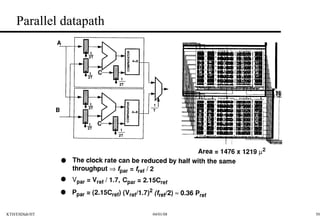

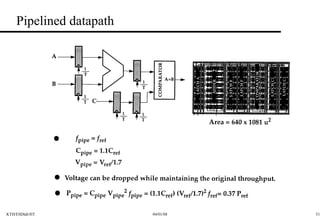

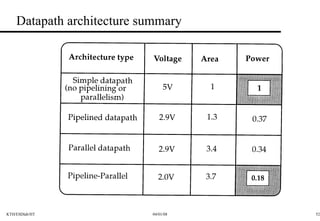

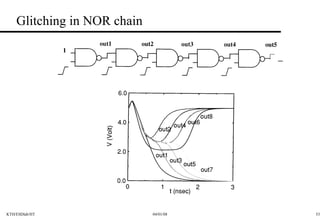

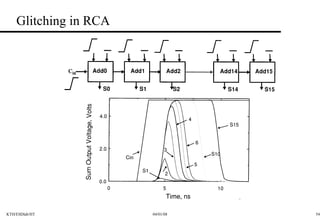

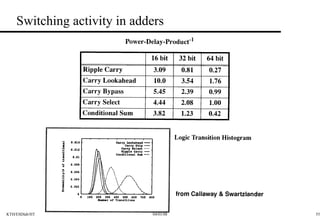

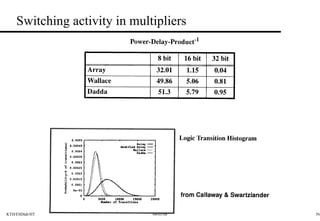

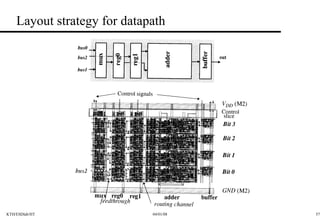

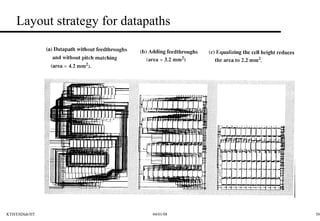

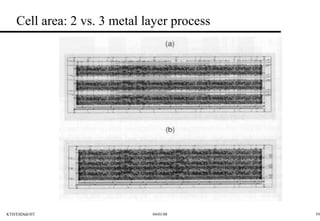

The document discusses various digital circuit techniques for arithmetic operations like addition and multiplication. It covers binary adders, full adders, ripple carry adders, carry lookahead adders, carry save adders, array multipliers, Wallace tree multipliers, and other basic datapath elements. The document also discusses design considerations like transistor count, critical path, performance, power, and layout strategies.