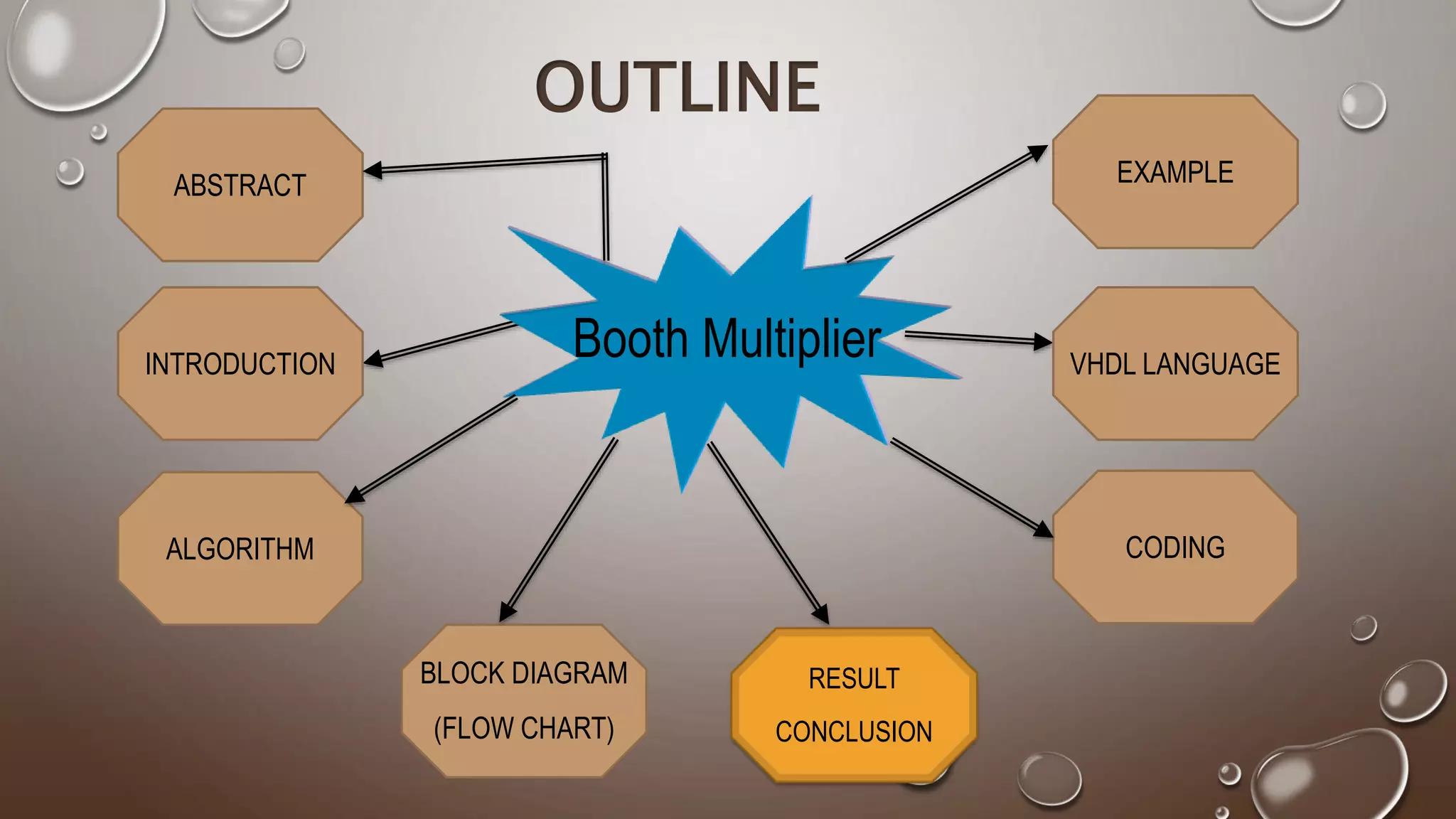

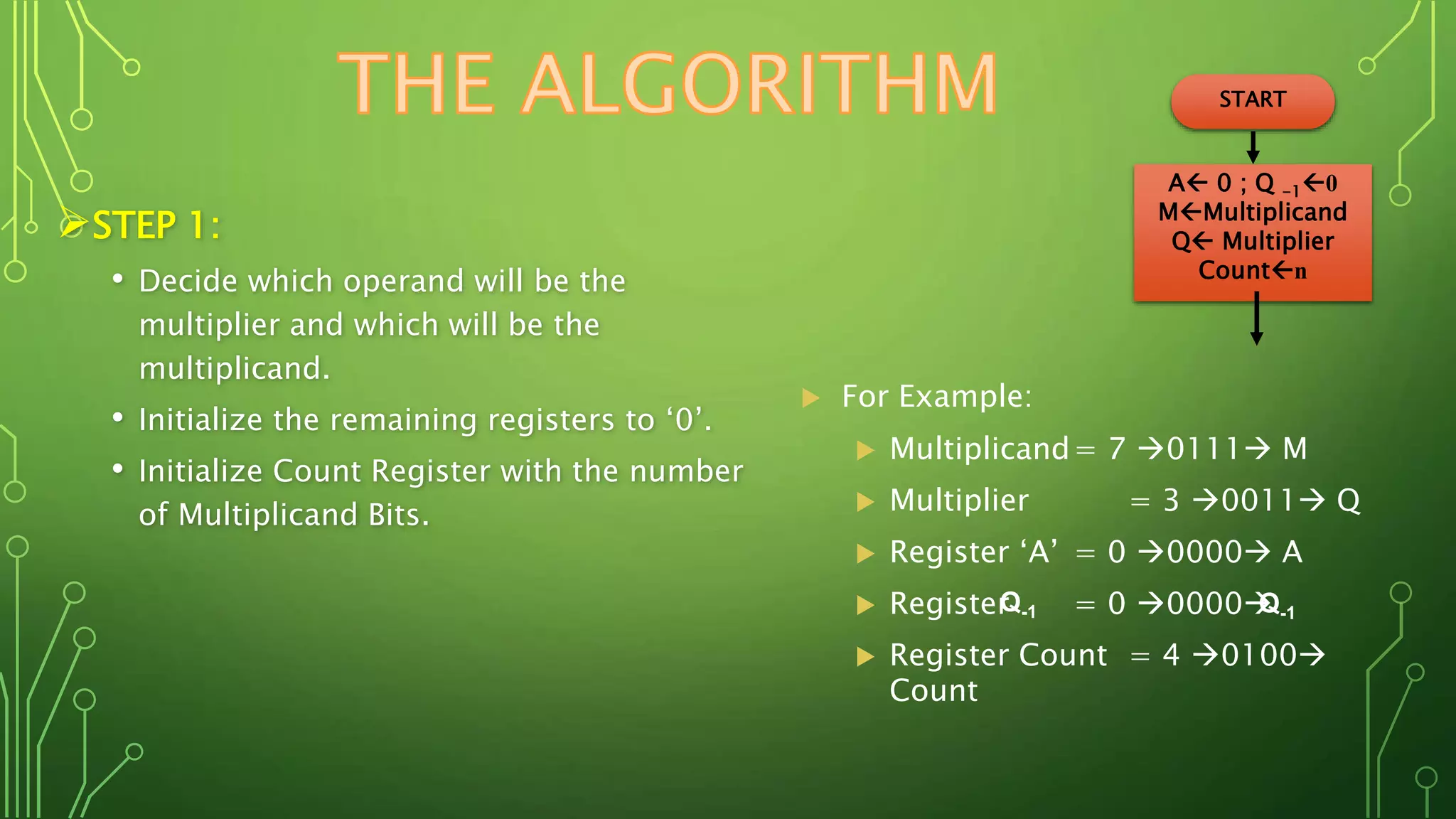

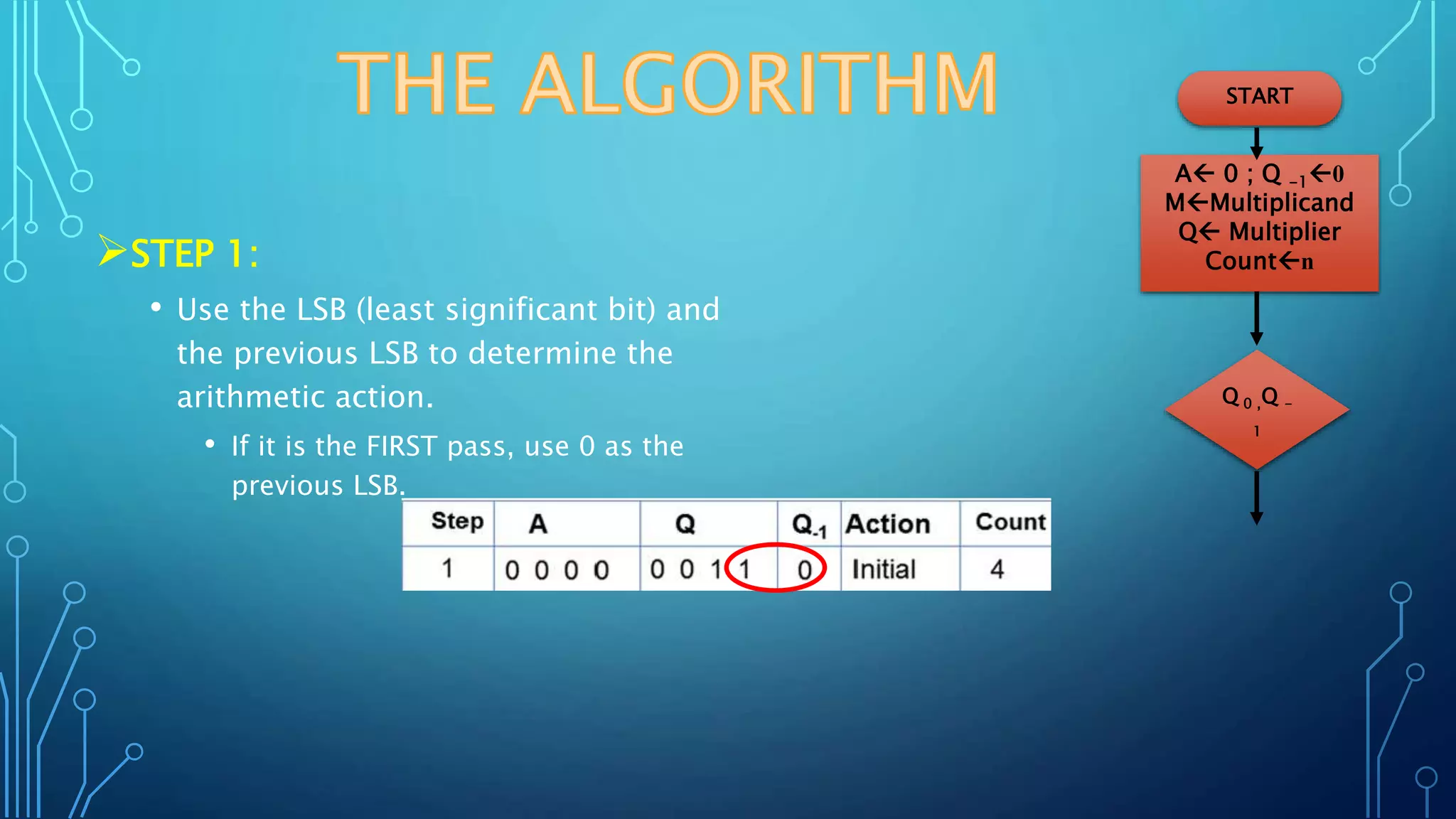

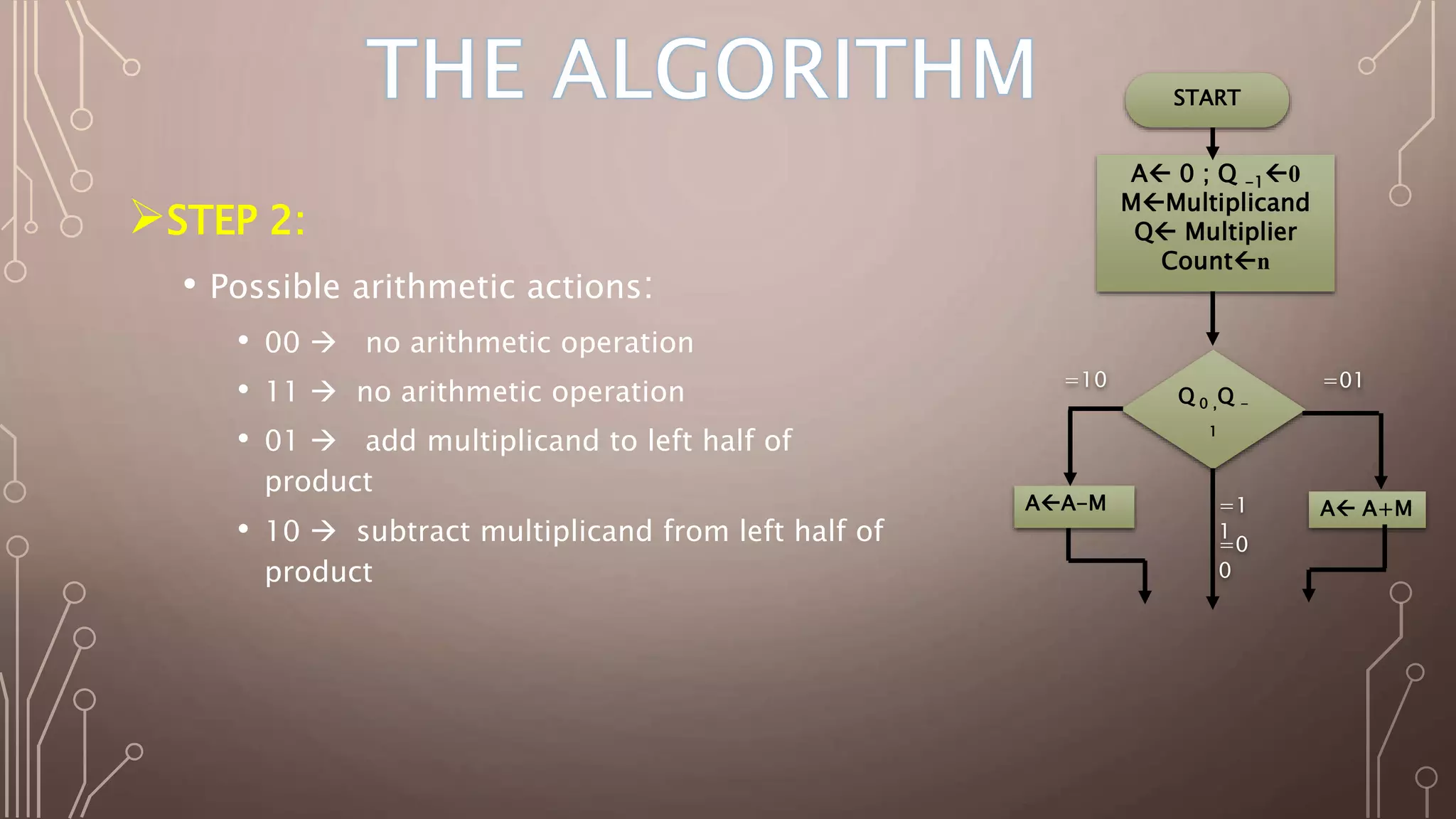

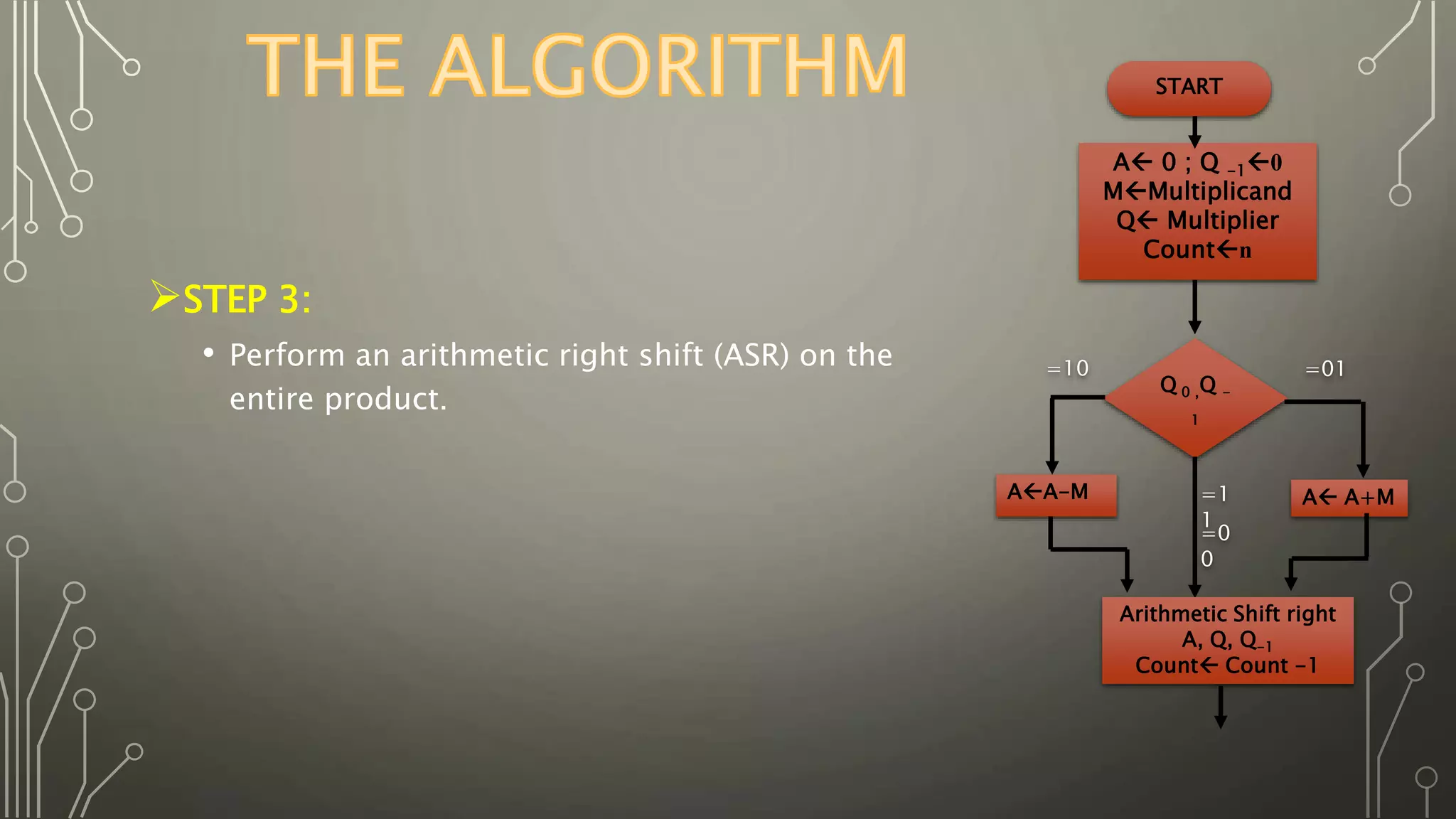

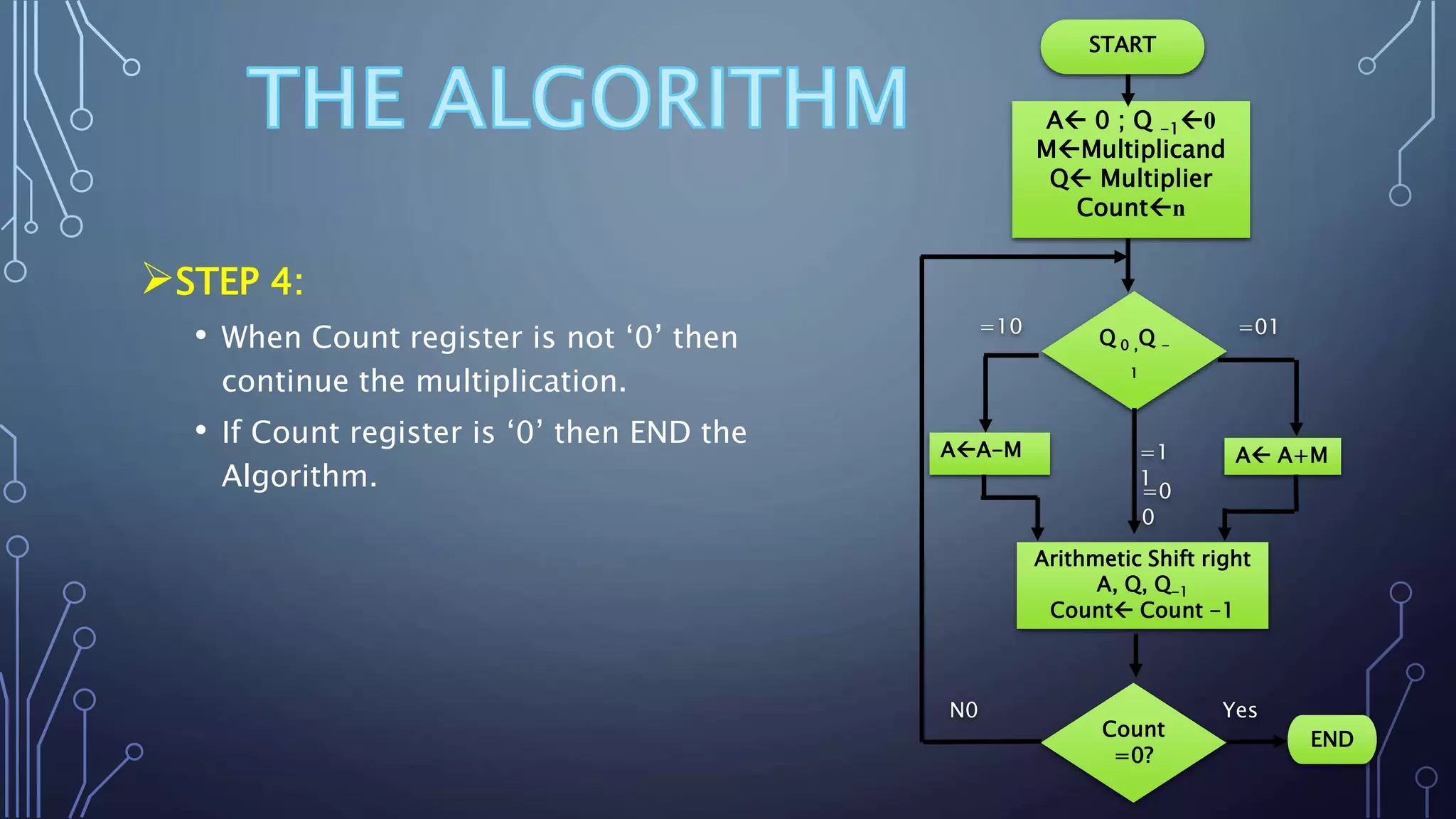

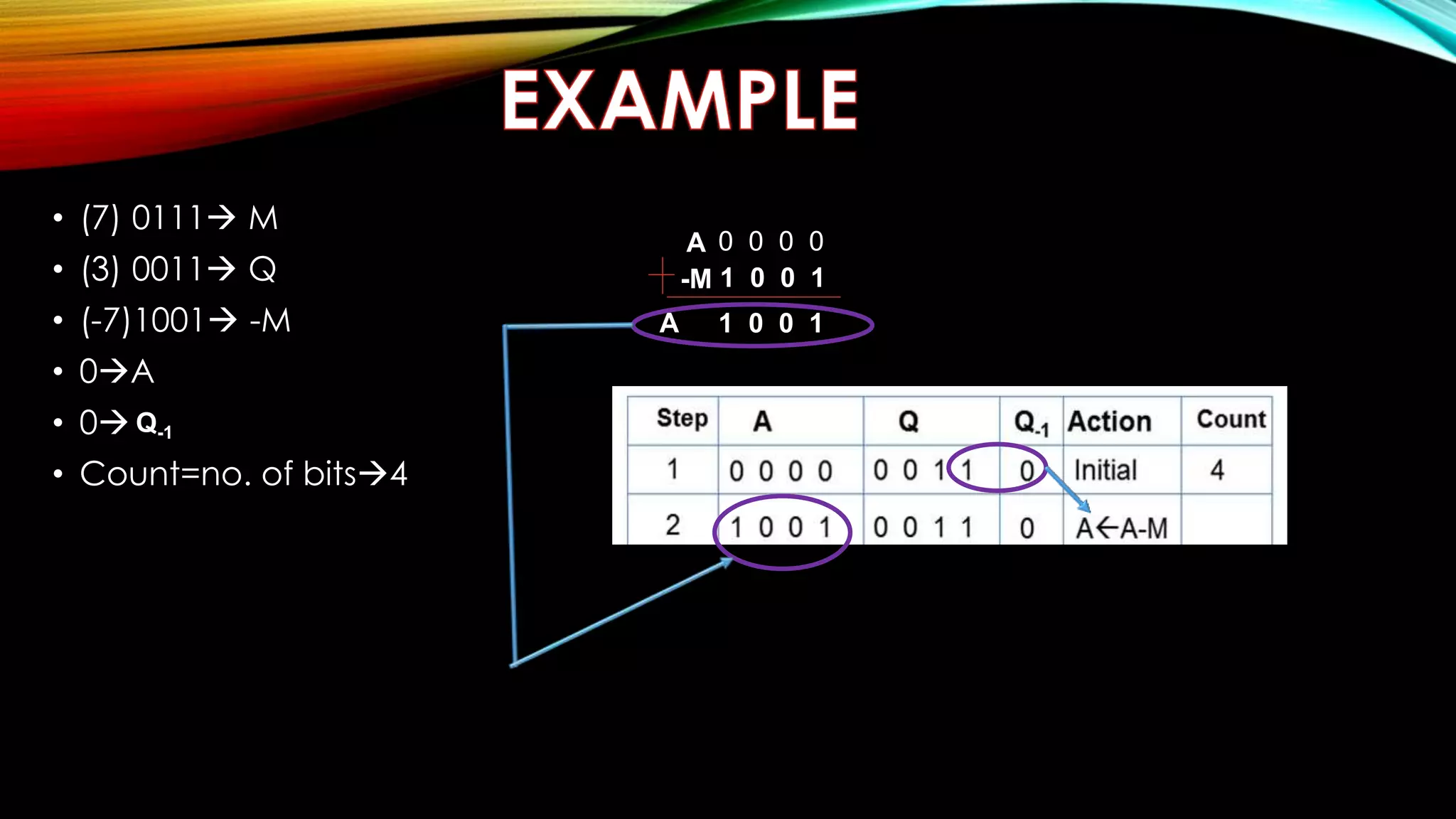

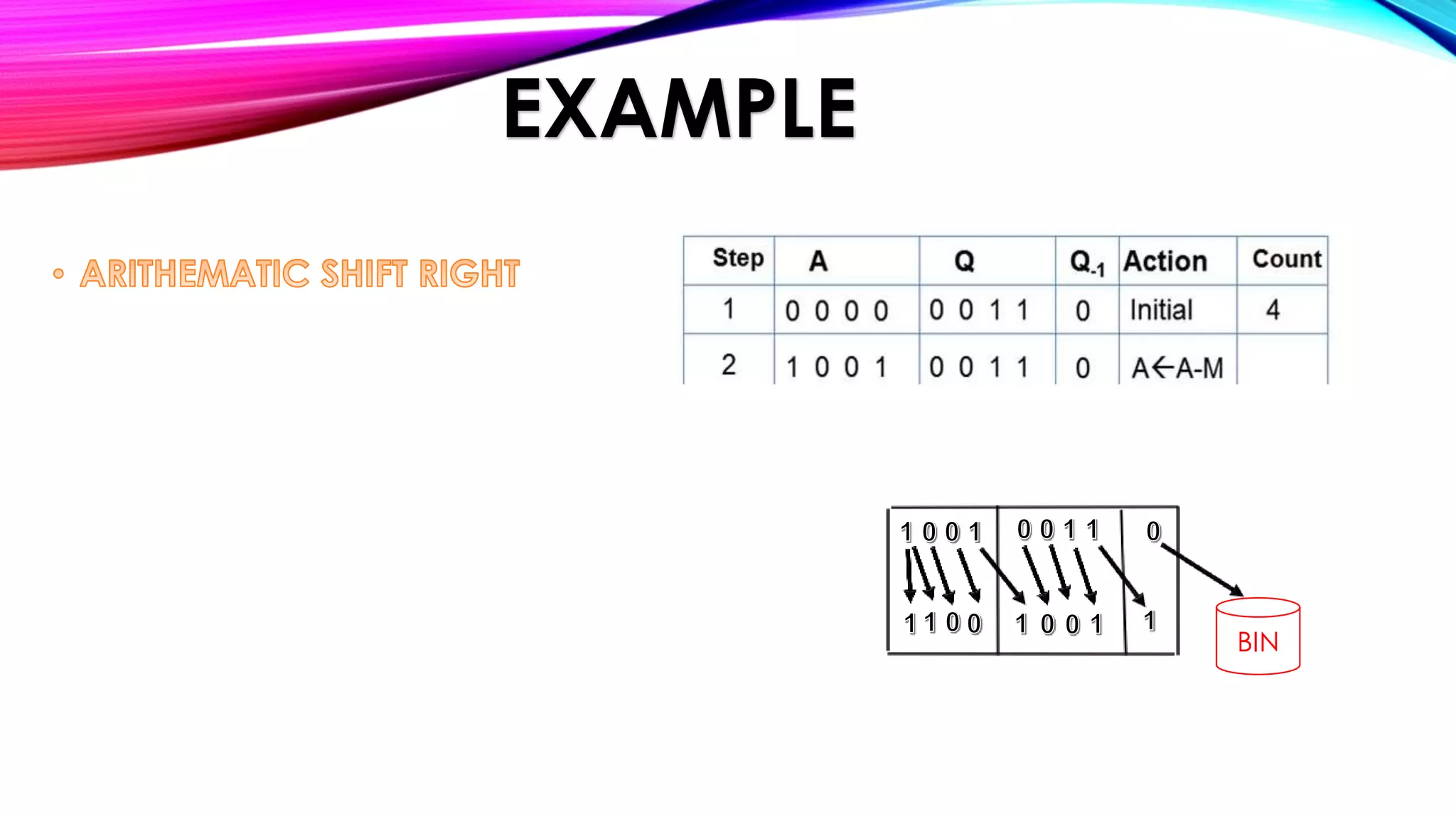

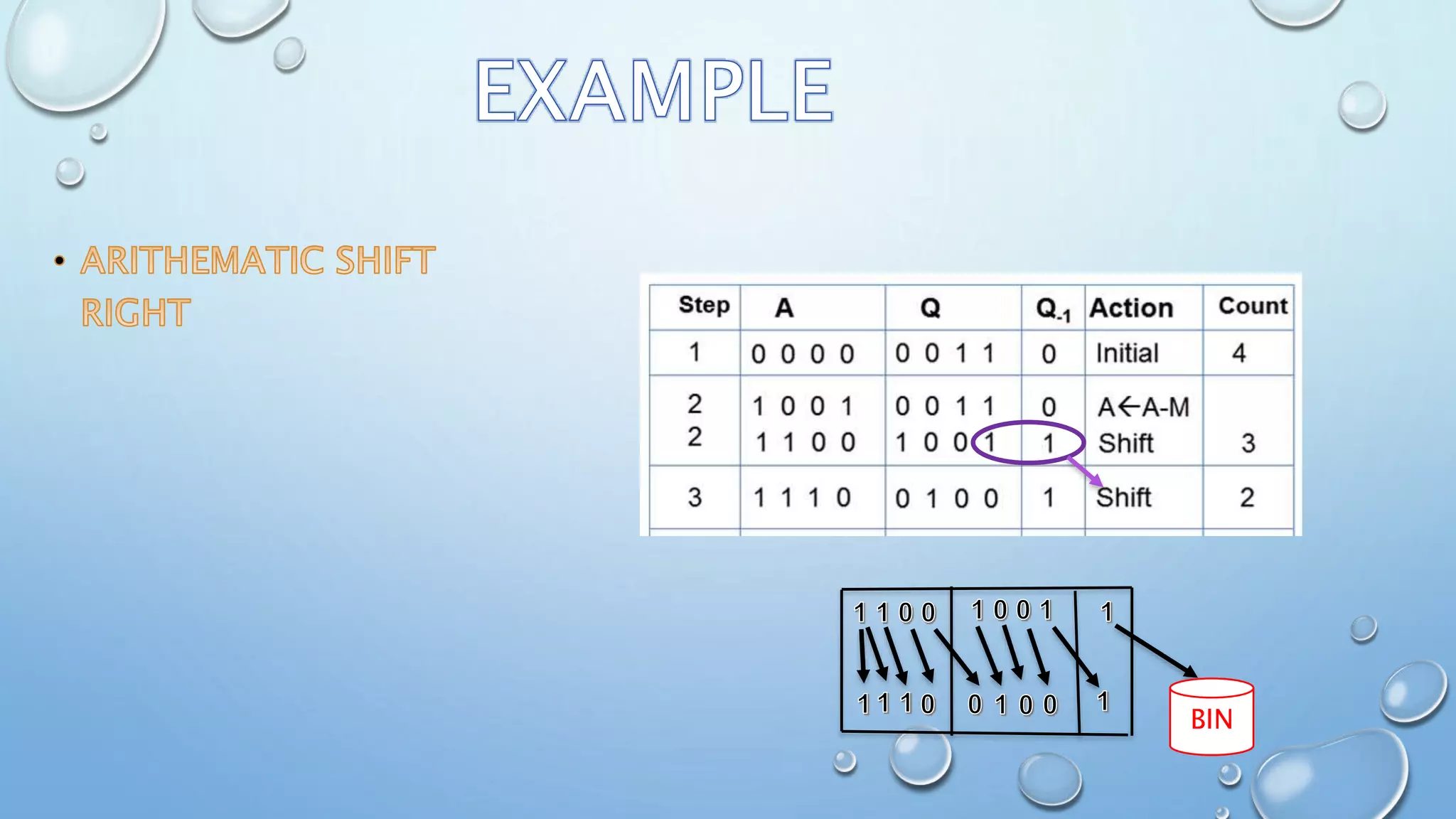

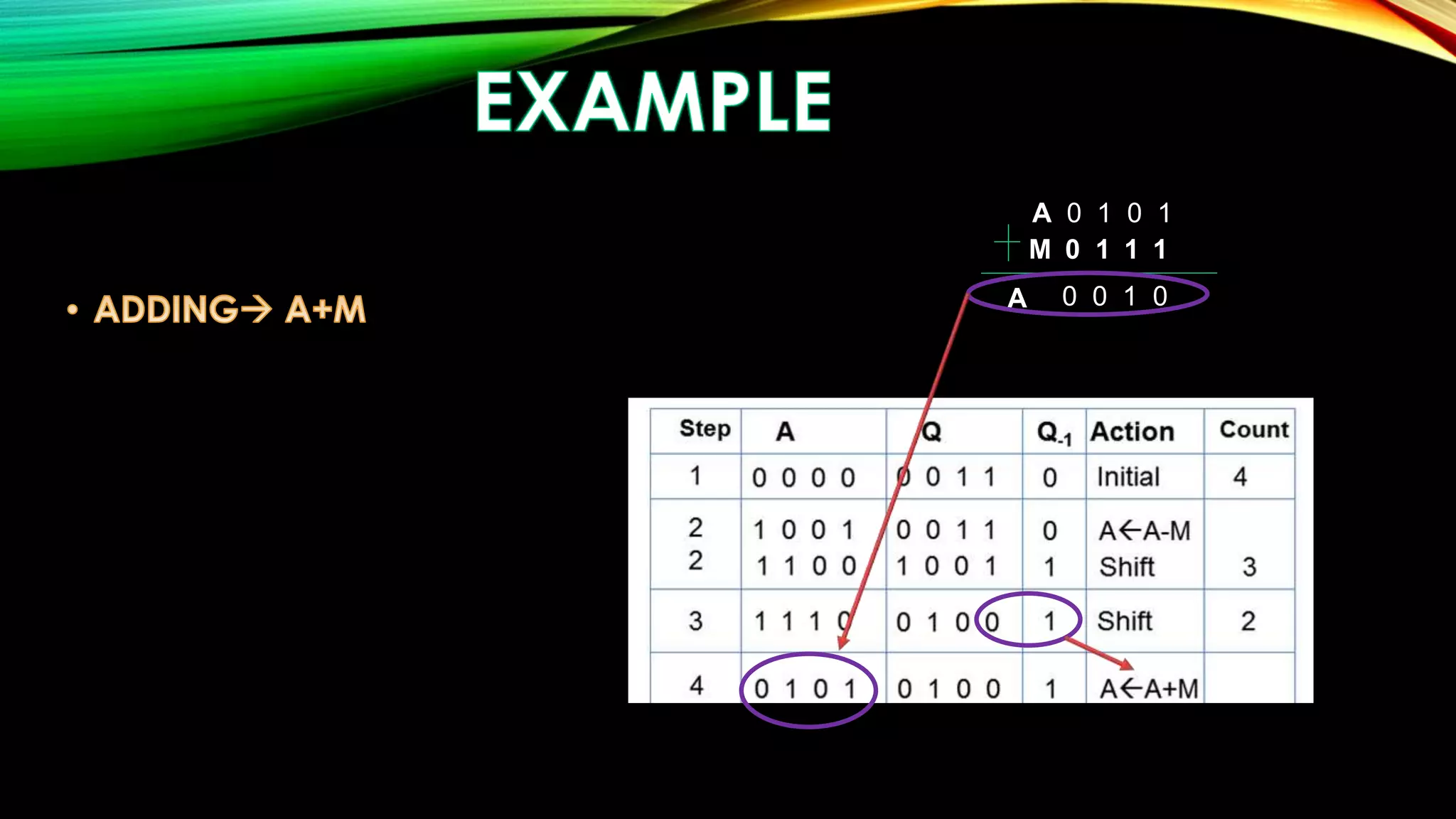

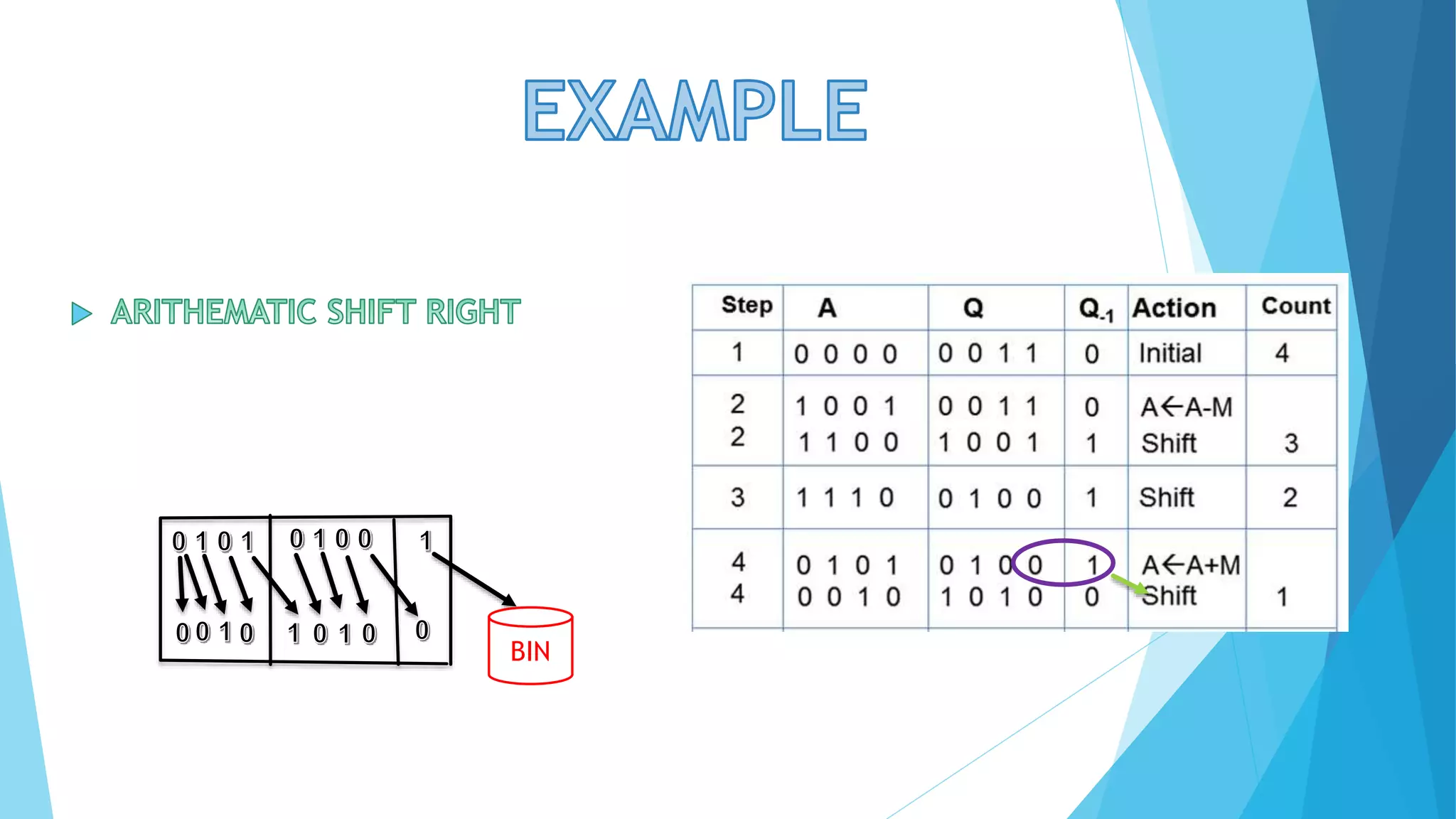

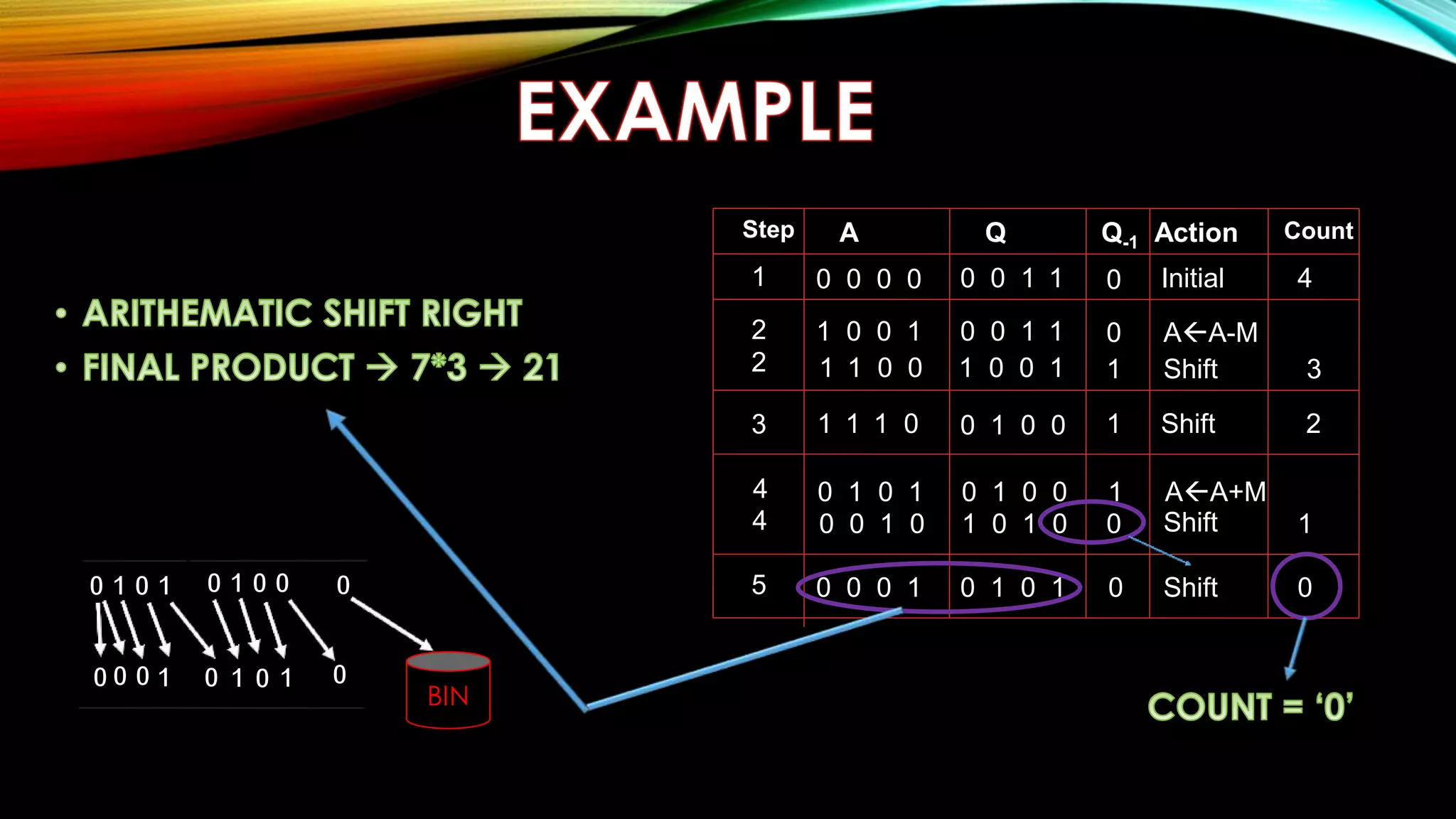

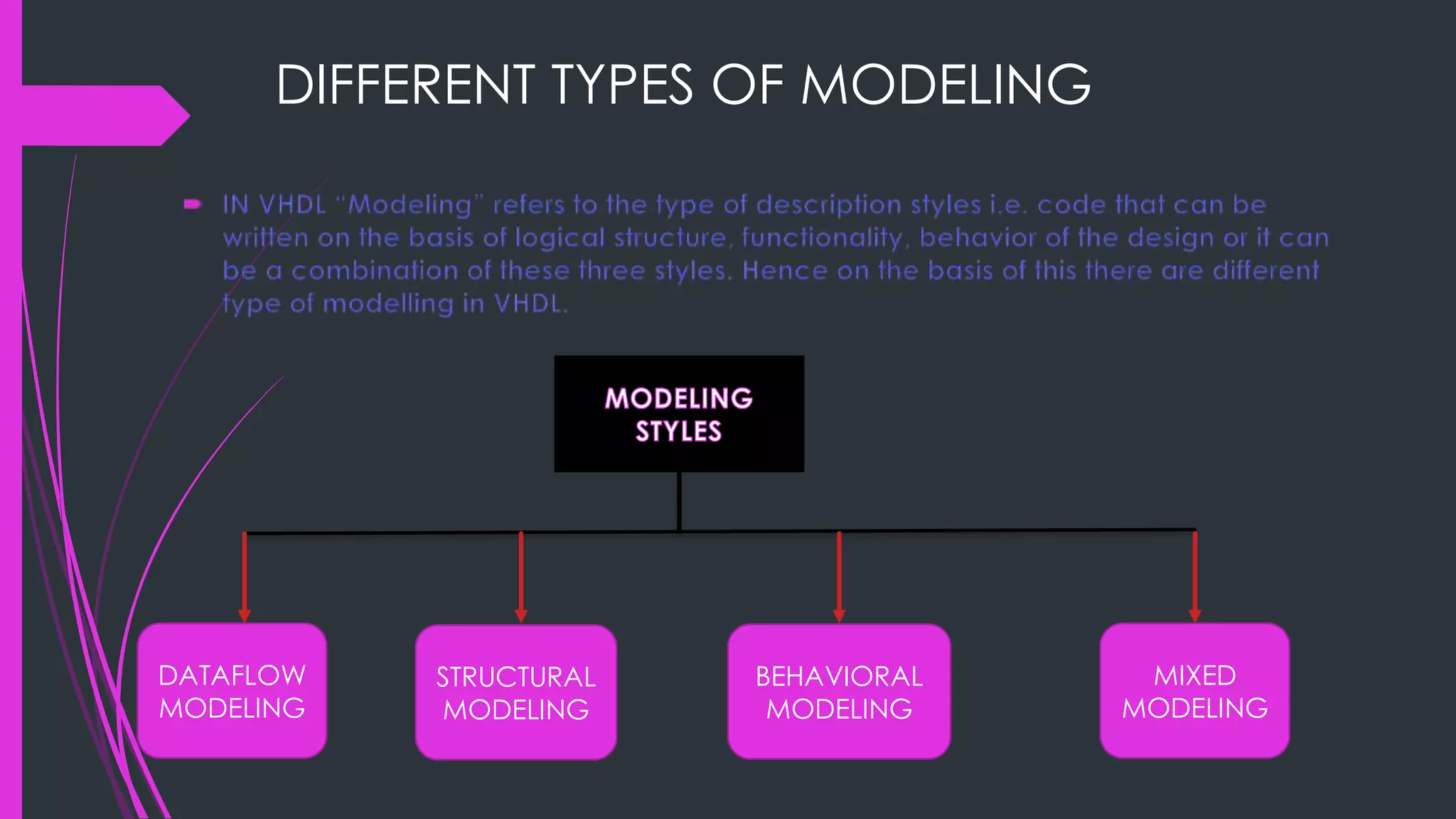

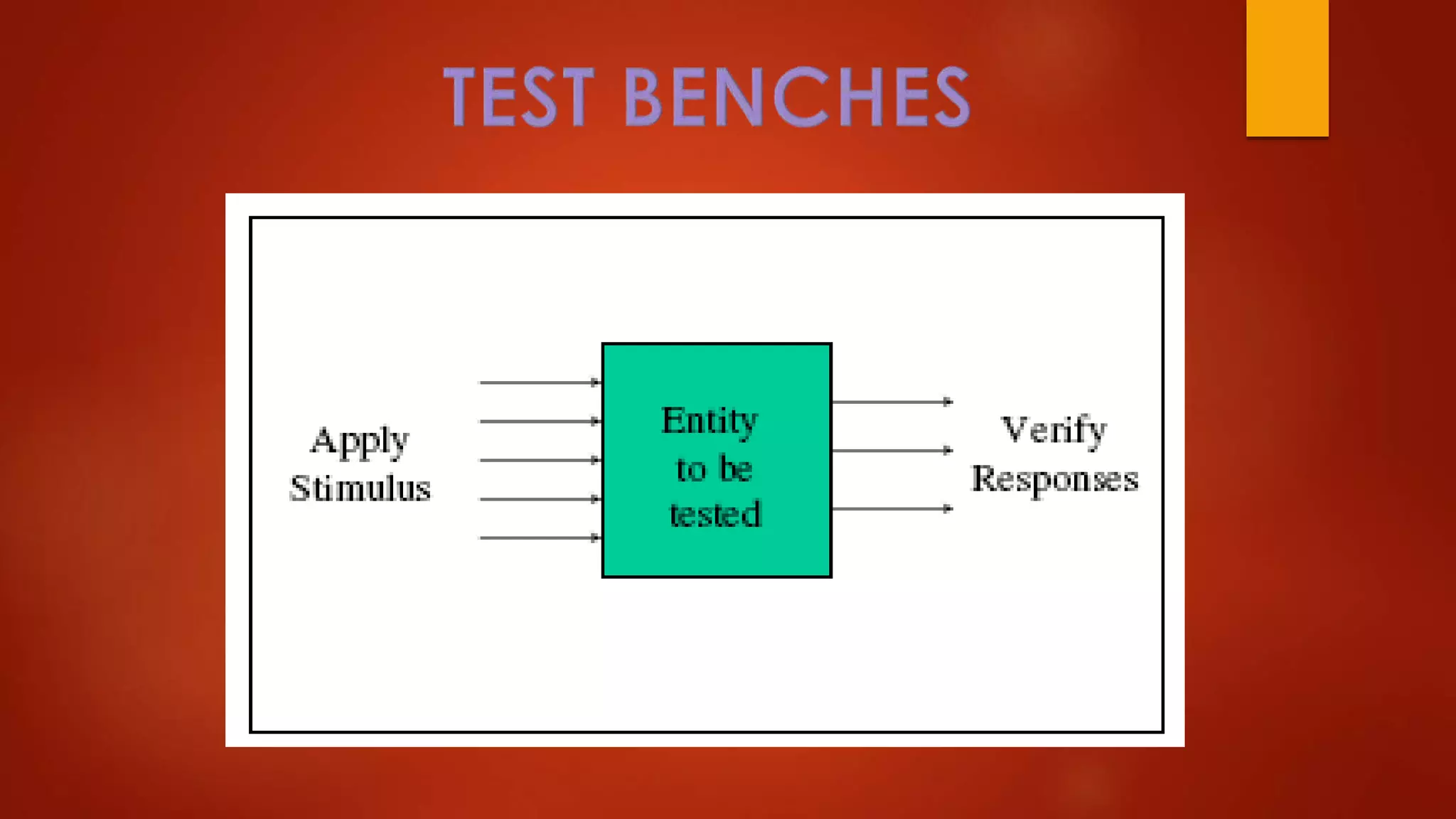

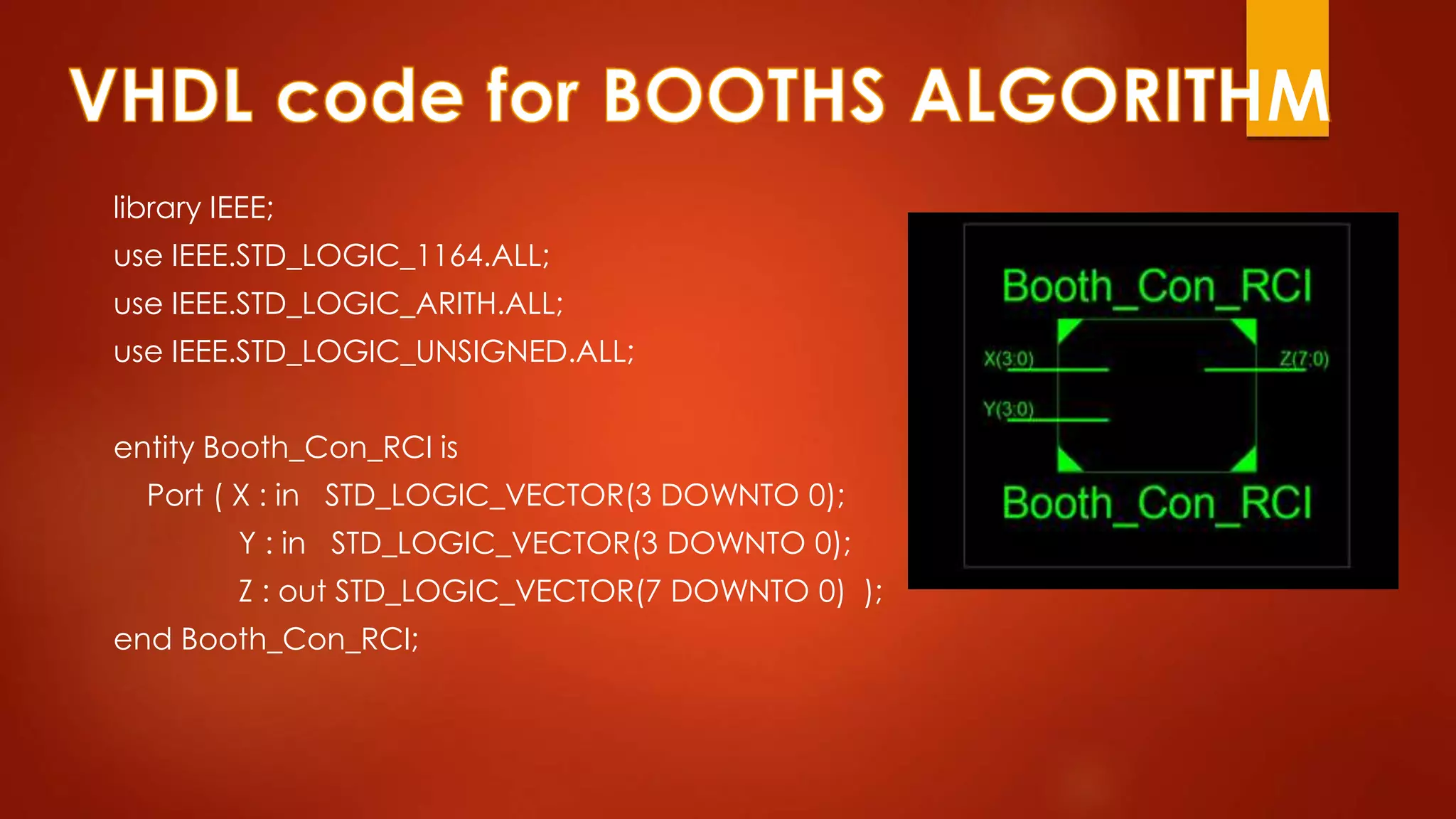

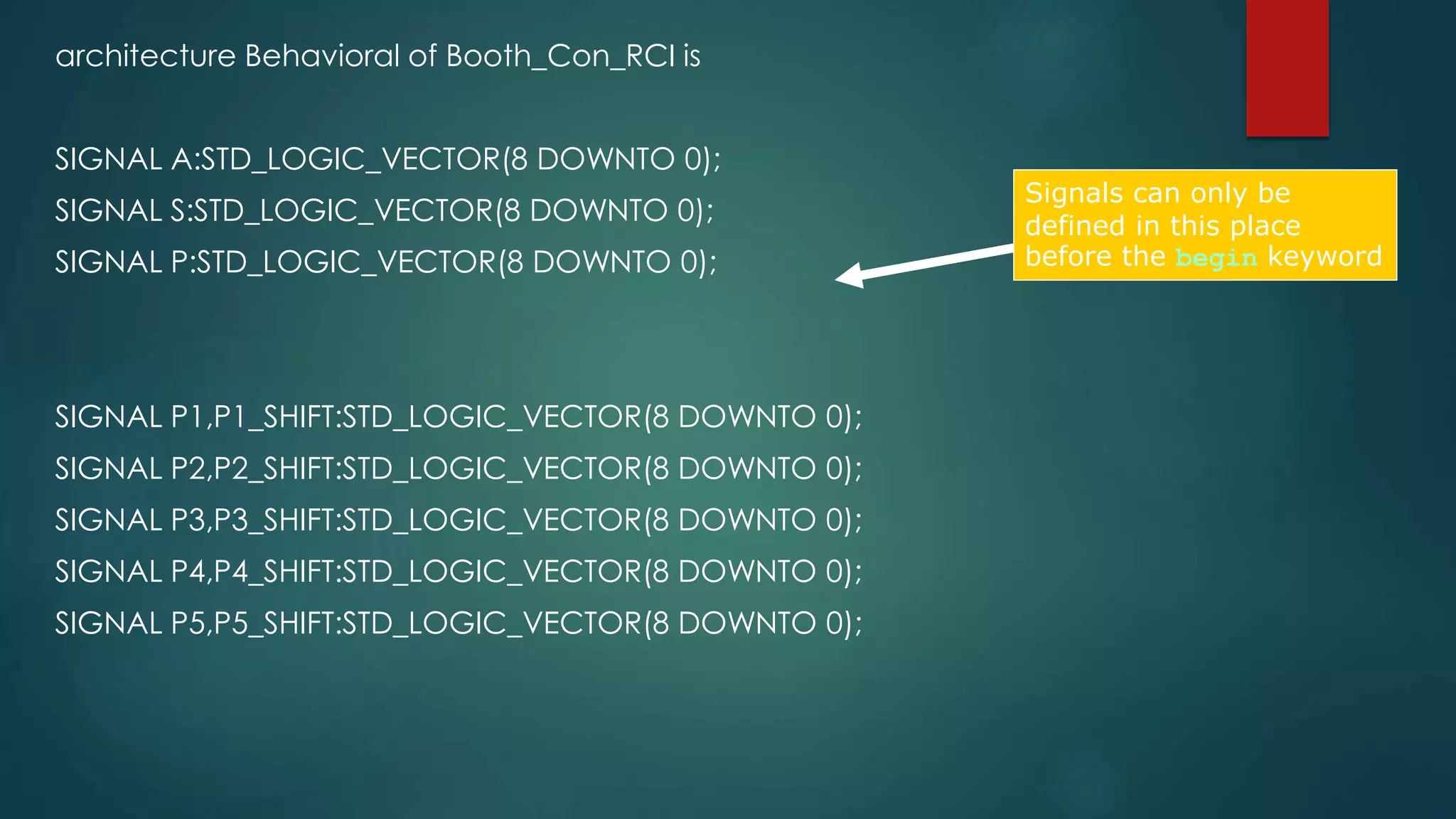

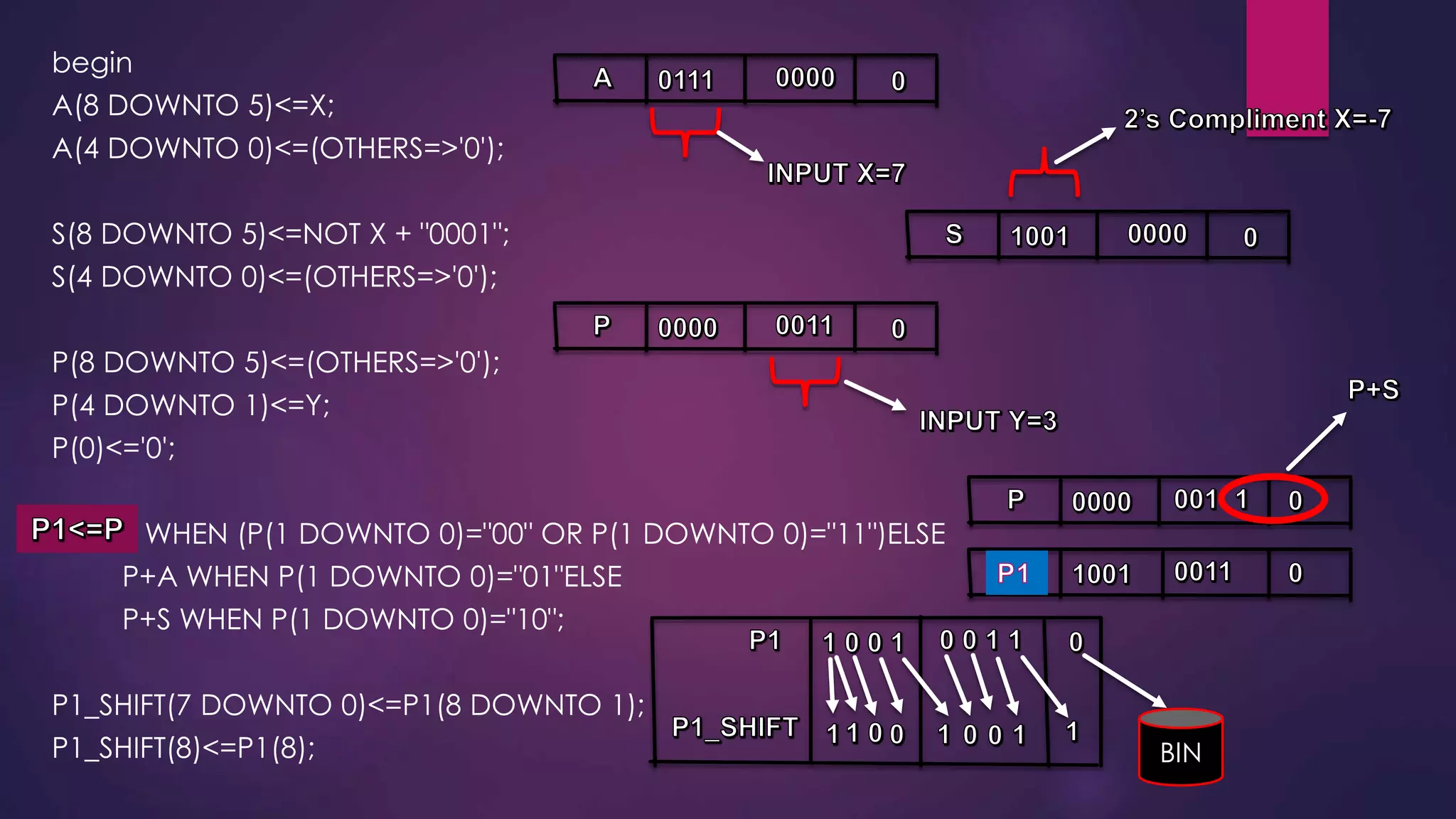

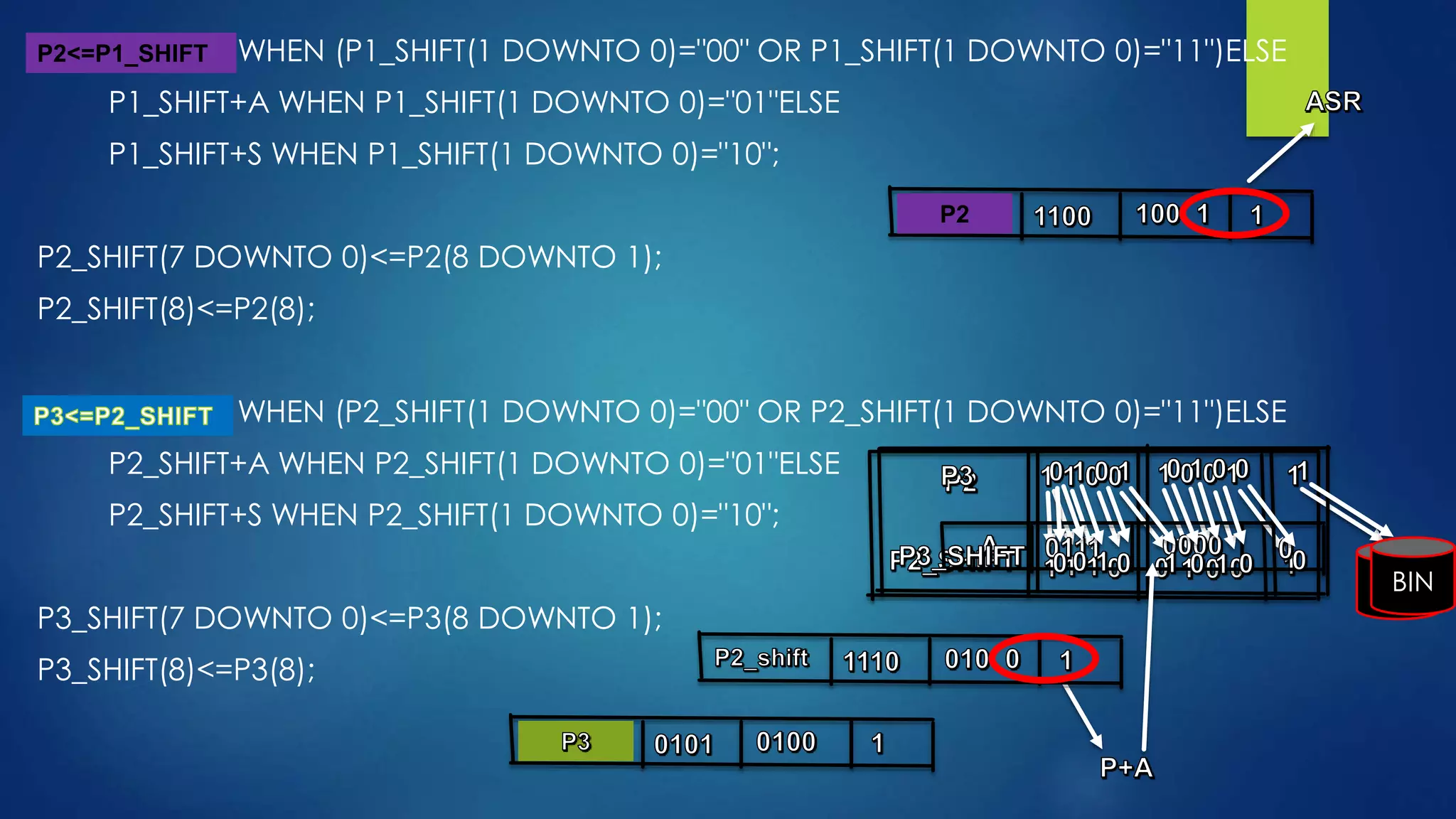

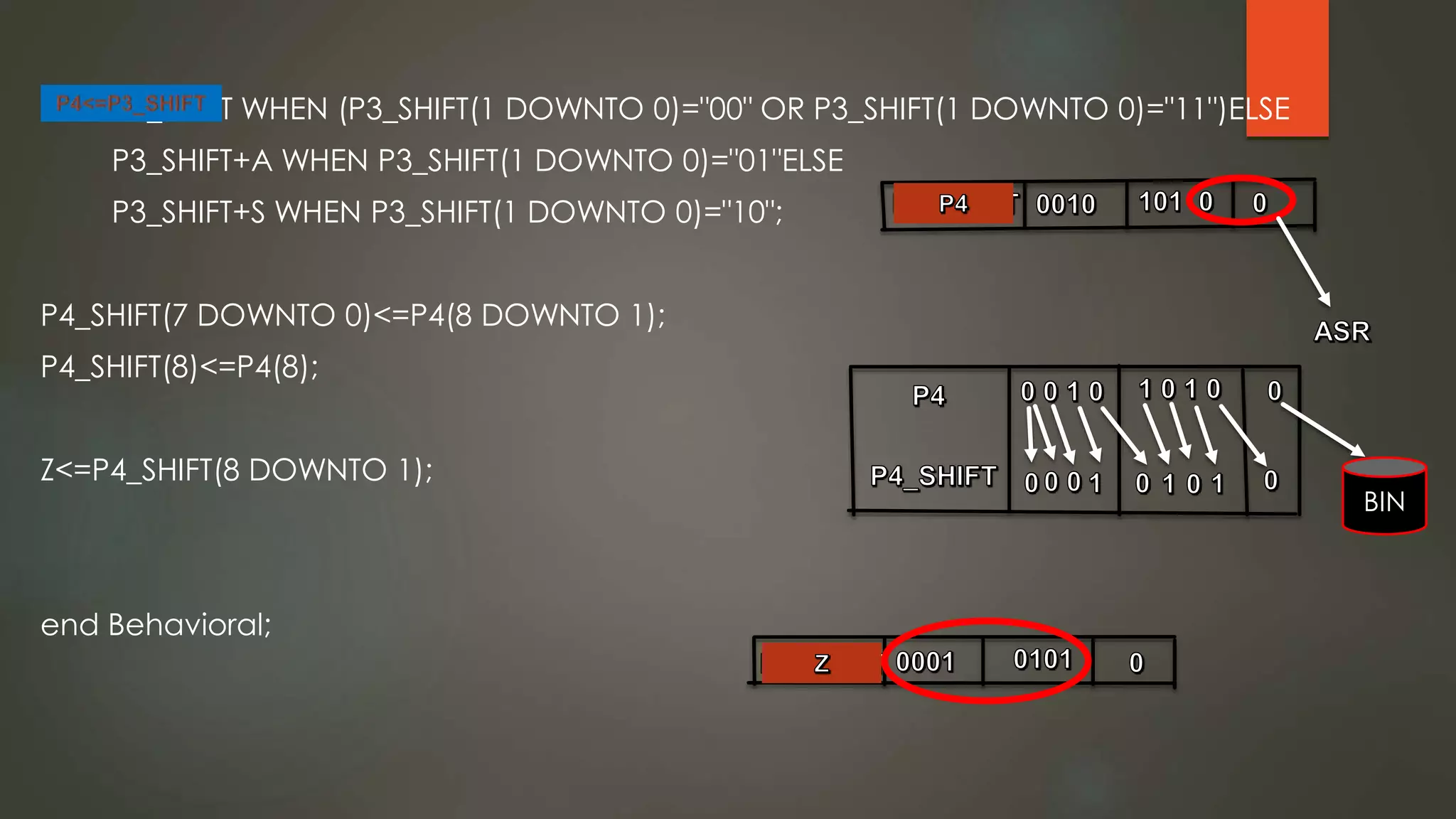

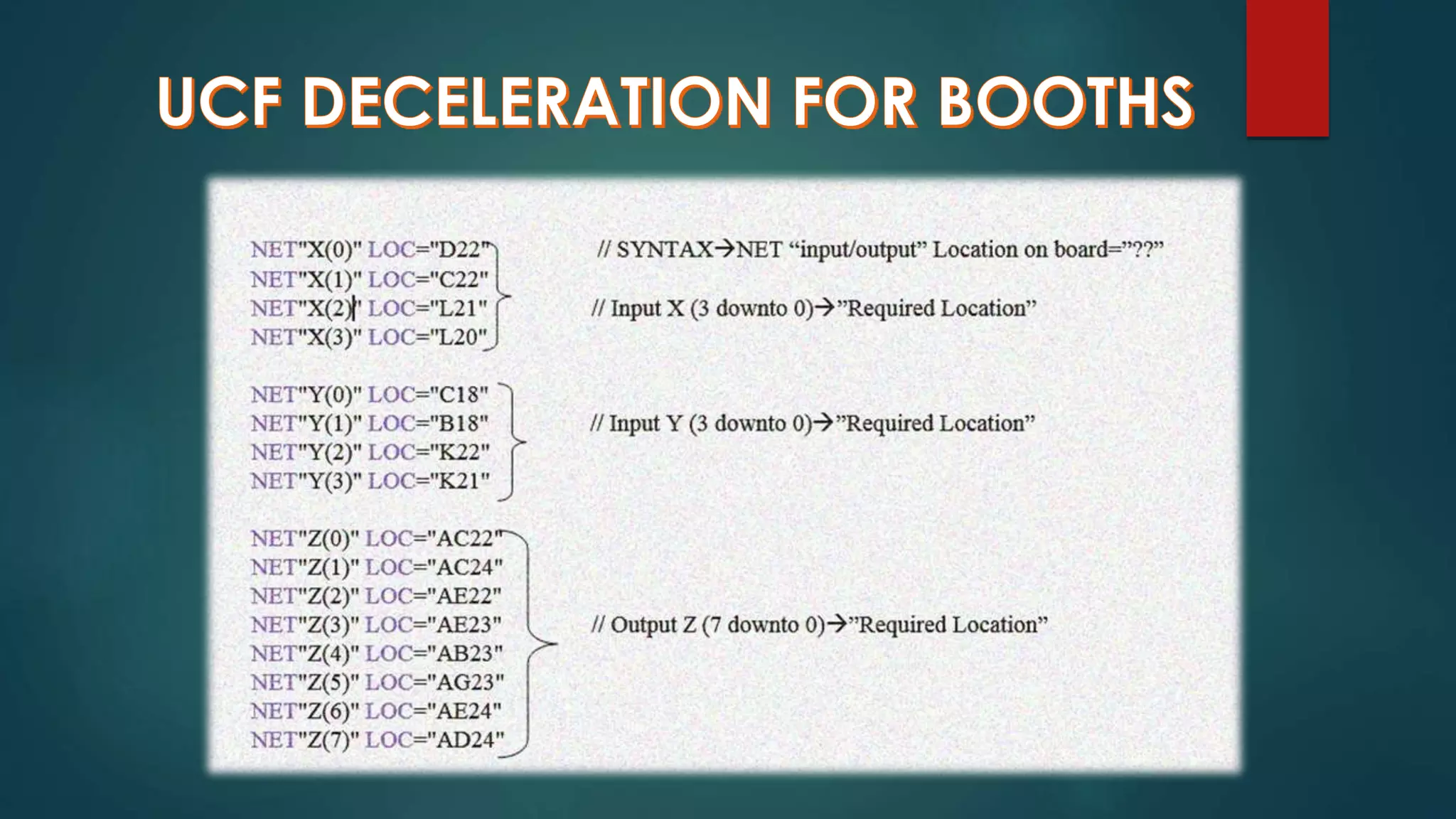

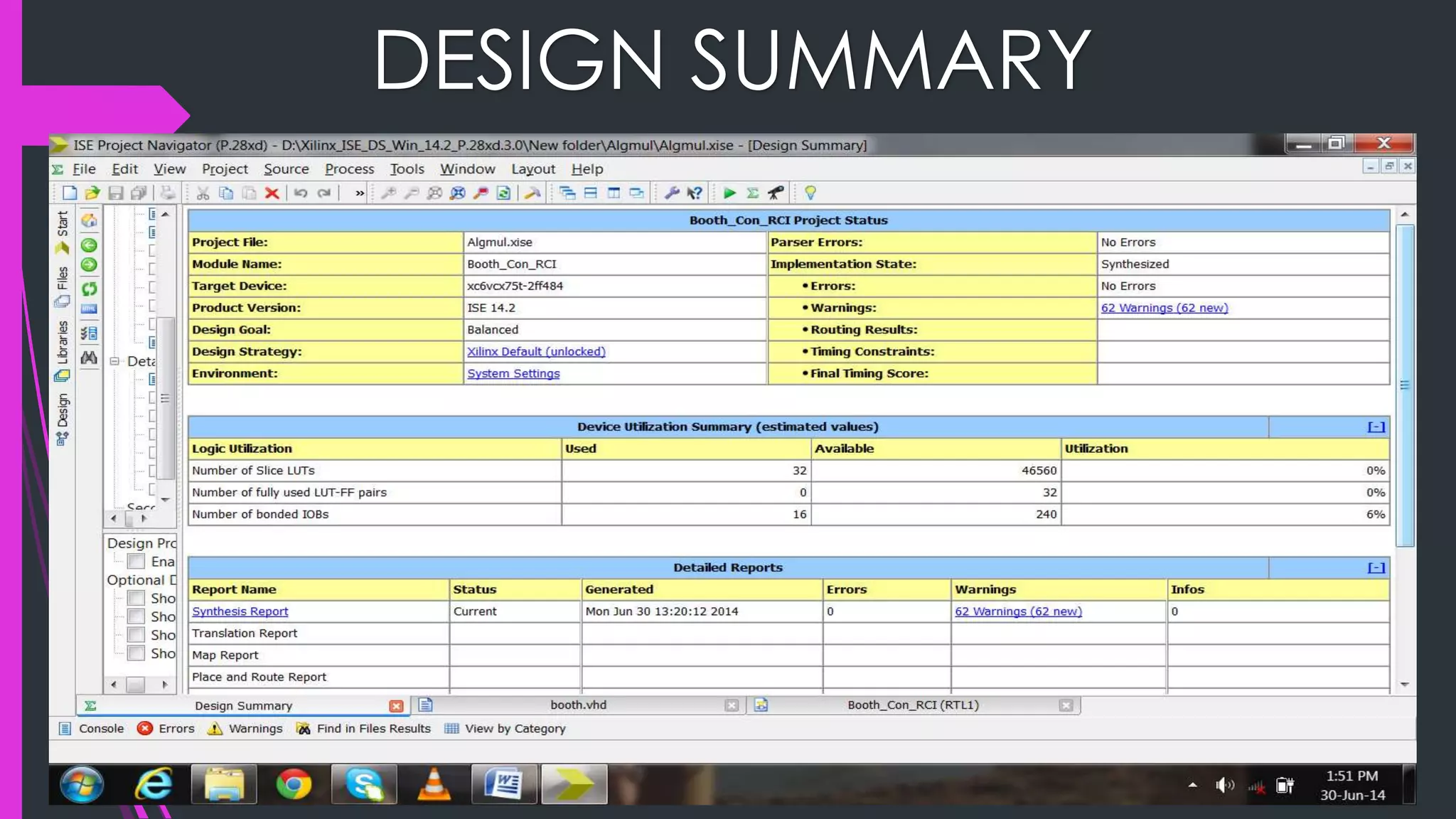

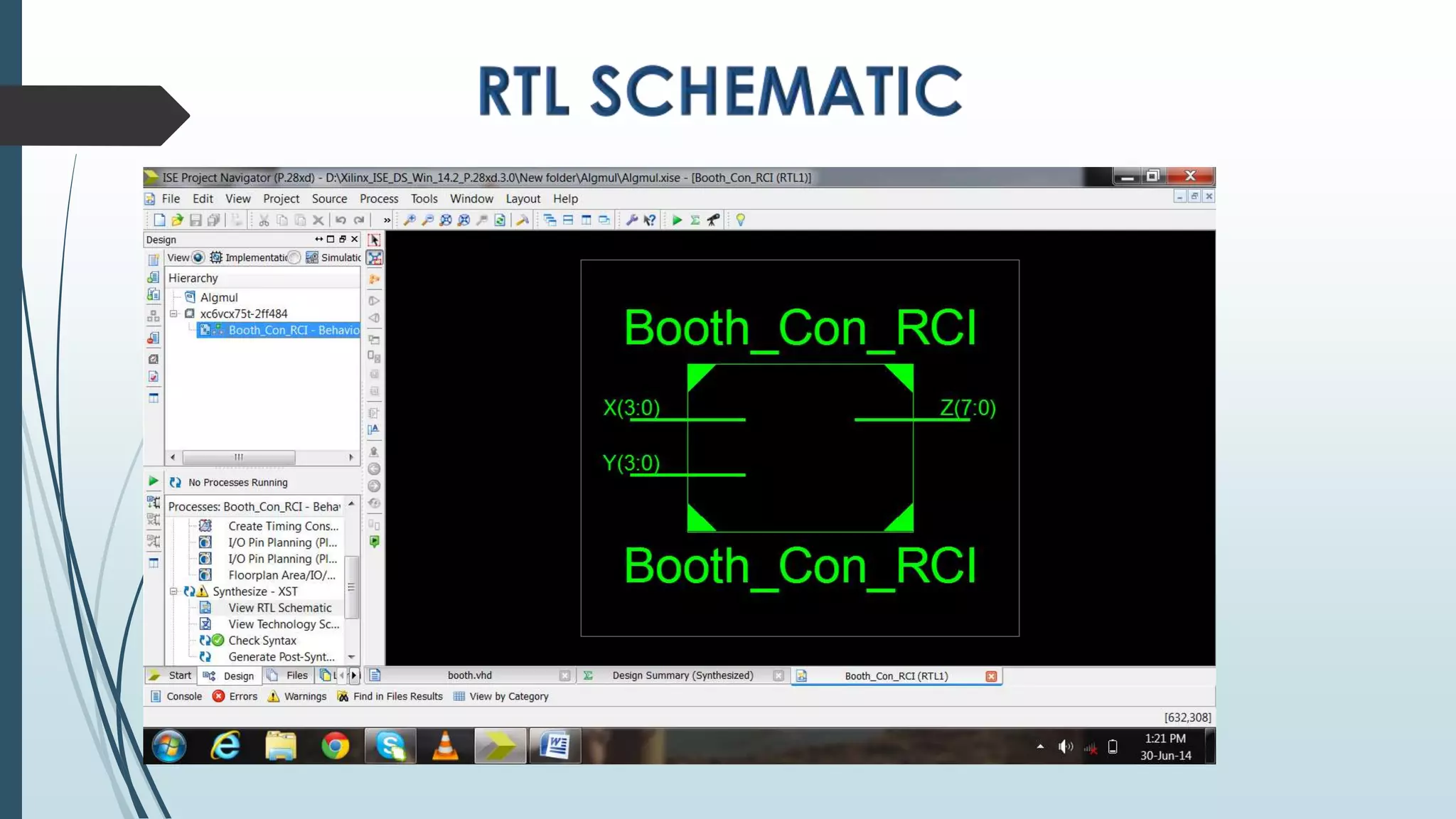

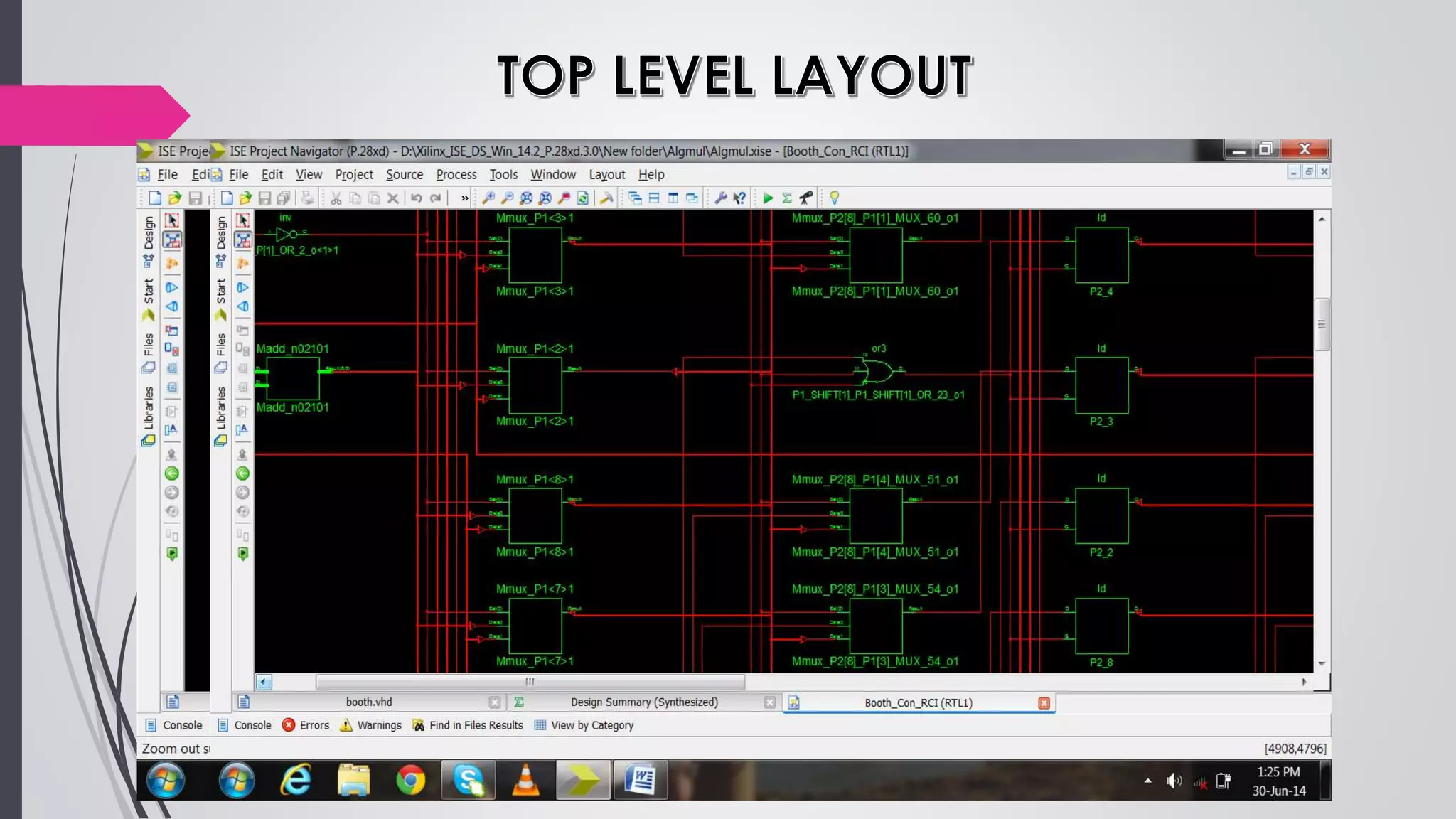

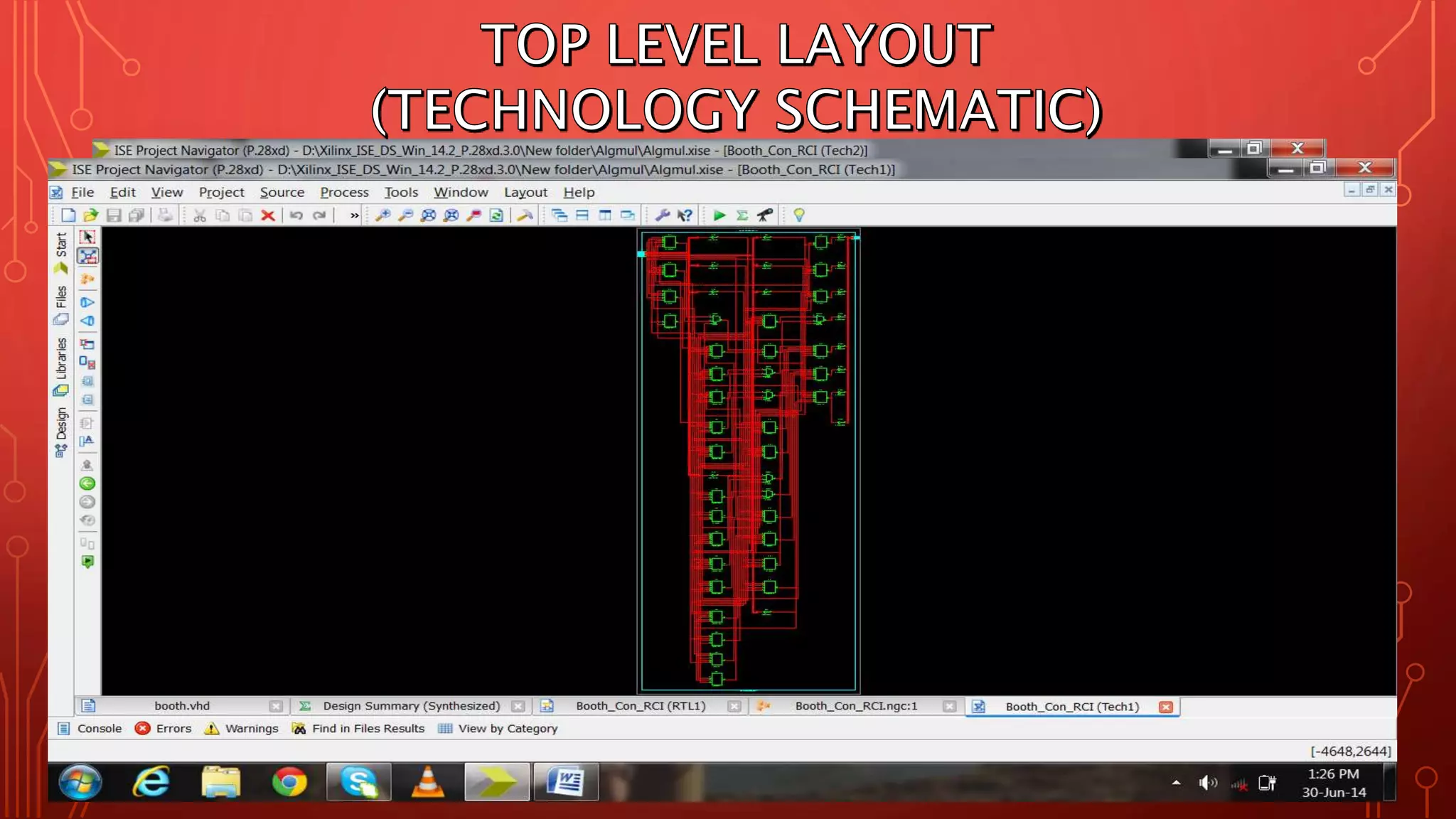

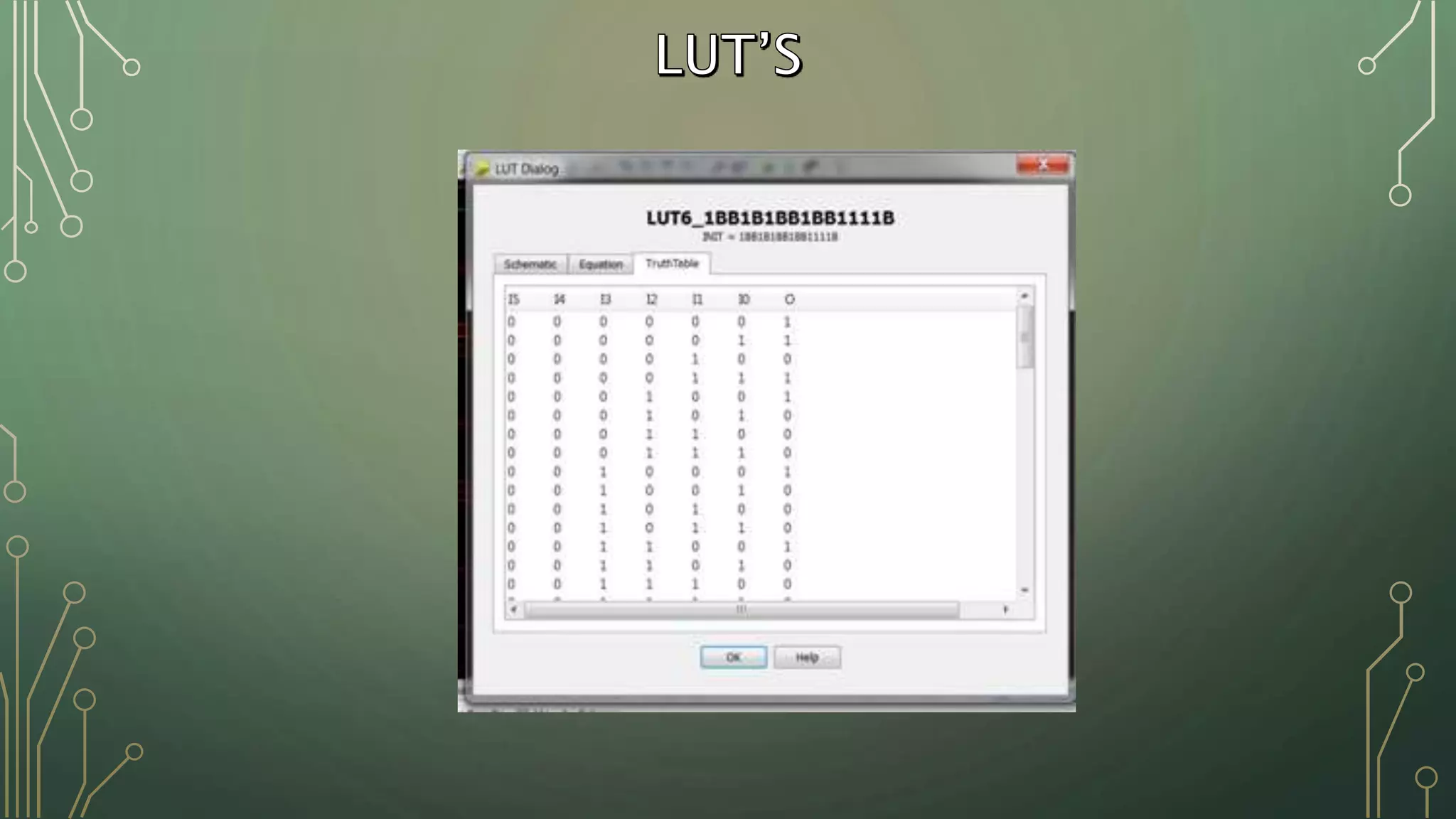

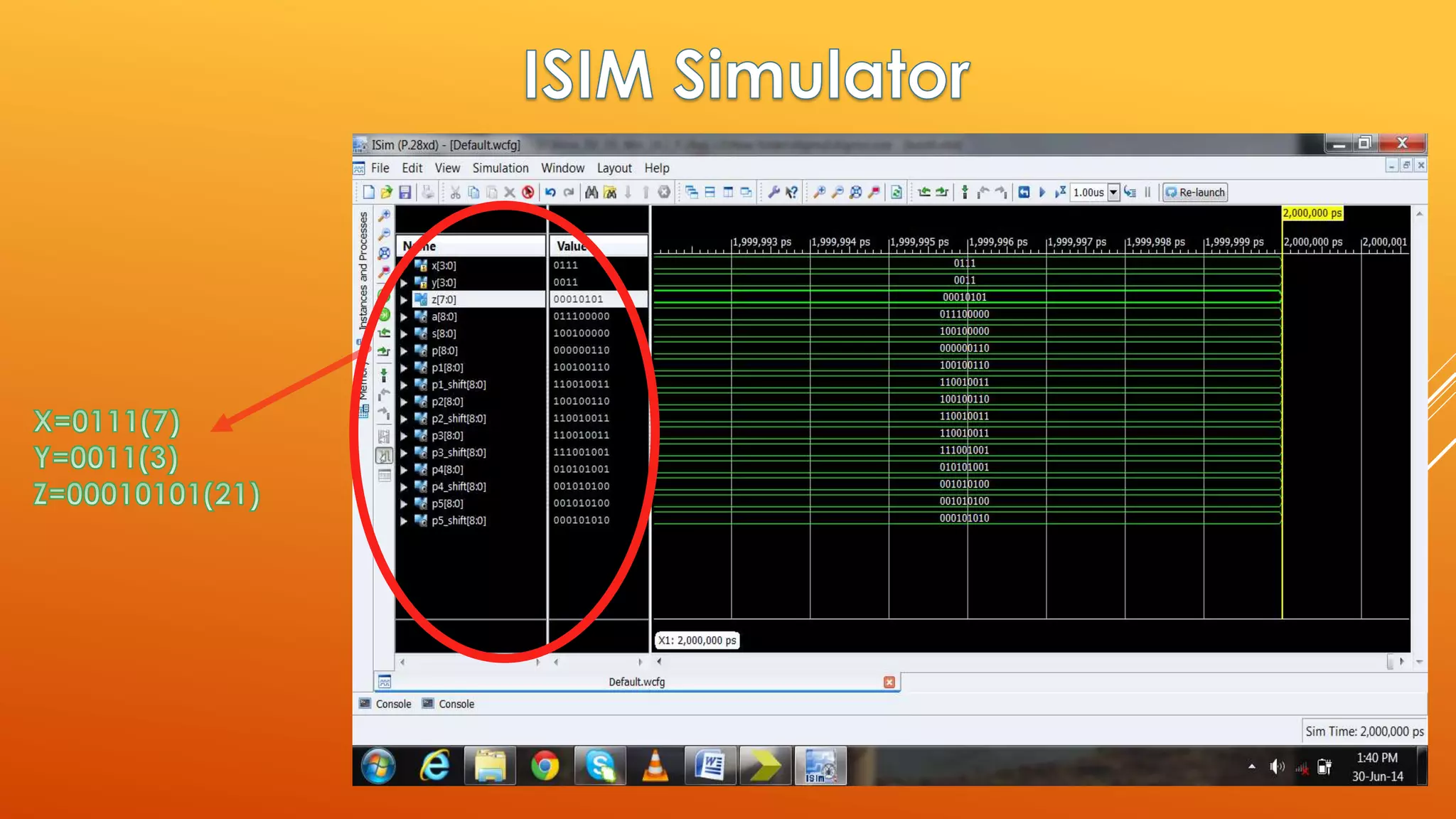

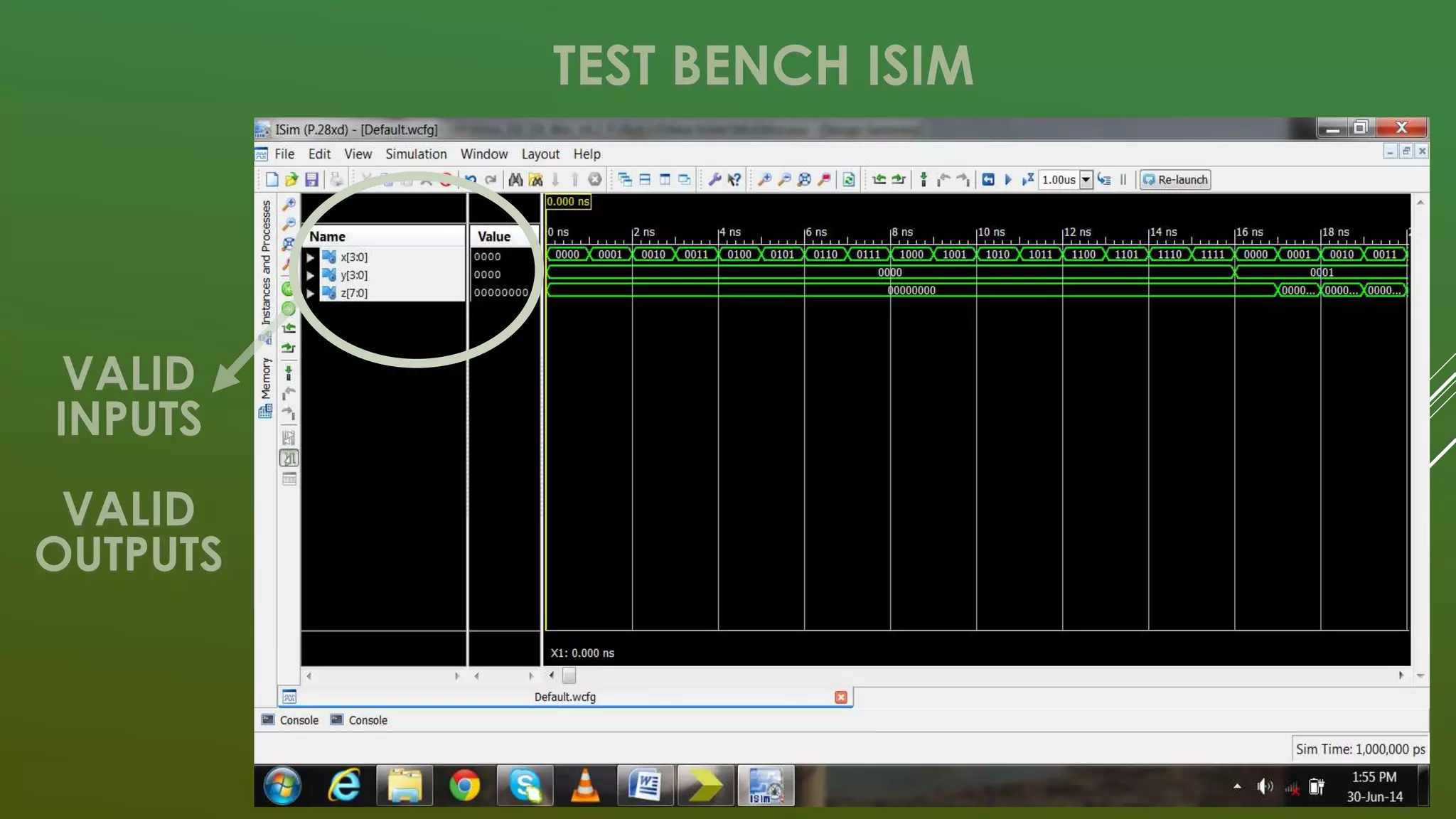

This document serves as an internal guide on the digital multiplier, focusing on the implementation of Booth's algorithm for signed-number multiplication using VHDL. It outlines the algorithm's functionality, types of multipliers, and the significance of multipliers in high-performance systems, as well as the simulation process on FPGA. The thesis concludes that Booth's radix-4 method offers advantages in speed and complexity compared to other methods, emphasizing further optimization opportunities in design efficiency.