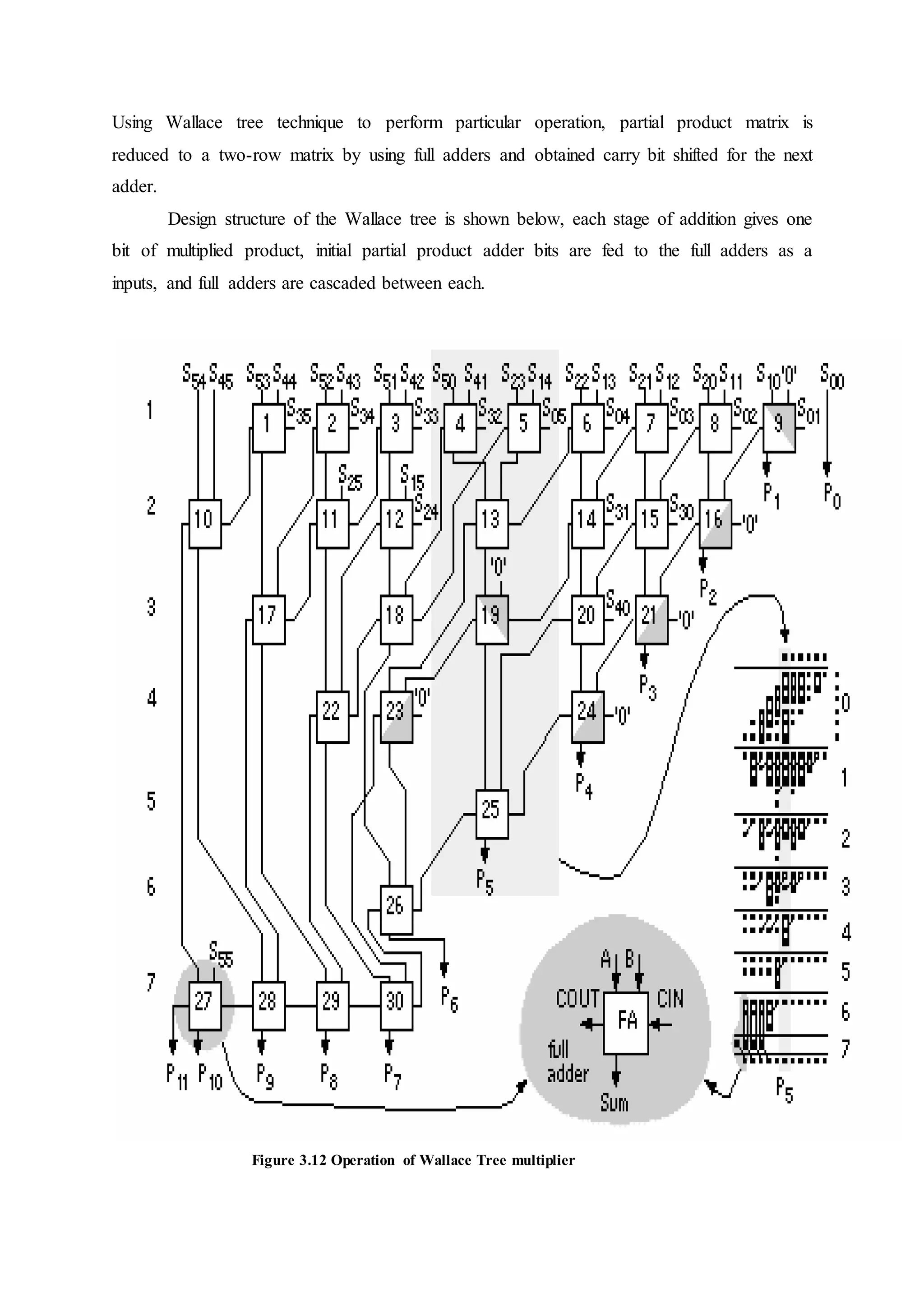

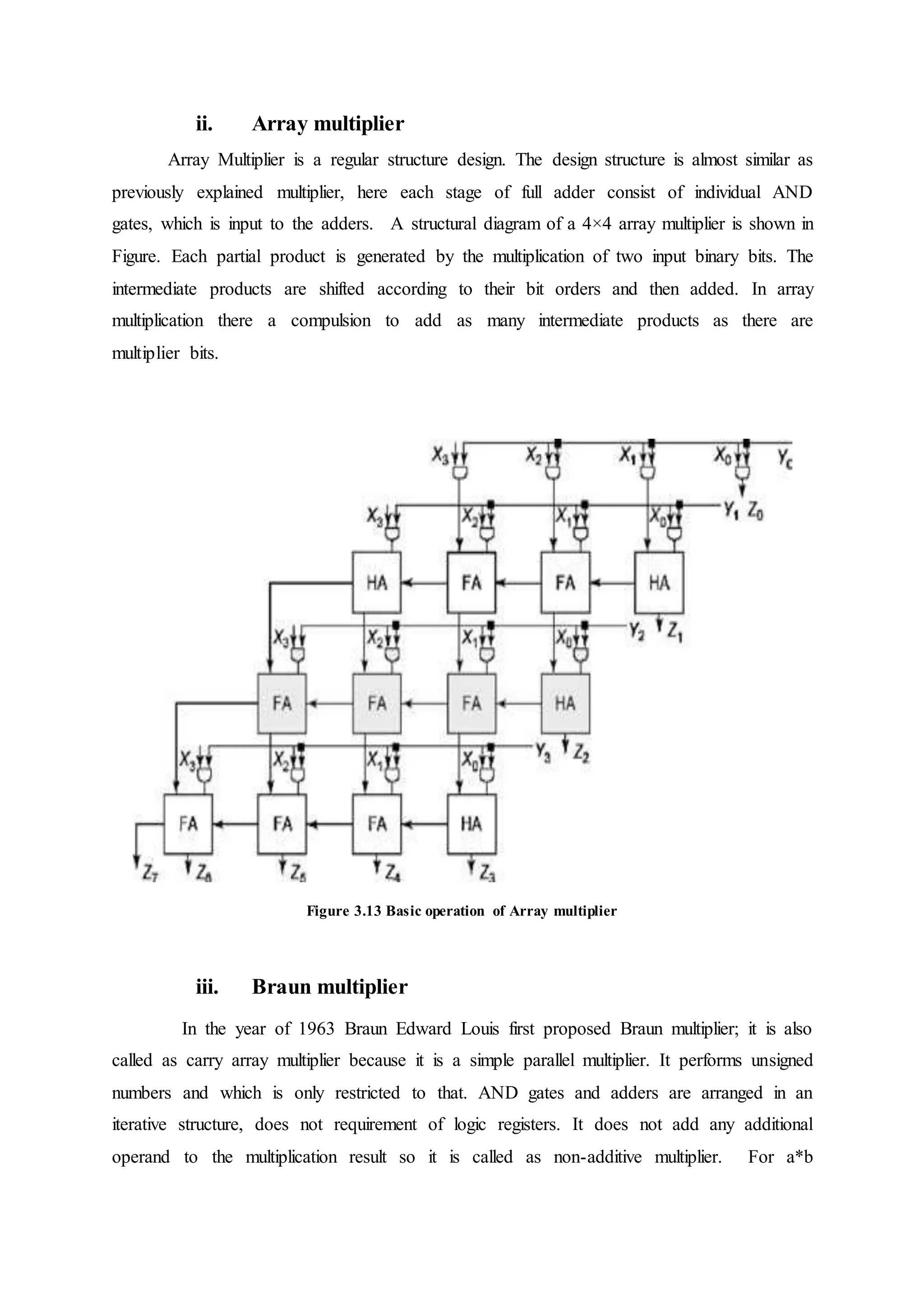

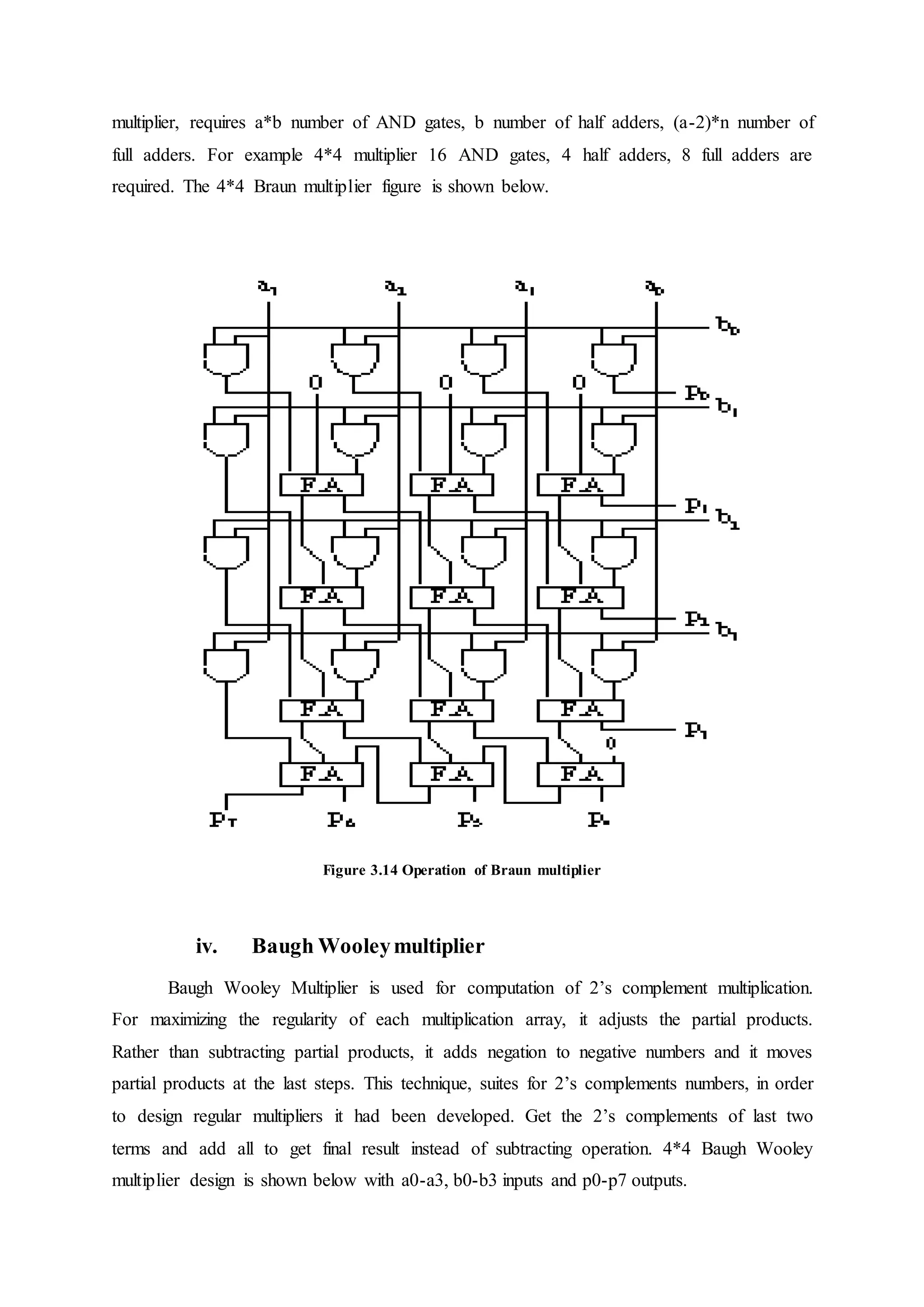

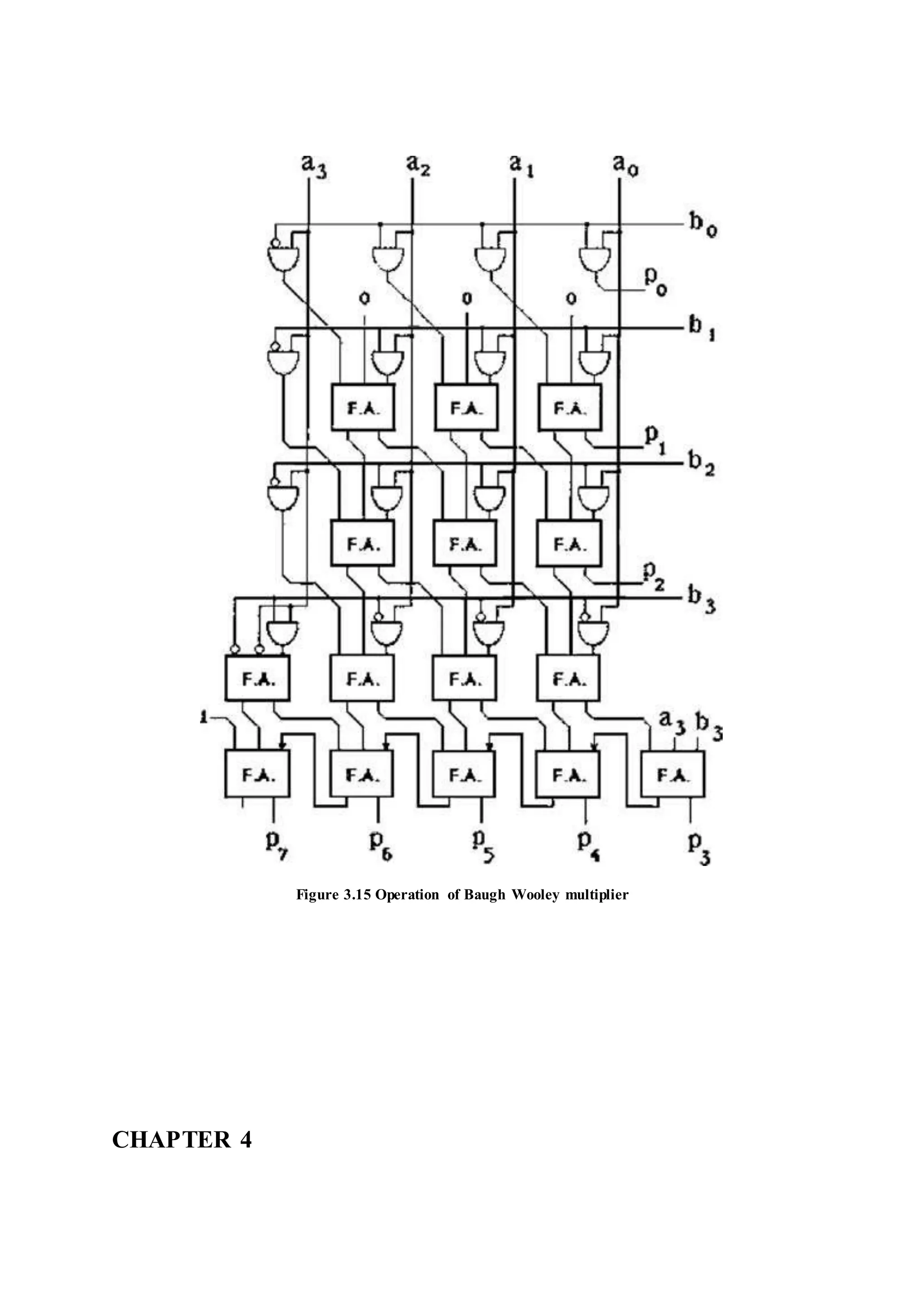

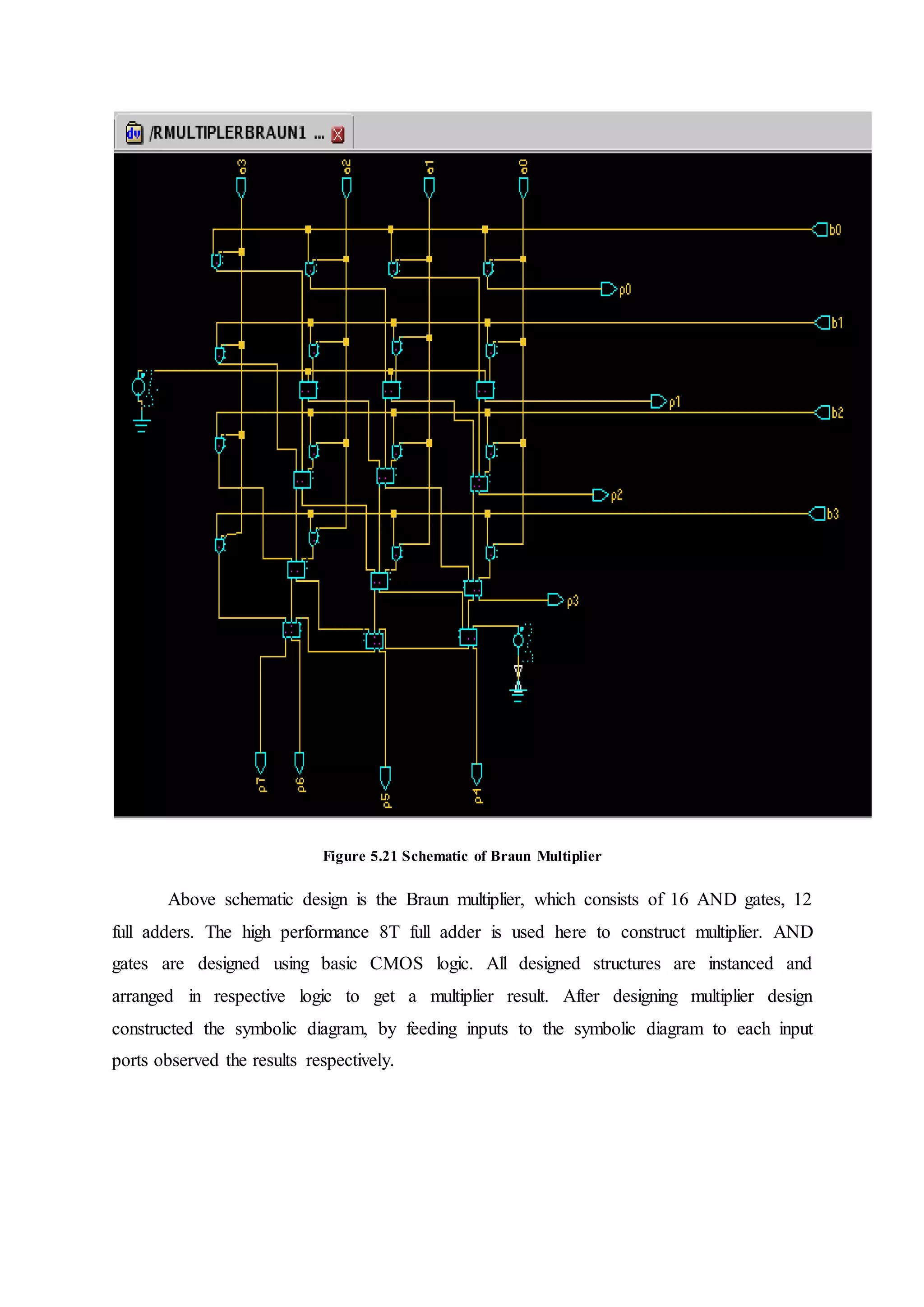

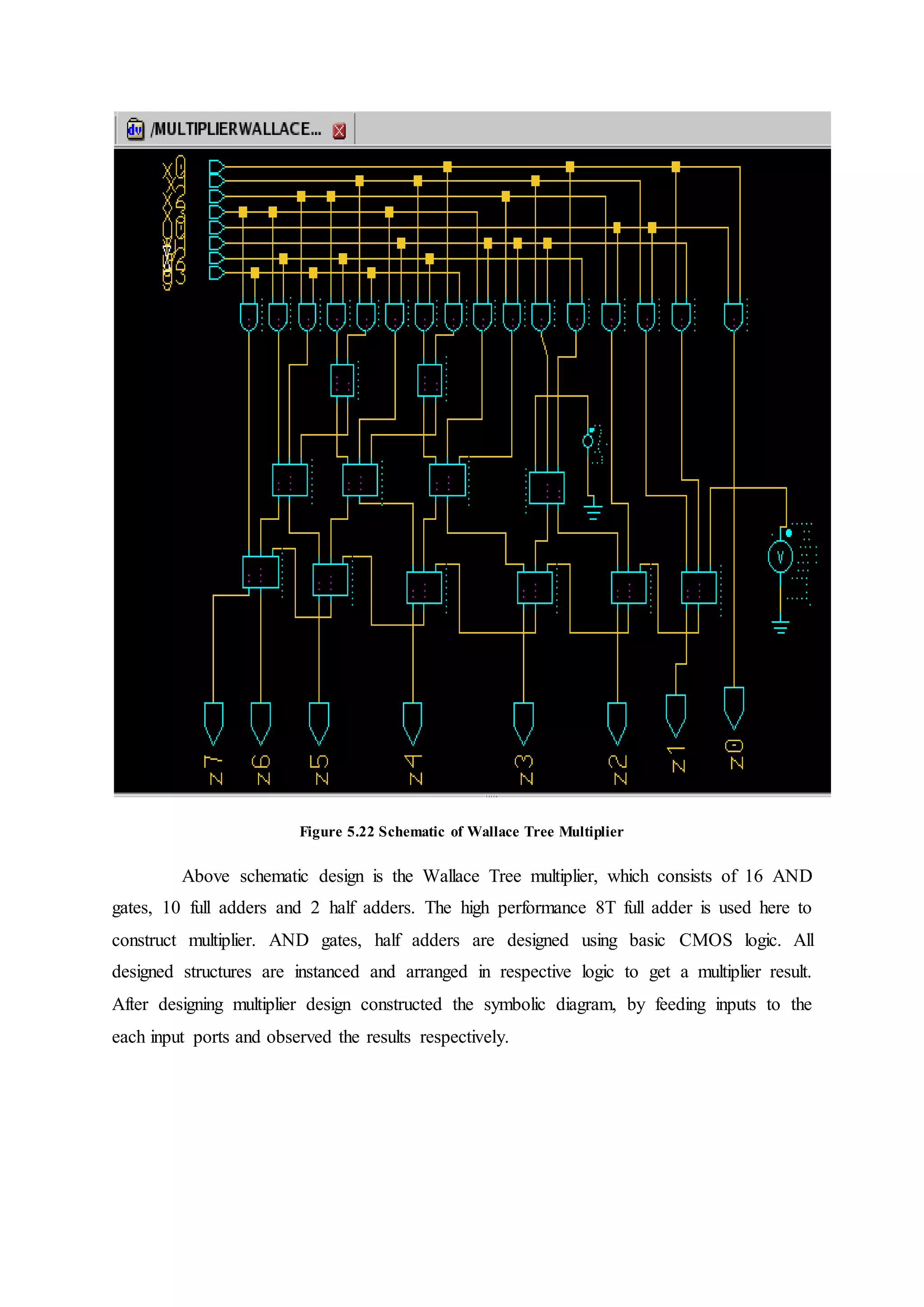

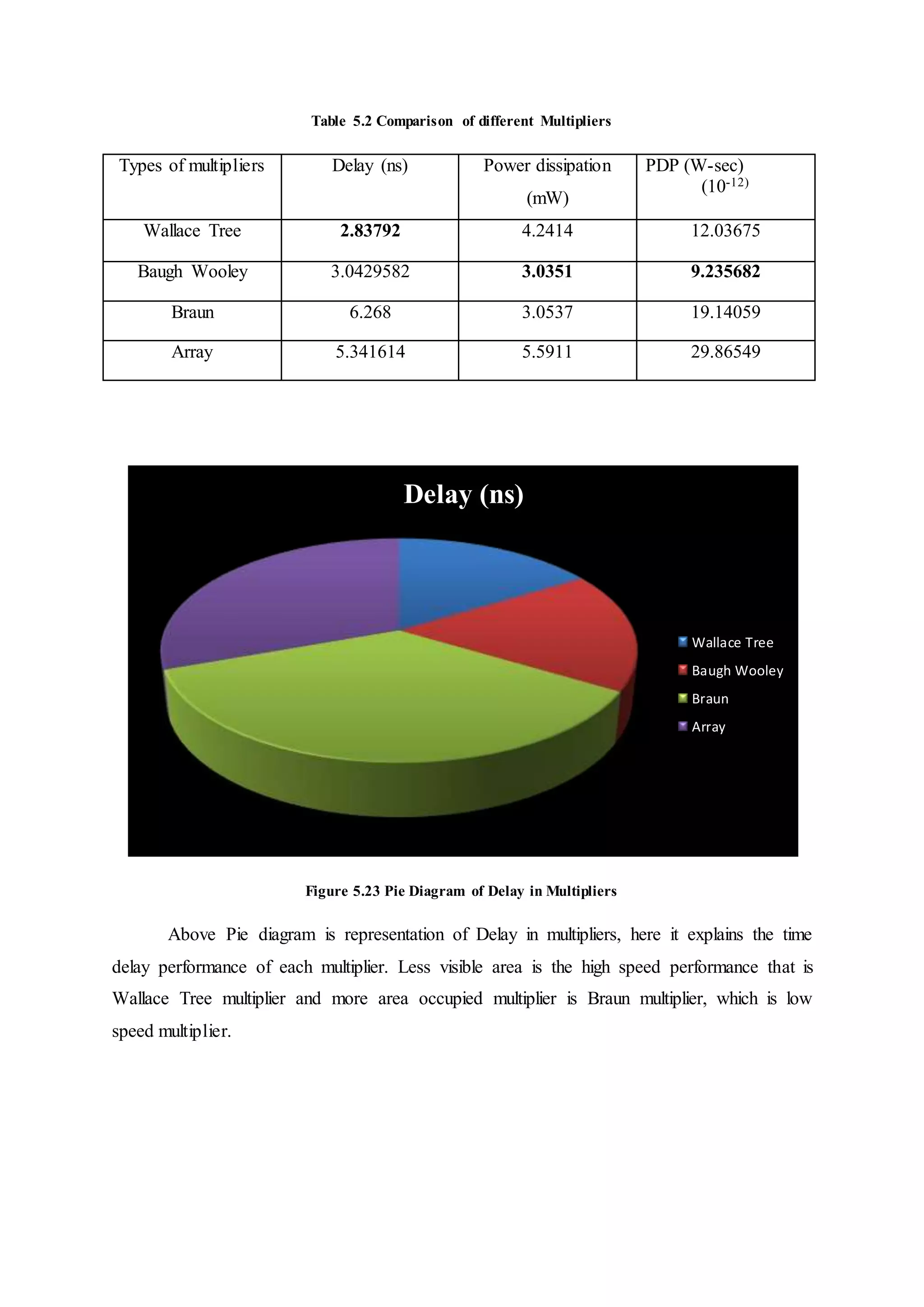

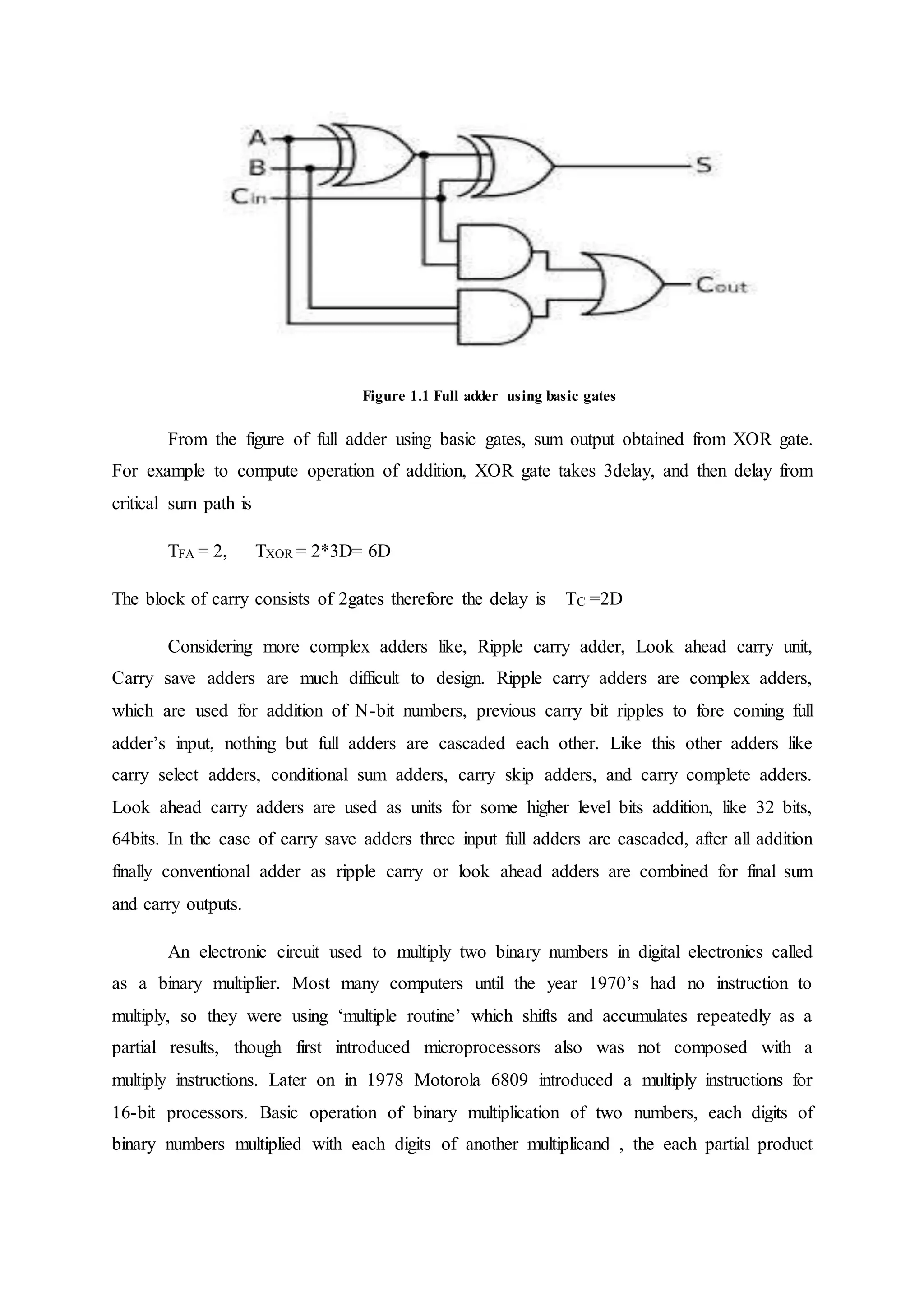

This document discusses the performance analysis of different CMOS full adder circuits and the VLSI design of a multiplier using Mentor Graphics. It analyzes the performance of various full adder circuits in terms of delay, power dissipation, and power-delay product. The high-performance 8T full adder is identified and used in the design of 4x4 multipliers like array, Braun, Baugh-Wooley, and Wallace tree multipliers. The multipliers are then analyzed and compared based on their complexity and performance.

![CHAPTER 2

LITERATURE SURVEY

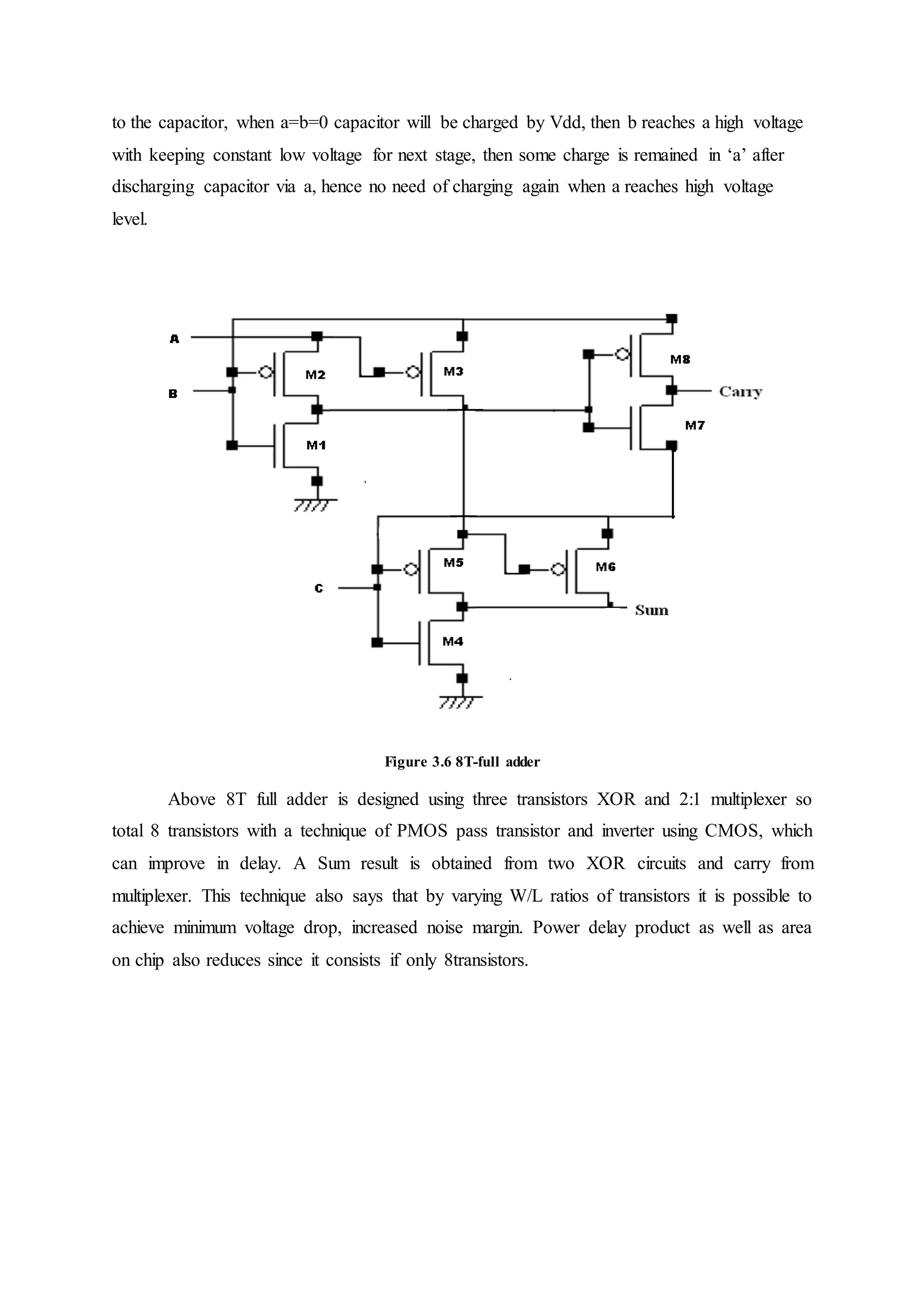

The work carried out by R. Dhayabarani, R. S. D. Wahida Banu, [1] proposes 8T

1bit full adder consists of six MOSFETS and multiplexer using two MOSFETs for reducing

the power consumption and delay. The proposed design and other designs like 14Trasistor

full adder, 20Transistor full adder, 28Transistor full adder, Conventional full adder, and

Transmission gate full adder are analysed via HSPICE simulations with 0.18um technology

and 1.2V supply voltage. Then high speed proposed full adder was considered to design

Wallace tree multiplier, Array multiplier, Braun multiplier, Baugh Wooley multiplier. Author

said that, Wallace tree multiplier a viable to efficient design for Digital FIR filter.

The work carried out by Deepak Garg, Mayank Kumar Rai,[2] proposed the

implementation of full adder 3T XOR and 2-to-1 multiplexer modules were used and with

total 8Transistors. Proposed full adder was compared against 10T full adder, 12T full adder,

16T full adder, 28T full adder. Here results are simulated through TANNER-EDA with 2.3

supply voltage based on 0.18um CMOS technology. An author said that, compared to other

full adders 8T adder successfully embeds the buffering circuit. 3T XOR based full adder

gives high speed, low voltage, and that lead to less energy consumption. As the transistor](https://image.slidesharecdn.com/d2275dad-5559-4ca3-8eb9-6a8e96203092-160120172530/75/Ramya-Project-4-2048.jpg)

![count is less it consumes less chip area, less cost of manufacturing, that was done via

designing and simulating the layout.

The work carried out by Deepali Sandhu, Sudhir Singh, Satwinder Singh [3]

presents the comparative work of low voltage, high speed full adder circuits. Here hybrid

design full adder approach combined in a single unit, and adder is designed using XOR-

XNOR. Also discussed conventional full adder combined with MOSCAP is called hybrid

design. This technique helps to reduce propagation delay, power consumption, and area of the

chip design. Simulation results in terms of delay, power, power delay product (PDP) are

compared against conventional CMOS, TG, and hybrid adder circuits.

Shipra Mishra, Shelendra Singh Tomar, Shyam Akashe, in “Design low power

10T full adder using process and circuit technique” [4] proposed 10T full adder analysed for

minimizing the leakage current, leakage power and boost up the speed. This analysis carried

out in different process and circuit techniques. To minimize the leakage power, minimum

transistors were used, and made variation in transistor dimension for reducing leakage

current. These simulations carried out through Cadence environment virtuoso tool with a

0.45um technology and for different supply voltages. This also expresses that, design lines

need to select suitable to required design features. On implementing on deep sub micron

method CMOS leakage current reduced at the process level. Most of the power consumption

decreased at the circuit level by constructing designs using less number of MOSFETs.

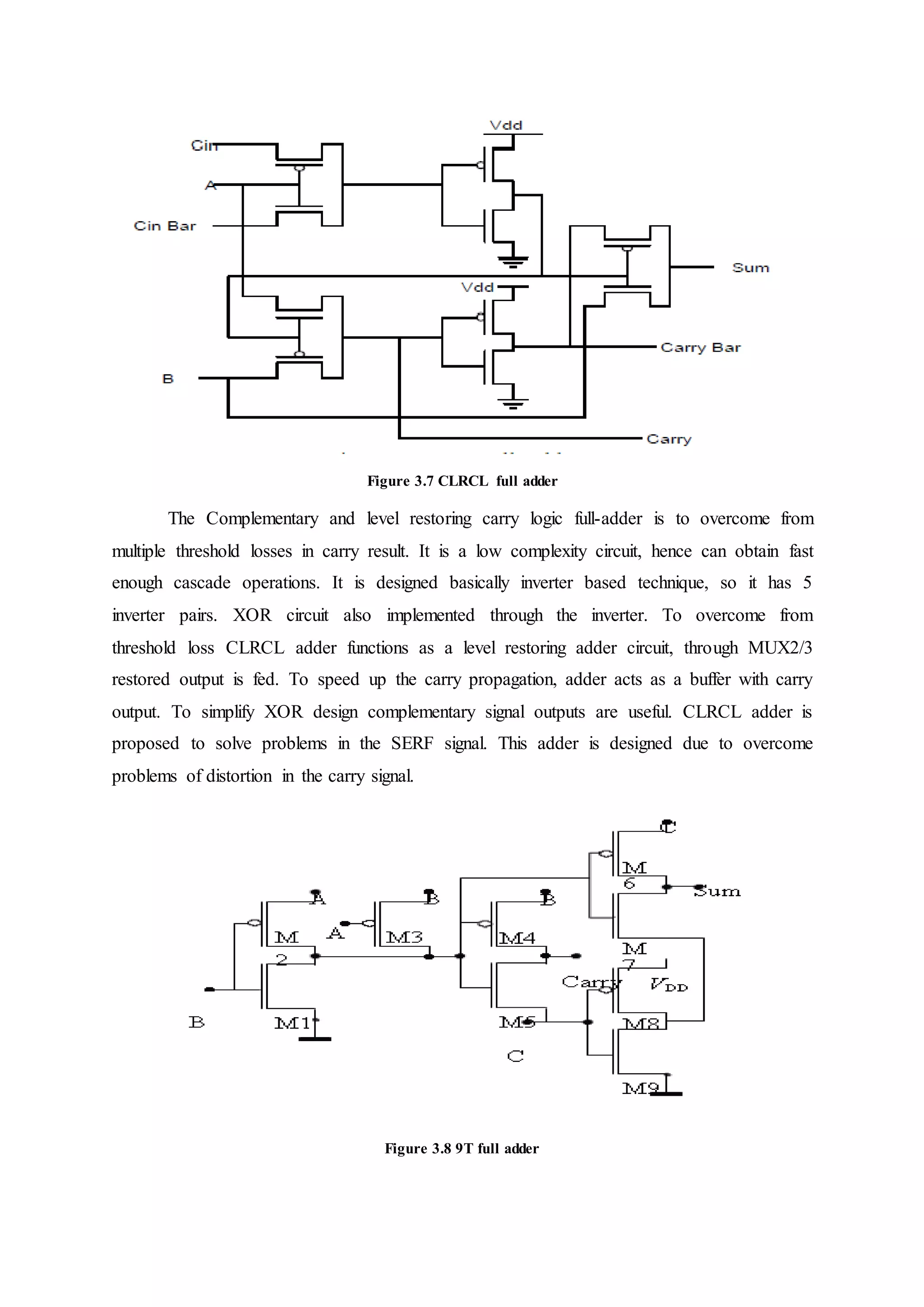

K. Nehru, A. Shanmugam, S. Vadivel in “CLRCL full adder based low power

multiplier architectures” [5] this power consumption, speed and area are the major concern.

The introducing CLRCL (complementary and level restoring carry logic) adder performance

analysed from designing multipliers using full adder. Here Braun multiplier, Array multiplier

and Baugh Wooley multiplier is designed using CLRCL full adder. As we all know designing

an efficient circuit is challenge in VLSI design stream. All multipliers were simulated for 4

bit data, verified results on a Tanner EDA tool with 250nm technology. Conventional based

multipliers are less performed than CLRCL based multipliers and exhibits better area on chip.

Among designed and simulated multipliers, array multiplier gives better performance of

power consumption compared with Braun and Baugh Wooley.

Dhireesha Kudithipudi and Eugene John in this, [6] compared parameters such as

power, delay and power delay product of multipliers. Here four different designs of digital](https://image.slidesharecdn.com/d2275dad-5559-4ca3-8eb9-6a8e96203092-160120172530/75/Ramya-Project-5-2048.jpg)

![Multipliers are constructed using 10T full adder, SERF full adder, 28T full adder. Multiplier

constructed using 28T full adder given the significant response on 180nm technology, but not

on 70nm. Using SERF designed multiplier resulted less power consumption than 10T full

adder used multiplier. Regarding propagation delay 10T full adder used multiplier established

better than others. Designed multipliers were Carry save multiplier, Bit array multiplier,

Wallace multiplier, Baugh Wooley multiplier, among these Carry save multiplier had better

PDP than other multipliers, and this demonstrated using 2*2, 4*4, and 8*8 bits to all

multipliers, and also said that, at the final stage of multiplication by incorporating hybrid

adder module forms critical path delay and high static leakage current zone.

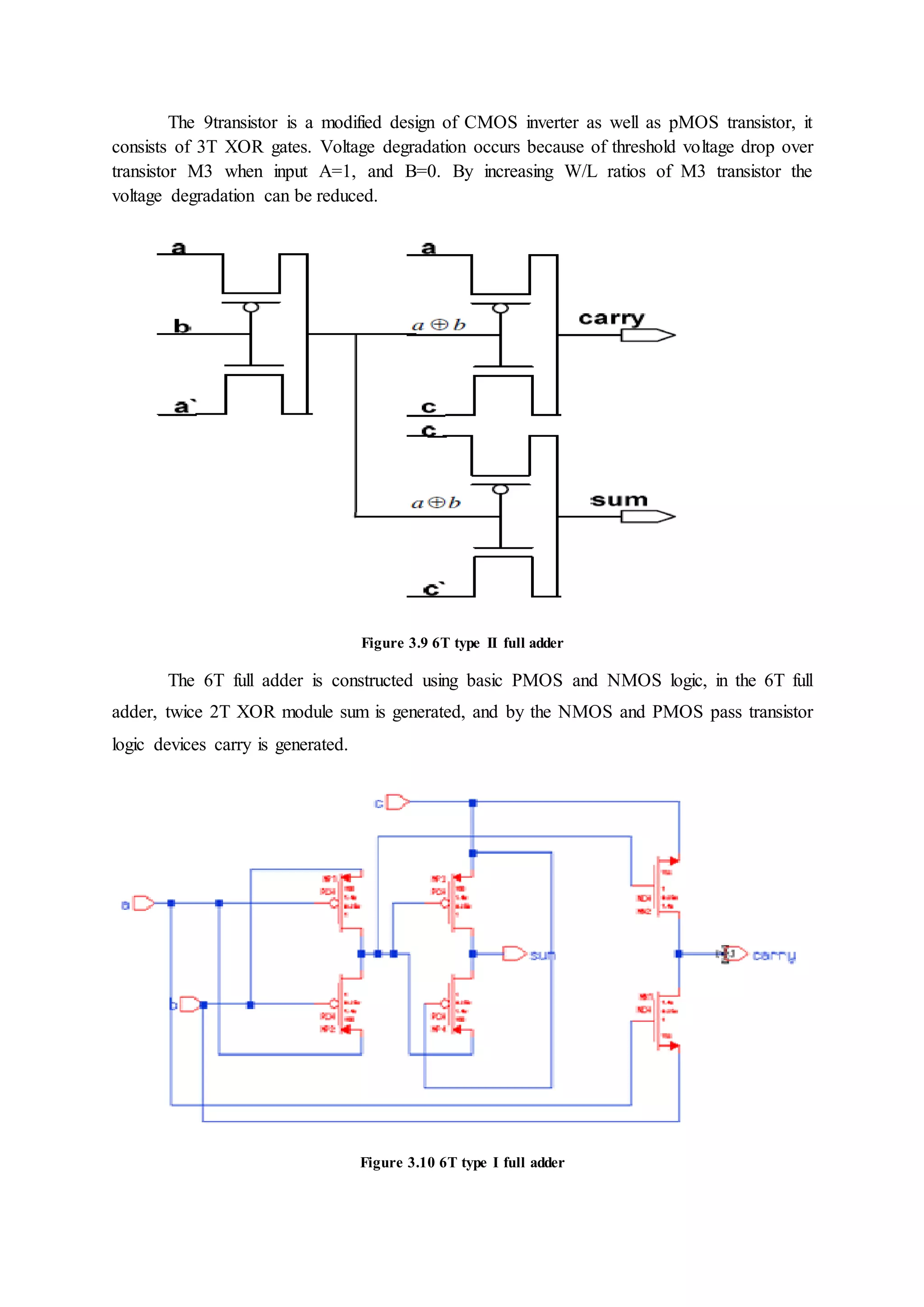

The authors, Saradindu Panda1, A. Banerjee, B. Maji, Dr. A. K.

Mukhopadhyay,[7] proposes the research on evolution of full adder to achieve high

performed full adder in all important parameters. Starting from conventional 28T CMOS full

adder, 20T transmission gate full adder, 14T full adder, 10T static energy recovery full adder,

10T realised using GDI (gate diffusion input), 9TA, and 9T B full adder, at last 8T full adder.

Above all the adders have advantages and disadvantages with their respect. GDI based adder

performed better but fabrication of MOSFET are cost effective, fabrication process is twin

well CMOS SOI (silicon on chip). TG (transmission gate) based adders showed low average

delay, but 14T full adder had low power delay product. So they thought that, 8T full adder

was the best option for optimization of power and delay.

The work carried out by Prof. S. Murugeswari, Dr. S. Kaja Mohideenn [8]

presents that, Wallace tree multiplier and truncated multiplier was constructed by carry save

adder and that was demonstrated. Further author had replaced proposed carry save adder

with a modified carry save adder (MCSA) and implemented using multiplexer. Multiplexer

based full adder was used instead of regular full adder in truncated multiplexer. 8 x 8

Multiplier had simulated on Model sim 6.3c and on Xilinx10.1 had carried out. The proposed

multiplexer based multiplier had reduced 25% of area and 10% of power reduction than

existing system these all carried out on Xilinx Spartan 3 XC3S50 FPGA. Hence truncated

multiplier with MUX based full adder would be the less power dissipated and less chip area

occupied.

Saravanan R, Kalaiyarasi M, S. Jim Hawkinson, D Sathya, [9] this presented in

order to achieve high speed, low power dissipation, and power delay product various](https://image.slidesharecdn.com/d2275dad-5559-4ca3-8eb9-6a8e96203092-160120172530/75/Ramya-Project-6-2048.jpg)

![technique style had used, those were hybrid CMOS logic style to decrease PDP, Gate

diffusion input (GDI) logic styles, and alternative internal logic styles. Author also presented

full voltage swing along with high speed, low power dissipation. There was an evolution in

full adder parameters by conducting different experiments from different designs. Initial

design was the hybrid logic style, later constructed by utilizing GDI based full adder, and

GDI technique also eradicated from construction of full adder with XOR/XNOR. This

approach provided the high speed, very low power, and voltage swing. This work was

compared with the other full adder in 1-bit, 2-bit, 4-bit, 8-bit and 16-bit structures and this

technique was better. All designs were simulated in 180nm technology on Mentor Graphics

tool and results analyzed in test bench forms.

Shahebaj Khan, Sandeep Kakde , Yogesh Suryawanshi, [10] in digital signal

processors, FIR filters and microprocessors multipliers are the weighty blocks. As the

research was keep on going about optimizing area and increasing speed of multipliers, so

they were resulted as high speed with the large area. Here author had proposed solution for

that; by introducing reduced complexity Wallace Tree (RCWT) form previous Wallace Tree

multiplier, it also required a high efficient full adder. RCWT had less number of adders than

previous, at final stage of multiplier connected with a carry propagating adder hence both

gave save time delay. Then RCWT was constructed using energy efficient CMOS full adder.

As a result power, area and speed were improved. Thus the proposed method of multiplier

reduced total 70-80% of half adders count than standard Wallace Tree multiplier.

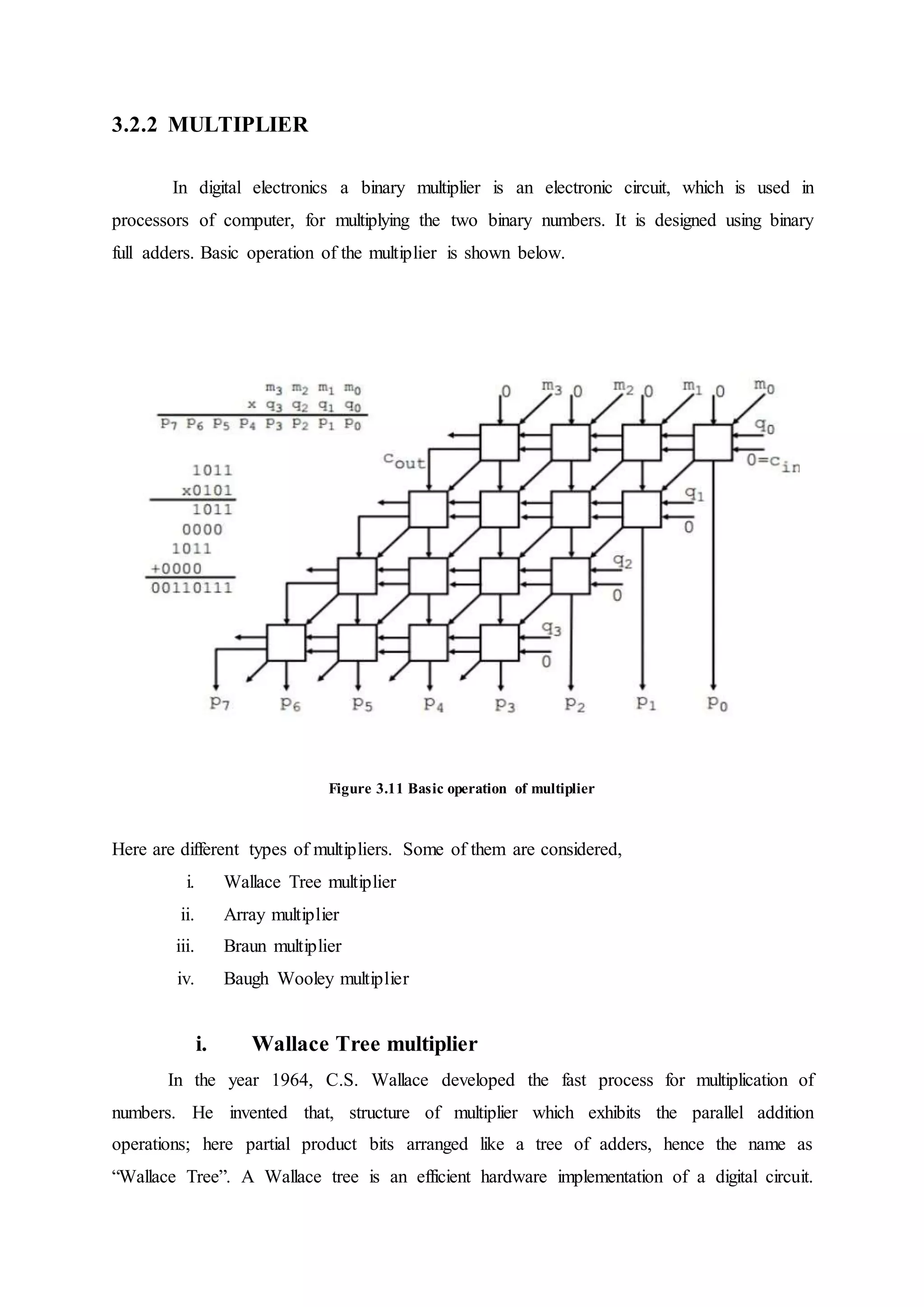

Karthik Reddy. G [11] in integrated circuits power consumption is the major

concerns and in leakage power is the major concept. ALU containing major roles of full

adder, by lowering the power consumption of full adder, power consumption of ALU would

be reduced and lowering power consumption ALU processors power consumption could also

reduce. Here the author proposed that designing low power and less transistor count full

adder on cadence tool and virtuoso platform with 180nm n-well CMOS technology by

supplying voltage 1.8V and frequency 100MHz. New designed 6T full adder saved 93.1% of

power, compared to 28T adder, SERF by 80.2%. It also highly performed than pass transistor

and GDI techniques.](https://image.slidesharecdn.com/d2275dad-5559-4ca3-8eb9-6a8e96203092-160120172530/75/Ramya-Project-7-2048.jpg)

![The work carried out by P.V. Rao, Cyril Prasanna Raj P, S. Ravi, [12] proposes

that, now a days in digital signal processing high clock frequencies and low power multipliers

are very important. Here author proposed the performance analysis of array multipliers,

Baugh Wooley multipliers and Wallace Tree multipliers. Physical verifications and

functionality checking were carried out on HSPICE. On Cadence Virtuoso layouts were

designed, DRC and LVS rules were verified using Hercules I. Multipliers should be selected

with respect to the application and performance based. Wallace Tree multiplier exhibited

least power and delay and less area in array multiplier.

CHAPTER 3

IMPLEMENTATION

3.1 INTRODUCTION

Adders are the fundamental building blocks for designing of any VLSI system

architectures; in this project three inputs and two outputs full adders are considered. A group

of full adders are analyzed according to their performance in terms of time delay, power

dissipation, power delay product (PDP) and power consumption. Time delay is that,

minimum period of time to drive output from the input, power dissipation is the loss of power

in the circuit to drive the output, and total power used by the circuit to perform the operation

is power consumption. Among those considered adders, high performed full adder that is

high speed, less power loss and less power consumed adder will be used in higher designs.

The high performed full adder is used for the design of multipliers.

Here group of full adders are taken for analysing the performance. In that some

special type of full adders are considered like CLRCL (complementary and level restoring

carry logic), SERF (static energy recovery full adder), GDI (gate diffusion input) based full

adders, and other adders are GDI_XOR full adder, GDI_XNOR full adder, full adder 9TA,

full adder 9TB, 8T full adder, 9T full adder, 6T full adder type I, 6T full adder type II are

analyzed.

All ten different full adders are designed using various numbers of MOSFETs. These

full adders are analyzed using Mentor Graphics tool with 180nm technology. The simulated

results are observed and found the high speed, less power dissipated, less PDP and less power](https://image.slidesharecdn.com/d2275dad-5559-4ca3-8eb9-6a8e96203092-160120172530/75/Ramya-Project-8-2048.jpg)