1) The ALU performs arithmetic operations like addition, subtraction, multiplication and division on fixed point and floating point numbers. Fixed point uses integers while floating point uses a sign, mantissa, and exponent.

2) Binary numbers are added using half adders and full adders which are logic circuits that implement addition using truth tables and K-maps. Subtraction is done using 1's or 2's complement representations.

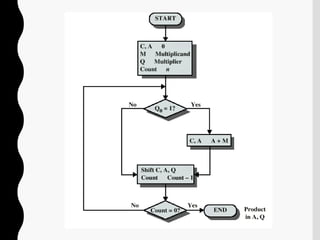

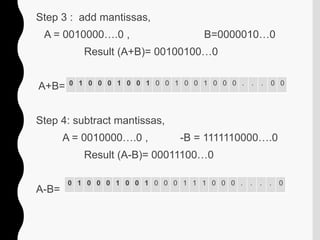

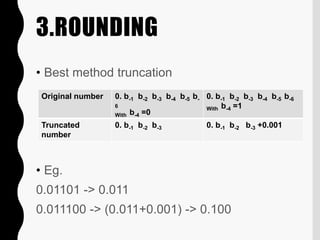

3) Multiplication is done using sequential or Booth's algorithm approaches while division uses restoring or non-restoring algorithms. Floating point uses similar addition and subtraction steps but first normalizes the exponents.